# EMC modeling of Integrated Circuits using IC-EMC

Etienne Sicard, Alexandre Boyer

# ▶ To cite this version:

Etienne Sicard, Alexandre Boyer. EMC modeling of Integrated Circuits using IC-EMC. 10th International Workshop on the Electromagnetic Compatibility of Integrated Circuits (EMC Compo 2015), Nov 2015, Edimburgh, United Kingdom. 2p. hal-01225370

HAL Id: hal-01225370

https://hal.science/hal-01225370

Submitted on 6 Nov 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# EMC modeling of Integrated Circuits using IC-EMC

#### Etienne SICARD

Dept of Electrical & Computer Engineering INSA, University of Toulouse France

Etienne.sicard@insa-toulouse.fr www.ic-emc.org

Abstract — The freeware IC-EMC is a windows-based software demonstrator which aims at simulating parasitic emission and susceptibility of integrated circuits. The demonstration proposed at EMC Compo 2015 illustrates the main features of the tool and recent IC case studies analyzed with IC-EMC, including a DSPIC processor, a Package-on-Package, and a Ethernet transceiver.

Keywords: EMC, Integrated circuits, parasitic emission, susceptibility, standards, IEC, IBIS, modeling

#### I. Introduction

The knowledge in integrated circuit design for electromagnetic compliance has risen rapidly over the past recent years, thanks to focused books [1-3], dedicated workshops [4] and IC-specific sessions in major EMC conferences such as APEMC [5]. At the interface between IC designers and vendors, the tool IC-EMC has been developed and made available to the EMC community [6] to ease exchanges of models and comparison with measurements, with several case studies [7] based on cooperative research with industry and dedicated training [8].

### II. SOFTWARE STRUCTURE

# A. EMC of ICs in practice

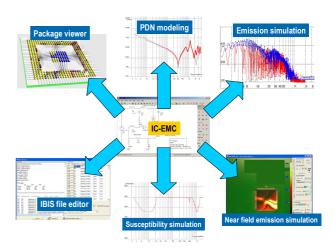

The tool IC-EMC includes a conventional schematic editor, (See Fig. 1), a set of tools to help user to build EMC models, an interface to Spice for analog simulation, and a post-processor for easy comparison between measured and simulated parasitic emission and susceptibility.

A set of tools with significant added value for EMC analysis are gathered in the same environment:

- A 3D package viewer, based on the IBIS pin list and models, and simple geometrical parameters such as the die size, type of package, IO pitch, etc.

- A passive distribution network (PDN) viewer, which eases identification of basic trends in the Z(f) profile, and derive associate model

- An emission simulation environment targeted to the prediction of conducted and radiated noise as measured using IEC standard characterization methods [9]

#### Alexandre BOYER

Dept of Electrical & Computer Engineering INSA, University of Toulouse France

alexandre.boyer@insa-toulouse.fr

- A near-field estimator based on elementary current dipole radiation. Near-field simulation may be compared to measurement described in XML format [10] as specified by IEC.

- An immunity simulation environment dedicated to the prediction of conducted and radiated immunity as measured using IEC standard immunity characterization methods [11].

All proposed models and approaches are built in compliance with the generic modeling philosophy described in IEC standard model approach [12]. A library of common standard models and several case studies ease the EMC simulation, as may be find in the on-line user's manual [7].

Figure 1. The IC-EMC capabilities in terms of emission and immunity prediction

#### III. RECENT EVOLUTIONS

# A. Package-on-package

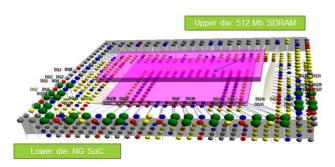

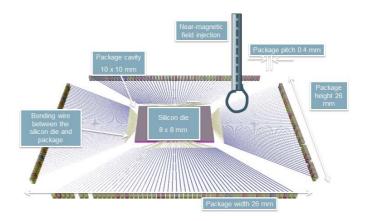

In cooperation with VALEO [13], the handling of Package-on-package and 3D ICs has been made available in IC-EMC. IBIS descriptions for up to 16 dies may be merged in order to reconstruct accurate 3D views of stacked structures, with associate power domain tracking and RLC-based parasitic element extraction (Fig. 2).

Figure 2. 3D view of the PoP analyzed by VALEO [13]

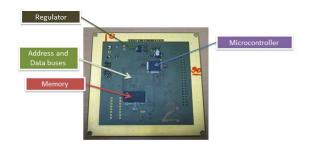

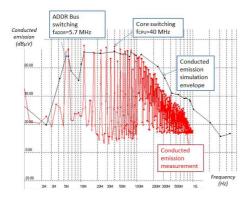

Figure 3. EMC test board for education [8] (top) and example of comparison between measured and simulated emission (bottom) [6]

# B. EMC board for education

Within the frame of a one-week training session including EMC measurements on ICs, we have reused a EMC research board designed by L. Guibert, Onera as part of his PhD [14] for educational purpose [8]. The case study proposed as a demonstration includes simple ICEM model construction [12] and matching with conducted measurements, as illustrated in Fig. 3 (1/150 $\Omega$  method [9]). The test board includes a DSPIC33F processor, a SRAM memory and a regulator.

# C. Immunity analysis of a transceiver

In cooperation with industry [15], we have investigated the immunity of a Ethernet Gigabit Switch using the Near-field immunity scan method [11][16].

Figure 4. Coupling of a magnetic loop used for near-field injection to the leads and bondings of a QFP package [15]

We propose to build a model of the sensitive parts based on the coupling of the near-magnetic probe to the package leads and bondings. The IBIS information of the driver and receiver is combined to the PDN and decoupling components to match NFSI measurements.

#### REFERENCES

- S. Ben Dhia, M. Ramdani, E. Sicard, "EMC of integrated circuits", Springer, 2006, ISBN: 0-387-26600-3

- [2] J. M. Redouté, Jean-Michel, M. Steyaert, "EMC of Analog Integrated Circuits", 2010, Springer, 978-90-481-3230-0

- [3] Er-Ping Li, "Electrical Modeling and Design for 3D System Integration", Wiley, 2012, ISBN 978-0470623466

- [4] www.emccompo.org, an international workshop help every 2 years, only focused on EMC for integrated circuits.

- [5] http://www.apemc2015.org

- [6] <a href="http://www.ic-emc.org">http://www.ic-emc.org</a>

- [7] E. Sicard, A. Boyer, "IC-EMC v2.5 User's Manual", Oct. 2011, 260 pp, ISBN 978-2-87649-061-1

- [8] E. Sicard, A. Boyer "A Hands-On Approach to Make Electromagnetic Compatibility of Integrated Circuits Relevant to Engineers and Students", EWME 2010, Grenoble, France

- [9] IEC 61967: Integrated circuits, measurement of electromagnetic emission up to 1 GHz, <u>www.iec.ch</u>

- [10] IEC 61967 Technical Report: Near-field scan data exchange format -2014

- [11] IEC 62132: Integrated circuits, measurement of electromagnetic immunity up to 1 GHz, <a href="https://www.iec.ch">www.iec.ch</a>

- [12] IEC 62433: Models of Integrated Circuits for EMI behavioral simulationICEM July 2005, <a href="https://www.iec.ch">www.iec.ch</a>

- [13] E. Sicard et al. "EMC performance analysis of a Processor/Memory System using PCB and Package-On-Package", EMC Compo 2015, Edinburgh

- [14] L. Guibert "Study of the nonlinear effects and the susceptibility of the electronic systems", PhD report, Oct. 2014, ISAE, Toulouse, France

- [15] M. Zouaoui, "Immunity of an Ethernet Gigabit Switch in a complex architecture", JNRDM 2015, PhD University of Nice, France.

- [16] A. Boyer et al, "Evaluation of the near-field injection method at integrated circuit level", EMC Europe 2014, Gotenburg, Sept. 2014