#### A WCET estimation workflow based on TWSA model of SystemC designs

Nesrine Harrath, Vladimir-Alexandru Paun, Bruno Monsuez

#### ► To cite this version:

Nesrine Harrath, Vladimir-Alexandru Paun, Bruno Monsuez. A WCET estimation workflow based on TWSA model of SystemC designs. The 32nd IEEE Real-Time Systems Symposium, Nov 2011, Vienne, Austria. hal-01214967

#### HAL Id: hal-01214967 https://hal.science/hal-01214967

Submitted on 13 Oct 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## A WCET estimation workflow based on TWSA model of SystemC designs

#### Objectives

Nesrine Harrath- Vladimir-Alexandru Paun – Bruno Monsuez ENSTA ParisTech, Paris, France http://uei.ensta-paristech.fr

#### Issues

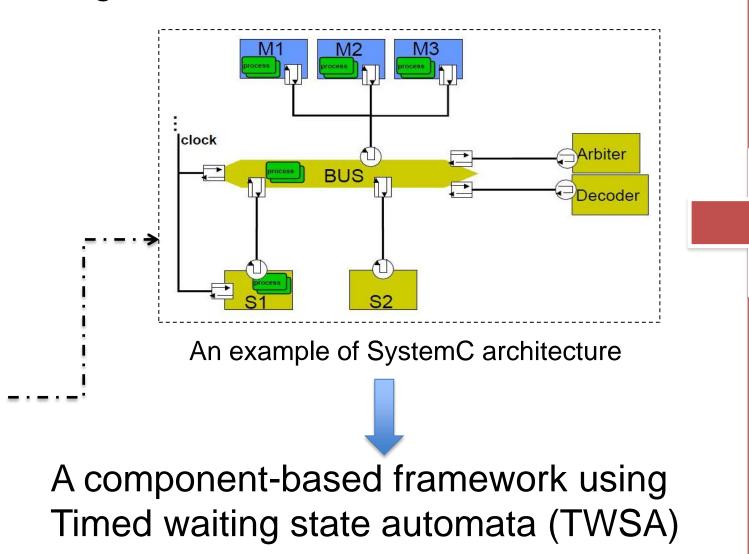

- □ Validating functional (correctness of system behavior) or non-functional properties (time constraints) of hard real time systems. Using the timed SystemC waiting state automata (TWSA) to model the hardware.

- Timing properties need to be carefully addressed as they are important in performance and safety verification of real time embedded systems.

- Giving an upper bound estimation of the worst case execution time of the code running on the modeled system.

- Scientifc challenges: verify and validate embedded software

- Industrial challenges : verify both functional and non-functional properties of a hard real time systems.

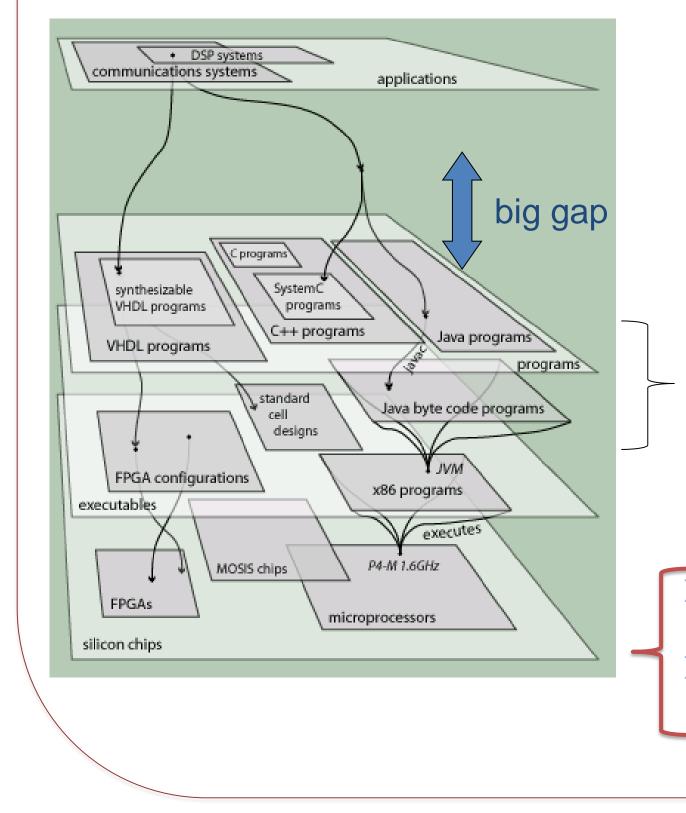

## Programming language: SystemC

SystemC is a system level design language for hardware/software modelling, it extends C++ by concurrency, time, hardware data types, reactivity... It has a simulation kernel that executes designs in a discrete-event simulation

### Problem: Building TWSA & WCET estimation

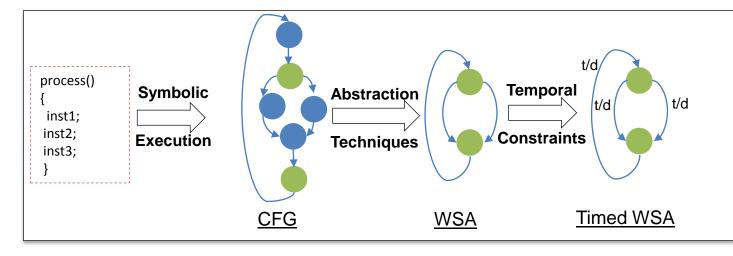

#### 1. Building the abstract model

A. Sequential analysis

# Explicit scheduler

TWSA

**B.** Concurrent analysis

#### 2. The worst case execution time analysis

> An abstract model based on the analysis of the wait/notify mechanism of SystemC. A compositional model used for a bottom/up approach.

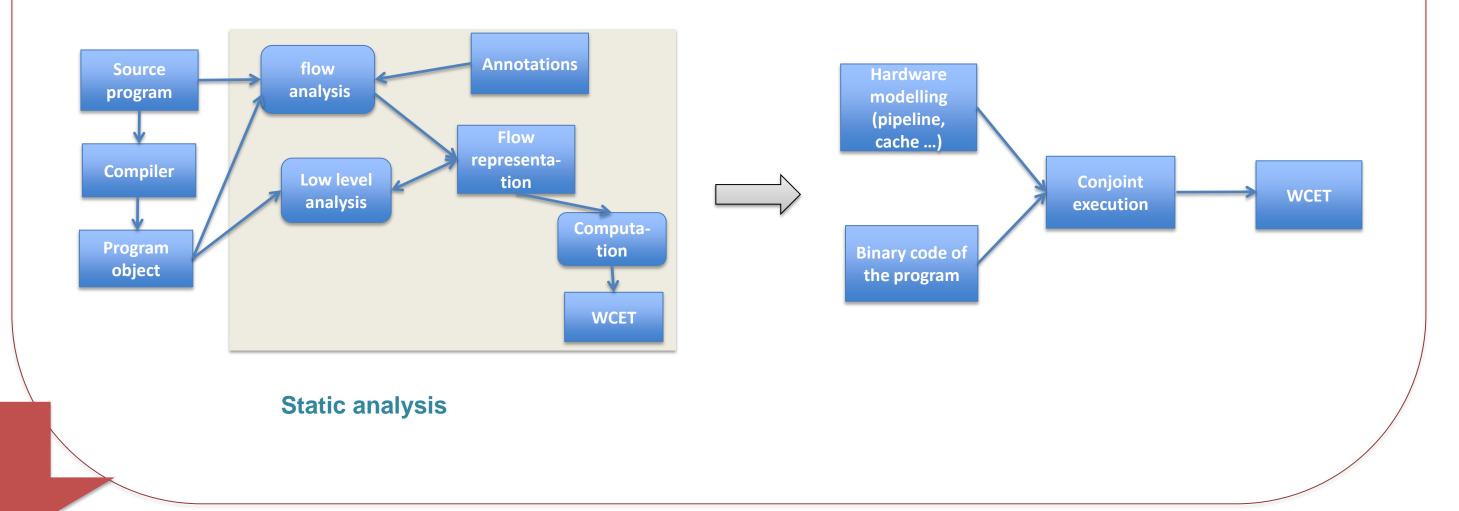

## Global approach

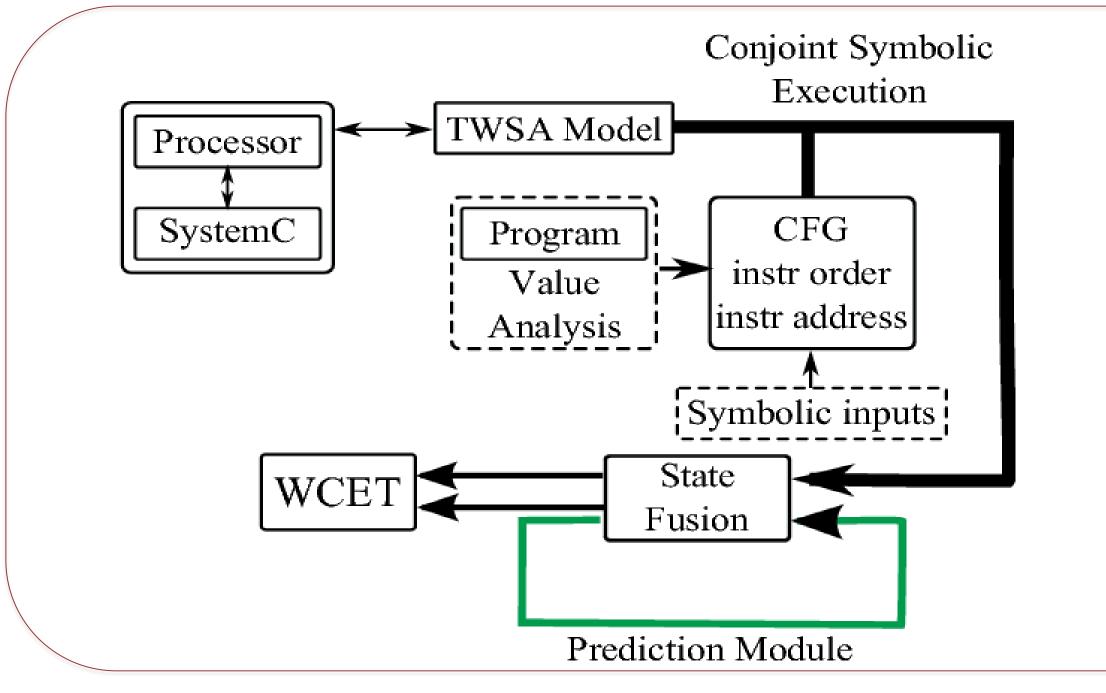

- Conjoint Symbolic Execution of the system model and the program

- □ With every executed instruction all reachable states of the processor are explored

- □ Handling the state space explosion with controlled precision:

- Using the TWSA model that keeps only valid and relevant states and that gives a  $\bullet$ precise and yet compact representation of the global system.

- Apply abstraction techniques to merge states and dynamically fusion states during the  $\bullet$ conjoint symbolic execution.

- Determining worst case behavior of the system

#### References

1. N. Harrath, and B. Monsuez, Timed SystemC Waiting-State Automata, On Third International Workshop on Verification and Evaluation of Computer

#### Results

- Modularity and adaptability to ever changing architectural models

- Generate the system model directly from the HDL code that served to create

and Communication Systems, Rabat, Morroco, 2009.

- 2. N. Harrath, and B. Monsuez, Building SystemC waiting state automata, VECOS, Tunisia, 2011

- 3. B. Benhamamouch, B. Monsuez, Computing worst case execution time (wcet) by symbolically executing a time-accurate hardware model (extented version), International Journal of Design, Analysis and Tools for Circuits and Systems, Vol. 1, No. 1, 2009.

- 1. B. Benhamamouch, B. Monsuez, F. Vdrine, Computing wcet using symbolic execution, Second International Workshop on Verification and Evaluation of Computer and Communication Systems, Leeds, England, 2008.

#### the system

Ability to verify the correctness of the system model with regard to the

upcoming certification standards

#### Future work

- Refine the SystemC model to capture precise information about the system behaviour.

- A joint study of system precision and dynamically changing architectures to give a precise estimation of WCET.

Unité d'Électronique et d'Informatique – ENSTA ParisTech – http://uei.ensta-paristech.fr 32, boulevard Victor 75739 Paris Cedex 15 bruno.monsuez@ensta-paristech.fr – 01 45 52 40 94

École Nationale Supérieure de **Techniques Avancées**