# TBES: Template-Based Exploration and Synthesis of Heterogeneous Multiprocessor Architectures on FPGA

Youenn Corre, Jean-Philippe Diguet, Dominique Heller, Dominique Blouin, Loïc Lagadec

## ▶ To cite this version:

Youenn Corre, Jean-Philippe Diguet, Dominique Heller, Dominique Blouin, Loïc Lagadec. TBES: Template-Based Exploration and Synthesis of Heterogeneous Multiprocessor Architectures on FPGA. ACM Transactions on Embedded Computing Systems (TECS), 2016, 15 (1), pp.9. hal-01172103

HAL Id: hal-01172103

https://hal.science/hal-01172103

Submitted on 11 Mar 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# TBES: Template-Based Exploration and Synthesis of Heterogeneous Multiprocessor Architectures on FPGA

Final submission to TECS, published as:

Y. Corre, J-Ph. Diguet, D. Heller, D. Blouin, L. Lagadec, *TBES: Template-Based Exploration and Synthesis of Heterogeneous Multiprocessor Architectures on FPGA*, ACM Trans. on Embedded Computing Systems (TECS), Vol. 15 Issue 1, Article. No. 9, Jan. 2016.

#### Abstract

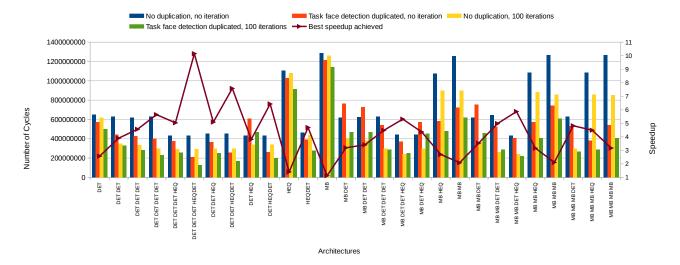

This paper describes TBES, a software end-to-end environment for synthesizing multi-task applications on FPGAs. The implementation follows a template-based approach for creating heterogeneous multiprocessor architectures. Heterogeneity stems from the use of general-purpose processors along with custom accelerators. Experimental results demonstrate substantial speedup for several classes of applications. Furthermore, this work allows to reduce development costs and save development time, both for the software architect, the domain expert, and the optimization expert. This work provides a framework to bring together various existing tools and optimisation algorithms. The advantages are manifold: modularity and flexibility, easy customization for best fit algorithm selection, durability and evolution over time, and legacy preservation including domain expert's know-how. In addition to the use of architecture templates for the overall system, a second contribution lies upon using high-level synthesis for promoting exploration of hardware IPs. The domain expert, who best knows which tasks are good candidates for hardware implementation, selects parts of the initial application, to be potentially synthesized as dedicated accelerators. As a consequence, HLS general problem turns into a constrained and more tractable issue, and automation capabilities eliminate the need for tedious and error prone manual processes during domain space exploration. The automation only takes place once the application has been broken down into concurrent tasks by the designer, who can then drive the synthesis process with a set of parameters provided by TBES to balance tradeoffs between optimization efforts and quality of results. The approach is demonstrated step by step up to FPGA implementations and executions with an MJPEG benchmark and a complex Viola-Jones face detection application. We show that TBES allows to achieve results with up to 10X speedup, to reduce development times and to widen design space exploration.

**Keywords:** Electronic System Level, High-Level Synthesis, Multiprocessor, System-on-Chip.

## 1 Introduction

In the domain of embedded systems like in high performance computing, Field-Programmable Gate Arrays (FPGA) and hybrid devices provide configurable resources for hardware (HW) specialization as well as the opportunity to take advantage of available parallelism. Both of these aspects improve the energy efficiency compared to applications running on Graphics Processing Units (GPU) and General-Purpose Processors (GPP). Application domains such as smart cameras [1], advanced acoustics [2] and cognitive radio [3] are typical examples that benefit from FPGAs including reconfiguration capabilities. Moreover embedded systems may soon take further advantage of new FPGA architectures, based on non-volatile memories with power gating capabilities [4], that will bring impressive gains in terms of power consumption.

However, embedded systems also have stringent productivity and small-market constraints. This means that designers might prefer standard architectures and easy to use design tools. Their designs also significantly rely on intensive code and IP reuse strategies. Such practices do not fit with the current complexity of programming heterogeneous hardware/software architectures on FPGAs. This programming and debugging complexity hinders their widespread adoption, despite recent progress in hardware/software interfacing in the domain of embedded systems (e.g. ARM/FPGA Accelerator Coherency Port on the Xilinx Zynq platform [5]) and HPC (IBM/Altera Coherent Accelerator Processor Interface [6]). The main reasons for these shortcomings are a lack of underlying processor architectures and a limited design reuse.

To cope with these issues, we rely on templates for Heterogeneous Multiprocessor SoC (HMPSoC) that introduce a conceptual layer, which makes the technology accessible for designers and CAD tools. The design space is constrained by these templates, and captured within flexible architecture models (specific to a given application domain), following a well-defined model of computation. This approach is based on the observation that exhaustive exploration of architecture models is useless since in practice, predefined models are well identified for given application domains. For instance, the authors of [7] propose architecture skeletons for image

processing, which can be mapped to different FPGA family targets, and updated when new targets become available. Such an approach allows to improve resource and performance estimations, and the use of fast High-Level Synthesis (HLS) tools within the Design Space Exploration (DSE) loop. Memory mapping is another tedious task for embedded system designers, and template-based methods enable the development of efficient heuristics to automate this task. Finally, code and scripts generation is simplified and allows the elimination of time-consuming low level tasks. In addition to system synthesis, the formalization and constraint of the design space through models provide a better control of the exploration of design properties such as the number and type of processors, the number, type and size of memories, the tasks and data mappings, and the coprocessors choices.

FPGAs offer more power-efficient solutions than GPPs, and support spatial parallelism leading to higher performance. However, programming for such devices remains less tractable than writing code for software functions. As a consequence, it makes sense to keep portions of an application as code running on a GPP. The main benefits are: an improved adaptability, a wide reuse of legacy code, and a good readability. On the other hand, when considering race conditions, FPGAs implementation is needed to achieve spatial execution (trading extra hardware resources for execution time). This observation advocates the use of heterogeneous systems [8], which best combine the sought characteristics of both solutions: flexibility and performances.

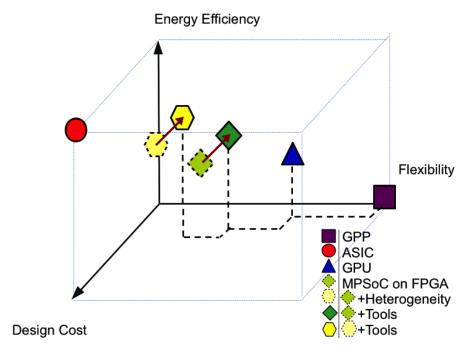

Fig. 1 illustrates the positioning of heterogeneous MPSoC designs in terms of flexibility, energy efficiency and design cost for various implementation platforms (GPP, Application-Specific Integrated Circuit (ASIC), MPSoC on FPGA, etc.). Systems implemented on GPPs are very flexible but suffer from low energy efficiency. On the opposite, ASICs are quite efficient but expensive to design. MPSoCs on FPGAs are a good compromise, but they remain complex to develop. Hence, the objective of the Template-Based Synthesis (TBES) approach and tool, presented in this paper, is to reduce the effort inherent to the development of FPGA-based systems, in order to benefit from efficiency gains provided by heterogeneity (i.e. coprocessors). We first start by presenting related work in Section 2 to compare our solution with the state of the art and to introduce our contributions. Section 3 presents the definition of the template-based architecture approach, and Section 4 describes the different steps of our design flow and TBES framework. In Section 5, we show how TBES is efficiently applied: first, on a classical Motion JPEG (MJPEG) application and second, on a complex Viola-Jones application for face detection. Finally, we conclude and present perspectives.

Figure 1: Positioning of heterogeneous MPSoC designs in terms of flexibility, energy efficiency and design cost for various execution platforms.

## 2 Related work and contributions

## 2.1 Related work

Over the years, numerous Electronic System-Level (ESL) design tools have been proposed for HMPSoC design, and a selection of these tools is presented in Table 1. We take as reference a hypothetical ideal ESL tool, regardless of its feasibility, and compare it with existing tools including TBES in order to state our contributions.

Table 1: Comparison of existing ESL frameworks.

| Frameworks                        |                                                                              | Inputs                                                                         |                                                    |                                                        | Design | Design Space Exploration                                                                |                                                                  |                                                          | Outputs                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------|--------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   | Application<br>Specifica-<br>tions                                           | Hardware                                                                       | Constraints                                        | Auton<br>Ex-<br>plo-<br>ration<br>SW<br>&<br>&<br>Arch | Sca    | Explored dimensions                                                                     | Estimations                                                      | Code<br>gen-<br>era-<br>tion                             | Hardware                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Ideal<br>Framework                | Widespread, well-known in- put languages // formalisms with no re- striction | Architecture<br>template spec-<br>ified with<br>high-level<br>formalisms       | Provided<br>by the<br>designer<br>through a<br>GUI | Yes Yes                                                | Yes    | Model, Tr<br>Mapping,<br>bata Parall<br>W partitic<br>granularity<br>uling. M.          | Fast and accurate                                                | Yes                                                      | Synthesizable<br>architec-<br>ture                 | Adapted<br>SW<br>code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $TBES \ (our\ tool)$              | C/C++ code<br>in SANLP                                                       | Architecture<br>template in<br>AADL                                            | Provided as part of the architecture template      |                                                        |        | Task & Data Mapping, Task Parallelism, HW/SW partitioning. Metrics: Performance, area   | Trace-based<br>Simulation;<br>Model-<br>based cost<br>estimation | Yes                                                      | Synthesizable arch. + backend tools files          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Daedalus [9]                      | C/C++ code<br>in SANLP                                                       | Component definitions in Pearl description language / XML for the architecture | XML files / GUI                                    | Yes No                                                 | Yes    | Task Mapping, HW/SW<br>partitioning, Schedul-<br>ing, Metrics: Perfor-<br>mance, area   | Trace-based simulation                                           | Yes                                                      | Synthesizable<br>arch. +<br>backend<br>tools files | Adapted<br>C++                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| System-<br>CoDesigner<br>[10]     | Actor-oriented<br>Model in<br>SystemC                                        | Graph of all<br>possible com-<br>ponents                                       | Mapping con- straints in un- specified formalism   | Yes                                                    | Yes    | HW/SW partitioning,<br>Task Mapping. Metrics:<br>Performance, area                      | Perf. with<br>VPC                                                | Yes                                                      | Bitstream                                          | Adapted C++                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Advanced<br>Systembuilder<br>[11] | Functional description (process + channel)                                   | HW components + topology                                                       | Mapping<br>con-<br>straints                        |                                                        |        | N/A                                                                                     | FPGA prototyp- ing: HW profiler / CABA files generation          | Yes                                                      | HLS of<br>HW com-<br>ponents                       | C code los communication of the los communication los code los cod |

| hArtes [12]                       | C code /<br>Scilab lan-<br>guage /<br>Nu-Tech<br>formalism                   | Architecture<br>template in<br>XML                                             | Pragma<br>annota-<br>tions                         | Yes                                                    | N      | Task Mapping, Task<br>Parallelism, HW/SW<br>partitioning. Metrics:<br>Performance, area | SocLib performance estimation                                    | Yes                                                      | HLS of HW<br>compo-<br>nents with<br>Dwarv [13]    | Compiled<br>binary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PeaCE~[14]                        | SPDF / fFSM<br>/ Task level<br>models of com-<br>putation                    | Set of avail-<br>able HW com-<br>ponents                                       | Specified<br>through a<br>GUI                      | Yes No                                                 | ON.    | Task Mapping, HW/SW partitioning, Scheduling. Metrics: performance, area, power         | Cosimulation / FPGA prototyping                                  | Yes,<br>simu-<br>lation<br>+<br>imple-<br>men-<br>tation | Synthesizable<br>architec-<br>ture                 | C code<br>+<br>comm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Space Code-<br>sign [15]          | C/C++ code<br>split into tasks                                               | XML Specifi-<br>cation                                                         | Specified<br>through a<br>GUI                      |                                                        | N/A    | N/A                                                                                     | Performance<br>(TLM<br>Simul.),<br>Cost, power                   | Yes<br>(with<br>extra<br>tools)                          | With extra tool (SpaceStudio GenX)                 | C/C++<br>adapted<br>code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SYLVA [16]                        | SDF graphs                                                                   | Set of Precharacterized HW components (FIMP)                                   | Sampling<br>Rate,<br>Latency                       | oN<br>ON                                               | Yes    | Task Parallelism, Scheduling, HW con- figuration. Metrics: Performance, area, power     | Area, En-<br>ergy, Time                                          | Yes                                                      | RTL HDL                                            | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Heracles [17]                     | Single or multi-threaded C/C++ code                                          | Set of Parameterized HW components                                             | Given<br>through a                                 | o<br>N                                                 | N/A    | N/A                                                                                     | Area, Per-<br>formance                                           | Yes                                                      | RTL HDL                                            | Compiled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

#### **2.1.1** Inputs

We consider three types of inputs: the specification of the application, the hardware description, and constraints on the system (available resources, targeted performances, etc.). Ideally, the application should be specified with any available formalism or language that designers are familiar with. As shown in Table 1, in many ESL frameworks these functional descriptions are expressed with a Domain Specific Language, or as software (SW) code. This code must comply with some constraints, and usually must follow a model of computation — such as Kahn Process Network (KPN, [18])[9] or Synchronous DataFlow (SDF) [16]. These restrictions are necessary in order to enable the analysis and transformations (e.g. synthesis, optimization, etc.) required to produce the final system.

Most ESL tools also rely on architecture specifications. For instance, Space Codesign [15] uses XML descriptions of components that specify the inputs. Heracles [17] is another system that provides parameterized component templates that can be configured through a GUI. However, unlike our approach, both Space Codesign and Heracles do not perform automated DSE and consequently, designers have to fully specify the entire system before its performance can be evaluated. For TBES, the level of details of the specifications is chosen by designers through selected templates, and unspecified characteristics are automatically explored by our tool.

#### 2.1.2 Design Space Exploration

The DSE should be fast even for large design spaces, by using efficient strategies to provide results satisfying the designers' constraints. To achieve this goal, the DSE process must rely on fast and accurate estimation techniques that will evaluate designs according to their performances, logic resource costs, and power consumption. ESL frameworks such as Advanced Systembuilder [11] and Space Codesign [15] do not perform a fully automated DSE. They rely on the designer for specifying the complete hardware architecture in order to produce synthesizable results. System Codesigner [10] uses a sophisticated but slow and non-deterministic multi-objective evolutionary algorithm for DSE. HLS is used but only in a first step to provide a hardware implementation for each actor selected by the designer. In SYLVA [16], an interesting automated DSE is proposed, starting from a SDF graph and a library of various functions implemented in hardware. It includes task level parallelism, hardware selection and pipelining. However, the architecture model is implicit and exclusively hardware-oriented.

In addition to the template-based strategy, another contribution of TBES is the integration of hardware accelerators exploration in the DSE loop. This is performed by generating series of accelerators by means of a fast HLS with different constraints. This estimation of IP candidates, before logic synthesis, allows to further improve the tradeoff between performance and logic resources utilization (cf. section 4.3.1). Automatic memory exploration and mapping is another important contribution of our work. This tedious task is not automated in most of the existing ESL tools

Finally, DSE must be scalable, i.e. designers should be able to balance the speed of the exploration — how long it will take to get a result satisfying the constraints — with the optimality of the results. To do so, our framework provides parameters that can be set by designers to define the DSE effort according to the desired tradeoff between optimality and solving time (cf. Section 4.4.1).

#### 2.1.3 Outputs

The expected output of an ESL framework should be the complete system implementation artifacts: a synthesizable version of the hardware architecture code, along with a version of the software code adapted to the target architecture. In addition, our framework generates the project files and scripts for backend tools corresponding to the selected target (e.g. Xilinx FPGA). Several tools exist that generate a complete implementation of HMPSoC from the designer's specifications: [19] also generates an implementation ready for backend tools along with the adapted software tasks using a thread-based operating system to hide processor heterogeneity to the designer. LegUp [20] generates an implementation of the software and hardware architecture, and in addition performs an HLS of the tasks that the designer wants to accelerate, but without performing any exploration unlike our approach.

The solution introduced in our framework is based on Model-Driven Engineering (MDE, [21]). We use MDE, which advocates the specification of the system with a set of models to support analysis such that system capabilities and quality attributes (performance, reliability, etc.) can be predicted to discover problems before system integration and testing, to avoid costly rework later in the development process. Furthermore, the models provide essential support for design space exploration and code generation. We use the Architecture Analysis and Design Language (AADL, [22]) as main specification language, coupled with our architecture template strategy, to generate the final design. This abstraction level provides the flexibility to use different templates or modify existing templates to meet application specific needs.

## 2.1.4 Conclusion

Existing tools for HMPSoC design are all missing at least one of the features we think are essential for an industry-ready ESL framework. Either they do not perform automated DSE, like Advanced Systembuilder and

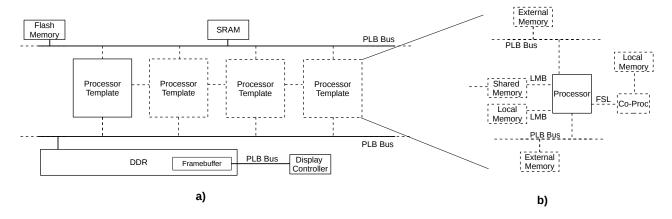

Figure 2: A graphical representation of an architecture template and a detailed view of the processor template. Solid lines indicate fixed parts (level 1) of the architecture while dotted lines represent potential instantiations (levels 2 and 3) that are decided during DSE.

Space Codesign, or their DSE process is too time-consuming — such as the SystemCoDesigner's CABA-based performance estimation, or the exhaustive exploration of Daedalus [9]. The hArtes framework [12] is too specific as it targets only a specific model of architecture: the MOLEN paradigm [23]. Consequently, there is a need for a new approach to tackle these issues, by providing designers with a way to express their specifications at the appropriate level of details, while automating the tedious tasks of the design flow.

#### 2.2 Contributions

The contributions of this work are:

- An approach based on architecture templates that:

- uses multi-level specifications providing flexibility, and usable by designers with different levels of expertise;

- formalizes and bounds the search space, allowing to develop fast and accurate algorithms for power,

performance and cost estimations and design space exploration;

- automates code and script generation, simplifies testbed generation, which is a key aspect of the design process, and allows to extract, from DSE, solutions specified with a format which is compliant with backend implementation tools;

- provides a solution to the lack of underlying platform architecture on FPGA, with a predefined but flexible architecture. This model, along with the encompassing standard Application Programming Interfaces (API) and Inputs/Outputs (I/O) information, and furthermore, libraries of software and hardware functions that can be easily updated, are of utmost importance, since they foster reuse.

- simplifies, through the use of MDE, the adaptation of developed tools to new FPGA devices and vendor tools.

- The integration of the hardware IP exploration in the DSE through the use of HLS and fast and accurate model-based estimations.

- A DSE strategy that automatically explores relevant dimensions: processor allocation, hardware accelerator choice, task mapping, memory selection and data mapping, HW/SW partitioning and the degree of parallelism. The exploration relies on a highly scalable strategy that allows for a wide range of tradeoffs between the exploration time and the optimality of the solutions.

## 3 Template-based architecture specification

#### 3.1 Template definition

Our model-driven approach relies on templates that provide pre-parameterized designs. The choice of templates is made by the designer in accordance with the application domain (DSP, video, etc.). Since for a specific domain, it is typical that different designs often have similar parameters, capturing these common parameters in a template favors reusability and reliability.

Since HMPSoC design is a complex process and requires a lot of competences, it is usually the case that different persons are responsible for developing the system: hence there are *domain experts*, that are responsible for developing the application aspects (code and task graph) and *optimization experts* that are responsible for

the implementation aspects (task mapping and data mapping). Our objective is to make our tool satisfactory for both purposes. To this end and in order to let designers focus their expertise on high added value tasks, we have divided our templates into three levels of specification. The first (static) level represents domain-specific elements that are fixed and cannot be modified during DSE. This is what is represented in solid lines in Fig. 2. The goal is to make the tool accessible to people with limited experience in design (e.g. domain experts). This is achieved by providing a library of templates — that could have been written by optimization experts — for specific application domains and device targets (e.g. Altera or Xilinx soft or hardcores). For the purpose of this study, we have targeted Xilinx and MicroBlaze (MB) architectures, but we used MDE methods to ease the management of libraries that can evolve through the integration of new templates and hardware targets.

The second level ( $DSE\ bounds$ ) provides a place for designers to specify the DSE constraints that will bound the design space such as:

- a choice of architecture templates;

- minimum and maximum number of processors as well as the available types;

- available memories including their maximum sizes and available interconnects;

- a mapping of the application input and output data;

- a mapping of specific task(s) (input, output tasks typically);

- specification of application tasks that are candidates for hardware acceleration and/or duplication for data parallelism exploitation.

The selection of a subset of tasks candidates for hardware implementation and for duplication also relies on designer's experience. Just like for architecture templates, application designers can base this selection on their own knowledge of the algorithms and on profiling results. This information is used to constrain Cost/Delay exploration, which is based on HLS iterations and task nodes duplications. Moreover, to further simplify this step, some bounds directly related to the target platform are pre-defined. These are for instance, the number and types of logic resources (e.g. number of flip-flops, registers, memories, etc.) of a FPGA board.

The third level (*expert*) of specification targets all the decisions that can be taken by the framework during DSE. This level of specification is optional and can be used by experienced designers (e.g. *optimization experts*) to enforce the value of some attributes of the specifications that should not be changed during DSE. These attributes include:

- task and memory mappings;

- number and types of processors;

- hardware accelerators exploration, synthesis and integration with software calls;

- tasks duplication for data-parallelism exploitation;

- scheduling.

Templates must be created by first specifying the fixed parts of the system, corresponding to the first level of specification. It is possible to use templates of components such as processors, memories or external peripherals of the system. An example of a processor template is given in Fig.2-b. These templates can be stored in a library for future reuse, and to further reduce the design workload. Ideally, a public database could be provided where designers could release templates (or component templates) under a reusable licence, in a similar fashion to what is done for hardware IPs released with OpenCores [24]. Once the designer has specified the parts of the template that need to be completed (level two and possibly level three), the template can be used as input for DSE. Providing these levels of system specification can greatly simplify the design phase. Designers having at their disposal a template database only have to deal with the level 2 of the template specifications, and rely on automated DSE to optimize the details of level 3.

A graphical representation of an architecture template for a video-decoder is presented in Fig.2-a. In this example, the input (e.g. read a video file on a flash drive) and the output (e.g. write to the frame buffer) will most likely be the same from one design of the decoder to another. Hence the template pre-instantiates, in the architecture, the components that are necessary for the input and output operations. In addition, a video-decoder must be able to write the decoded output video in real-time. Since the data is in a raw uncompressed format, a large bandwidth is required and it is thus required to instantiate a dedicated bus to the frame buffer.

```

Package xilinx components

public with microBlazeProperties;

processor microblaze

reset: in event port;

interrupt: in data port;

data_plb: requires bus access;

inst_plb: requires bus access;

data_lmb: requires bus access;

inst_lmb: requires bus access;

debug: requires bus access;

master_fsl: requires bus access;

slave_fsl: requires bus access;

properties

default values

microblazeProperties::FSL_links => 0;

end microblaze;

end xilinx_components;

```

Figure 3: Excerpt of the AADL model of the MicroBlaze.

## 3.2 AADL Specification

To model the system architecture, AADL [22] is used. It is a domain-specific language for embedded systems including modeling capabilities for both software and hardware parts of a system. AADL provides base component categories for representing processors, buses, memories, devices, systems, processes, threads, thread groups, data and subprograms. In TBES however, the software part is currently specified using KPN-compliant C code, and only the hardware platform is specified in AADL.

A component in AADL is described using two distinct types of declaration: i) a type declaration specifies the external interface of a component through which it can be connected to other components (I/O ports, data/bus access, etc.); ii) an implementation declaration specifies the internal composition of a component in terms of one or several subcomponents. Both type and implementation declarations can specify component properties. A set of properties predefined in the AADL standard is available to specify various configuration parameters of components. For example, for a generic memory component, the predefined properties are the size, the access rights, the word size, read and write times, etc. AADL can be extended by the addition of other properties for representing attributes of more specific components such as a MB processor. This is illustrated in Fig.3, where an excerpt of the AADL representation of a MB processor is presented.

AADL components and property sets declarations can constitute a library of components to be instantiated in FPGA-based designs. Declarations for Xilinx-specific components such as MB processors, buses, controllers, etc. have been added to a library. This is necessary to specify the values for parameters specific to Xilinx IPs.

From AADL models, we are able to generate all the implementation files for the found architecture solution needed by synthesis and implementation tools such as Xilinx XPS or Altera's Quartus. The Xilinx tools have been selected to demonstrate the proposed approach, so the generated files are the .mhs and .mss files [25]. The first file describes the synthesized hardware platform with its components, their parameters and their connections. The second file describes the driver specifications in order to call the hardware components from the software code.

The architecture selected from DSE is represented by an AADL model, which contains the instantiated components, their associated parameters represented as properties, and the components' inter-connections. This representation is automatically transformed, into the corresponding project files for the targeted FPGA design tools for an immediate implementation on the FPGA. Using this MDE technique, only the grammar and the model transformations used for code generation need to be changed to target a different FPGA synthesis tool.

## 4 Design Flow

## 4.1 Tool Philosophy

While it is now clear that efficient and easy-to-use tools are a key success-maker for embedded systems development, the impact of ESL tools has been underestimated for years. A layered approach has emerged as a divide-and-conquer strategy to cope with the increasing complexity of programming such platforms. Tools are critical in the design process – as the tools serve as the user's entry point, and directly impact the final system's performances –, it is thus essential to identify the characteristics that make a tool efficient, usable, and acceptable to users. The first challenge that tool makers must face is to offer an environment that matches the designer's habits, thus reducing the learning curve in order to lower the rejection rate from experienced – hence highly valuable – users. The tools do not aim at replacing the user's knowledge. However, a significant gain in development time is expected by having the tools handle the tedious tasks, while designers concentrate their efforts on specialized tasks requiring expertise. As a consequence, the tools must preserve the legacy artifacts

(process, IPs, etc.), since this provides continuity to the users, flattens the learning curve, and reduces the time-to-market.

From an internal point of view – being relative to tool designers – new techniques must be applied to cut off the development and testing costs of software (MDE, code generation, etc.). This is enabled by frameworks that capture the intent of existing tools as well as their API. A direct benefit lies in the ability to tailor the execution of these tools, through scripting, function invocation, etc. This is a critical issue: it leads to gaining a short term solution by implementing tailored or customized flows controlling the execution of external tools, which can be used as a comparison point to evaluate every potential future evolutions of the flow. Candidate tools to be integrated in the flow require no more than one useful functionality (transcoding, etc.) to be kept in the flow. Because their internal flow is exposed as atomic steps, elementary functions drive the selection process. Making the right choice, though, requires an educated guess coming from a deep knowledge of the domain. While being based on existing tool integration, such approaches also favor evolution.

#### 4.2 The TBES Tool

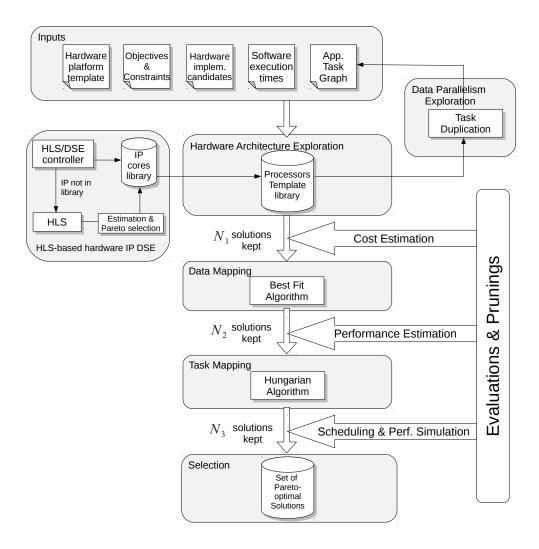

Following the presented tool philosophy, TBES was constructed by assembling different tools — already existing tools and custom-made processes — into a flow depicted in Fig.7. The next subsections present each step of the flow with their associated tools.

#### 4.2.1 Input Specifications

The required inputs for our framework are the C code of the application and a template describing a generic architecture that will be used as a basis for DSE.

For the C code input, designers must split their application into tasks, in order to express the application parallelism. This must be done manually as task splitting is application-specific and will also determine the granularity of the communication. Deciding the task granularity using automated methods is very challenging, whereas it is natural for a designer who has the knowledge of the application. To help the designer, our framework includes an automated profiling process based on the gprof standard tool[26].

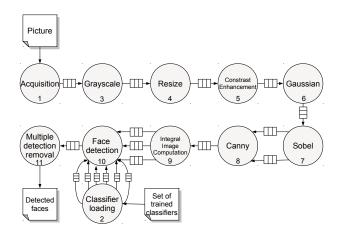

Once the task splitting is done, the C code of the application is automatically transformed to comply with the Kahn Process Network (KPN, [18]) model of computation. Each node of the resulting KPN graph represents one task of the application, and the edges represent the communication channels. The transformation is performed by a tool called KPNGen [27], which requires that the input application satisfies a number of constraints: the program must be coded in the form of one or more nested loops or conditional statements, wherein functions are called sequentially, as illustrated by Fig.4. In the loop(s), each function call corresponds to a single task,

```

for (i = 0; i < 1138; i++) {

for (j = 0; j < 42; j++) {

fetchTask(&iqzz_d);

iqzzTask(&iqzz_d, &block_YCbCr);

idctTask(&block_YCbCr, &Idct_YCbC);

yuvTask(&Idct_YCbC, &pix);

dispatchTask(&pix);

}</pre>

```

Figure 4: Example of the main loop of a program compliant with the constraints imposed by the KPNGen tool.

and communications are expressed through the call parameters, i.e. a variable used by two functions means that this variable is sent by one function to another. Other restrictions that apply on the program are that the indices of the loops must evolve following affine functions, and the control of these indices must be static, i.e. they must be determined at design time and cannot be modified during execution. The advantage of using KPN is that it makes the execution of the program deterministic, and the task synchronization is performed through blocking reads, thus allowing to easily exploit data parallelism.

For the architecture input, it is specified through the use of templates expressed in the AADL language as introduced in subsection 3.2.

#### 4.3 Performance and Cost Estimations

Two properties are estimated during our DSE targeting FPGAs: resource usage and performance. The efficiency of DSE must rely on accurate estimations. In this section, we describe these estimations performed at several stages of our design flow.

#### 4.3.1 HLS-based Coprocessor Exploration and Estimation

We use HLS to perform an exploration of different coprocessor solutions inside the loop of the heterogeneous multiprocessor DSE. This exploration is used to find the best compromise between performance and logic

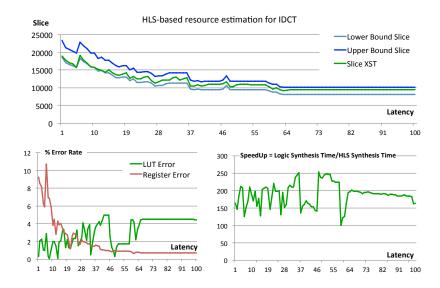

Figure 5: Exploration of an IDCT coprocessor in order to compare our HLS-based estimation with logic synthesis. Comparisons of slice estimations are shown on the top curve and the bottom ones show the accuracy of the estimation and the speedup over logic synthesis.

resource consumption. This is made possible by coupling HLS with accurate resource consumption estimators, instead of performing a costly logic synthesis of the coprocessors.

HLS is the transformation of a functional description — provided as C code in our framework — into a Register Transfer Level (RTL) description. The generated architecture described at the RTL level is compliant with an architecture model that depends on the HLS tool. The HLS tool currently used in our framework is GAUT [28], which is linear in complexity. It is a free HLS tool based on a Data Flow Graph model and therefore dedicated to data-dominated algorithms. From a C/C++ specification and a set of design constraints, GAUT automatically generates a potentially pipelined RTL architecture in two formalisms: in VHDL for synthesis, and in SystemC for virtual prototyping. In our flow, the set of design constraints is provided by the HLS/DSE controller (cf. Fig.7), in order to generate and evaluate a set of coprocessors with several performance/resource tradeoffs. The HLS constraints we consider for automated exploration are the latency and the communication model (FIFO or shared memory). The generated architecture is composed of i) a processing unit composed of the data-path (logic/arithmetic operators + storage elements + steering logic) and an FSM controller; ii) a memory unit composed of memory banks and associated controllers and iii) a communication interface which can be implemented as a FIFO, a shared memory (optionally with ping pong mode), or a 4-phase handshake. Given that the underlying model of architecture of GAUT is clearly defined, it is possible to perform a resource usage estimation. So after behavioral synthesis, the following features are known exactly:

- allocated data-path logic/arithmetic operators: numbers of DSP blocks or LUTs;

- number of registers;

- width and height of the FSM controller: slices number (Distributed RAM) or BRAMs;

- number and size of multiplexers;

- width and size of memories: slices number (Distributed RAM) or BRAMs.

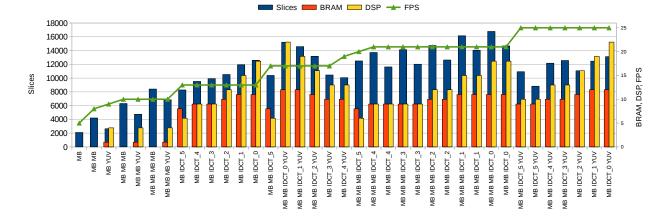

From these features, we can estimate the usage of FPGA resources: LUTs, registers, DSP blocks, block RAM, etc. Fig.5 presents the results of resource estimation on an IDCT algorithm from the MJPEG benchmark. For this experiment, we generated a series of IDCT coprocessors with varying latency, and then from the HLS results computed an estimation. We then performed a logic synthesis with the Xilinx XST synthesis tool to measure the accuracy of our estimation. For slices (which is the basic logic block in Xilinx FPGAs, gathering LUTs + registers + dedicated multiplexer), the tool computes a lower (100% use of slices resources) and an upper bound (80% use of slices resources). The upper bound rate has been set (80%) from HLS benchmarks in the domain of signal and image processing: FFT, IDCT, Sobel, Gaussian filter, Walsh-Hadamard transform, FIR, IIR, Cordic, AES, etc. The results of these benchmarks and more details on our estimation method can be found in [29]. The bottom left graph of Fig.5 shows, for the same IDCT series, the error percentage between the number of LUTs and registers obtained with our estimation and the real cost obtained after logic synthesis. We can see that the estimation error of LUTs is usually under 5% and the estimation error of registers is higher (up to 10%) in some cases, probably due to fan-out sizing reasons (register duplication). The bottom right graph shows that we obtain speedups of two orders of magnitude over logic synthesis. Moreover, the speedup increases with application complexity and allows to quickly explore the design space of solutions.

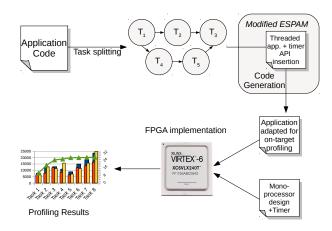

Figure 6: Flow of the on-target profiling step.

In conclusion, HLS offers a fast implementation solution and a possibility to explore the design space of hardware IP in an efficient way. A quick and accurate estimation of results is useful because designers can quickly measure the effects of code transformation and resource and timings constraints.

#### 4.3.2 Application Profiling

The exploration starts with an automated and non-intrusive on-target profiling, which is performed to obtain, for each task, accurate performance measurements for the targeted processor. These measurements are then used during DSE for mapping performance estimation. They also provide a way to determine a set of task candidates for hardware acceleration.

In our framework, this profiling is automated through code transformation and the use of a pre-designed FPGA system that contains the target processor (e.g. MB) with hardware timers to measure execution time. That step is illustrated by Fig.6. During the code transformation, which is performed by a modified version of the ESPAM tool [30], each task becomes a thread and calls to the timers are inserted. Inter-task communication times are not measured during profiling as they depend on design decisions such as task and data mapping, which have not yet been taken at this stage. During this profiling, it is the responsibility of the designer to provide a dataset representative of the final system execution.

#### 4.3.3 Multiprocessor without Interconnect and Dependencies

During early stages of the DSE process, when only the number and the type of processors have been decided, a first estimation is performed. We first check that the design does not consume more logic resources than what has been specified. If this is the case, the design is discarded and not further explored. Otherwise, we perform a performance estimation. At this stage, such estimation is obviously very rough. However, it is only used to establish if acceleration is needed. The estimation is given by the following formula:

$$\frac{CT}{nP} + nW \times nWC + nR \times CC \tag{1}$$

where CT is the computing time, nP the number of processors, nW the number of write operations, nWC the cost in cycles of a write operation, nR the number of read operations, and CC the cost in cycles of a cache miss. In this equation, we divide the total execution time of the application — computed using the profiling described in the above section — by the number of processors, which yields the maximum possible acceleration. While this is overly optimistic, it is counterbalanced by the communication cost for which we assume that a cache miss occurs at each read.

#### 4.3.4 Communication

Since dataflow applications are usually data-intensive, design choices for communication such as data mappings, memory types and sizes, bus types are as equally important as computation design choices. So in order to detect possible contentions on a bus or a memory, we first compute the number of cycles necessary to read — or write since the formula is the same — the quantity of data for one iteration of the program from a given memory. It is computed from the following formula:

$$nRC = RL_{mem} \times \frac{dataSize}{B_{mem}} + dataSize \tag{2}$$

where nRC is the total number of cycles used for read operations in one iteration of the program,  $RL_{mem}$  the latency value in cycles for a read operation in the memory mem, and  $B_{mem}$  the number of bytes transferred

in one burst. With this information, we can estimate the risk of congestion as:

$$CR_{mem} = \frac{F_{mem}}{nI \times (nRC + nWC)} \tag{3}$$

where  $CR_{mem}$  is the congestion ratio of the given memory mem,  $F_{mem}$  the frequency of the memory, nI the number of iterations of the program in one second, and nRC and nWC the number of cycles for the read operations — write operations respectively — given by the previous equation (2). The result is a ratio, which when higher than one means that the memory is overloaded. When lower than one, then no congestion should occur. A similar formula can be used for communication channels:

$$CR_{comm} = \frac{F}{L_{comm} \times (dataSize/B_{comm})}$$

(4)

where  $CR_{comm}$  is the congestion ratio of the given communication channel comm, F the frequency of the system,  $L_{comm}$  the latency of the communication channel, and  $B_{comm}$  the bandwidth of the channel in bytes per second. Both of these metrics are used during our data mapping exploration in order to estimate the degree of congestion of a memory or a channel.

#### 4.3.5 Simulation

Once the full system has been specified, a final performance estimation is performed with the Sesame simulation tool [31]. This simulation is trace-based and takes into account three kinds of events: execute, read and write. Using the trace of these events and a description of the architecture and its components, Sesame provides a fast estimation of the system performances. While being significantly faster than a Cycle Accurate-Bit Accurate simulation, it is still the most time-consuming operation of our DSE flow. The total simulation time depends on the size of the trace and the number of designs to evaluate. It is thus important on one hand to limit the size of the trace by finding the smallest execution time that still produces results representative of the final performance, and on the other hand to perform a selection of the designs to be simulated. The version of Sesame implemented in the Daedalus framework is used to generate exhaustively the task mappings. We thus modified it in order to take into account only the mappings selected by our tool, leading to shorter exploration times as shown in the results section.

## 4.4 Design Space Exploration

The DSE flow is shown in Fig.7, and a more detailed description of the DSE algorithm can be found in [29]. We focus here on the task and data mapping, as well as on the pruning strategies used to provide designers with the possibility to balance exploration time and solution optimality.

#### 4.4.1 Pruning Strategy

Our goal is to offer to designers a highly scalable exploration strategy, which ranges from a greedy algorithm that will return the first solution that satisfies the constraints, to an exhaustive exploration, and includes in between a very large number of intermediary solutions that offer a tradeoff between the exploration time and the optimality of the resulting solution. To this end, designers can specify through variables (the  $N_1, N_2, N_3$  in Fig.7), the maximal number of solutions they want to keep at the end of each step of the design flow. Consequently, one can decide to keep a larger number of solutions on the steps that would need more exploration. This selection process is shown in Fig.7 and in Algorithm 1. The selection relies on metrics used to evaluate the performance or the cost of the system such as the ones described in Section 4.3.

## 4.4.2 Task and Data Mapping Heuristics

The algorithm for data and task mapping is described in Algorithm 1. A few definitions must be introduced to understand the algorithm:

- TaskClusters: set of tasks to be mapped, gathered as clusters of independent tasks.

- *ProcSet*: set of processors in the architecture.

- DataSet: set of data representing communications between two tasks sorted in decreasing size.

- MemorySet: set of memories sorted in decreasing order of speed.

The data mapping consists of assigning the data communicated between the tasks onto the memories of the architecture. In our framework, the implemented data-mapping strategy follows a best-fit allocation, which consists in assigning data to the fastest memory that has sufficient space to store the currently assigned data. Since we want to maximize the size of the explored design space, we generate several different data mappings in order to introduce diversity. To achieve this goal, we combine three strategies that produce interesting variations:

## Algorithm 1 Data and Task Mapping Algorithm.

```

1: Initialization: 2: All hardware accelerated Tasks T are mapped on the corresponding Accelerator_i

3:

for all N_1 architecture solutions do

//Data Mapping

//Consider several sizes for synthesized memories (e.g. BRAM)

6:

7:

8:

//Randomize memories latencies

//Map biggest data on fastest memories first for all Data D in DataSet do

9:

for all Memory M in MemorySet do

10:

11:

while M has enough space for D do

12:

mapDataOnMem(D,\,M)

13:

end while

14:

end for

15:

end for

16:

//Map smallest data on fastest memories first

17:

for all Data D in ReverseDataSet do

18:

for all Memory M in MemorySet do

while M has enough space for D do mapDataOnMem(D, M) end while

19:

20:

21:

22:

23:

24:

25:

26:

27:

28:

end for

//Selection of the N_2 best data-mappings

//Task Mapping

// Itask Mapping

for all N<sub>2</sub> selected mapping solutions do

//Make first task mapping with less loaded processors

for all Task T in TC<sub>1</sub>, the first element of TaskClusters do

for all Processor P in ProcSet do

29:

30:

31:

if P is the less loaded proc then

32:

33:

mapTaskOnProc(T,\,P)

end if

34:

end for

35:

end for

//Hungarian Algorithm for all Task cluster TC_i of TaskClusters do

36:

37:

for all Task T in TC_i do for all Processor P in ProcSet do for all Memory M in MemorySet do costMatrix = computeCostMatrix(\alpha \times execTime_{(T,P)}, \beta \times comm_{(T,M)}, \gamma \times procLoad_{(P)}, \delta \times memLoad_{(M)})

38:

39:

40:

41:

42:

43:

end for

44:

end for

apply

Hungarian

Algorithm<br/>(TC_i,\, {\rm costMatrix})

45:

46:

checkForCongestion()

47:

end for

48:

49: //Selection of the N_3 best task-mappings 50: end for

end for

```

Figure 7: Flow of the Design Space Exploration.

- The read and write latencies of the different memory types are modified with a random coefficient that introduces in the DSE variations representing bus access conflicts and cache misses.

- Memories that are synthesized, such as BRAM, do not have a fixed size. So another dimension explored during data mapping is memory size. The allowed sizes must be provided by the designer.

- Last, two ways for the order in which data are mapped are considered: biggest data size mapped first and smallest data size mapped first.