# From AADL to Timed Abstract State Machines: A Verified Model Transformation

Zhibin Yang, Kai Hu, Dianfu Ma, Jean-Paul Bodeveix, Lei Pi, Jean-Pierre Talpin

# ▶ To cite this version:

Zhibin Yang, Kai Hu, Dianfu Ma, Jean-Paul Bodeveix, Lei Pi, et al.. From AADL to Timed Abstract State Machines: A Verified Model Transformation. Journal of Systems and Software, 2014, vol. 93, pp. 42-68. 10.1016/j.jss.2014.02.058 . hal-01123837

HAL Id: hal-01123837

https://hal.science/hal-01123837

Submitted on 5 Mar 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Open Archive TOULOUSE Archive Ouverte (OATAO)

OATAO is an open access repository that collects the work of Toulouse researchers and makes it freely available over the web where possible.

This is an author-deposited version published in : <a href="http://oatao.univ-toulouse.fr/Eprints ID">http://oatao.univ-toulouse.fr/Eprints ID</a> : 12950

**To link to this article**: DOI::10.1016/j.jss.2014.02.058 URL: <a href="http://dx.doi.org/10.1016/j.jss.2014.02.058">http://dx.doi.org/10.1016/j.jss.2014.02.058</a>

**To cite this version**: Yang, Zhibin and Hu, Kai and Ma, Dianfu and Bodeveix, Jean-Paul and Pi, Lei and Talpin, Jean-Pierre *From AADL to Timed Abstract State Machines: A Verified Model Transformation*. (2014) Journal of Systems and Software, vol. 93. pp. 42-68. ISSN 0164-1212

Any correspondance concerning this service should be sent to the repository administrator: <a href="mailto:staff-oatao@listes-diff.inp-toulouse.fr">staff-oatao@listes-diff.inp-toulouse.fr</a>

# From AADL to Timed Abstract State Machines: A verified model transformation

Zhibin Yang a,b,\*, Kai Hu a,\*, Dianfu Ma a,\*, Jean-Paul Bodeveix b, Lei Pi c, Jean-Pierre Talpin d

- <sup>a</sup> School of Computer Science and Engineering, Beihang University, Beijing, China

- <sup>b</sup> IRIT-CNRS, Université de Toulouse, Toulouse, France

- <sup>c</sup> INTECS, Toulouse, France

- d INRIA-Rennes, Campus de Beaulieu, Rennes, France

#### ABSTRACT

Architecture Analysis and Design Language (AADL) is an architecture description language standard for embedded real-time systems widely used in the avionics and aerospace industry to model safety-critical applications. To verify and analyze the AADL models, model transformation technologies are often used to automatically extract a formal specification suitable for analysis and verification. In this process, it remains a challenge to prove that the model transformation preserves the semantics of the initial AADL model or, at least, some of the specific properties or requirements it needs to satisfy. This paper presents a machine checked semantics-preserving transformation of a subset of AADL (including periodic threads, data port communications, mode changes, and the AADL behavior annex) into Timed Abstract State Machines (TASM). The AADL standard itself lacks at present a formal semantics to make this translation validation possible. Our contribution is to bridge this gap by providing two formal semantics for the subset of AADL. The execution semantics provided by the AADL standard is formalized as Timed Transition Systems (TTS). This formalization gives a reference expression of AADL semantics which can be compared with the TASM-based translation (for verification purpose). Finally, the verified transformation is mechanized in the theorem prover Coq.

# 1. Introduction

Embedded real-time systems, such as those for avionics and aerospace platforms, represent one of the most safety-critical categories of system. Their system behaviors do not only rely on the software/hardware architecture, but also rely on the runtime environment, such as scheduling, communication and reconfiguration. Moreover, they are more and more complex, so reducing the development cost and time is an important element of design in these systems (van Vliet, 2008).

The Architecture Analysis and Design Language (AADL) (SAE, 2009) is an SAE International (formerly known as the Society of Automotive Engineers) standard (SAE AS5506). AADL employs formal modeling concepts for the description of software/hardware architecture and runtime environment in terms of distinct components and their interactions, and it is especially effective for model-driven design of complex embedded real-time systems (Walker et al., 2013).

A safety-critical system is often required to pass stringent qualification and certification processes (for example DO-178C) before its deployment. When described using an AADL model, such a system specification is often transformed to another formal model for verification and analysis. Examples of such transformations are numerous: translations to Behavior Interaction Priority (BIP) (Chkouri et al., 2008), to TLA+ (Rolland et al., 2008), to real-time process algebra ACSR (Sokolsky et al., 2006), to IF (Abdoul et al., 2008), to Fiacre (Berthomieu et al., 2009), to Real-Time Maude (Ölveczky et al., 2010), to Lustre (Jahier et al., 2007), to Polychrony (Ma et al., 2009), etc. The goal of such a translation is to reuse existing verification and analysis tools and their formal model of computation and communication for the purpose of validating the AADL models.

<sup>\*</sup> Corresponding authors. Tel.: +33 0637053466, +86 13522338282, +86 13701068603. *E-mail addresses*: Zhibin.Yang@irit.fr (Z. Yang), hukai@buaa.edu.cn (K. Hu), dfma@buaa.edu.cn (D. Ma), bodeveix@irit.fr (J.-P. Bodeveix), lei.pi@intecs.it (L. Pi), Jean-Pierre.Talpin@inria.fr (J.-P. Talpin).

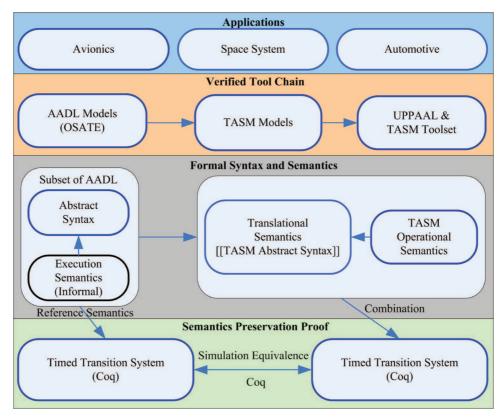

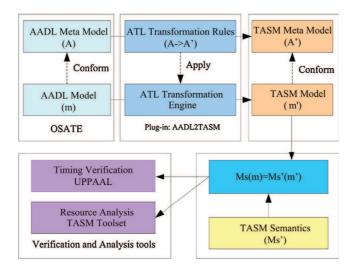

Fig. 1. A global view of the verified AADL model transformation.

One challenge, however, is the problem of proving that the translation itself preserves the intended semantics of the AADL model in the first place or, at least, some of the specific properties or requirements it needs to satisfy (Cabot et al., 2010; Lano and Rahimi, 2013; Giese et al., 2006; Narayanan and Karsai, 2008; Narayanan, 2008; Guerra et al., 2013; Kessentini et al., 2011; Mottu et al., 2008; Xiong et al., 2007).

This paper presents a machine checked semantics-preserving transformation of a subset of AADL into Timed Abstract State Machines (TASM) (Ouimet and Lundqvist, 2006, 2008). TASM is an extension of the Abstract State Machine (ASM) formalism (Börger, 2002), which supports the specification of timing and resource consumption as well as behavior and communication. Compared with the existing approaches such as translations to BIP, TLA+, ACSR, IF, Fiacre, Real-Time Maude, Lustre, etc., we consider some resource information in the transformation. Furthermore, a formal proof of the semantics preservation of the transformation has not been considered by them. In this work, the theorem prover Coq (Bertot and Castéran, 2004) is used to prove the methodology, i.e. the correctness of the translation.

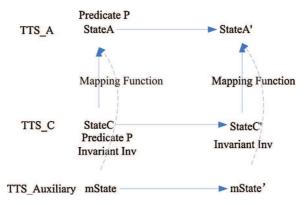

Following the global idea, we would like to provide a verified tool chain for the end users (as shown in Fig. 1). The first version of the model transformation tool prototype AADL2TASM has been implemented in ATL (ATLAS Transformation Language) (Jouault et al., 2006) directly. AADL2TASM is a plug-in of the AADL modeling environment OSATE (CMU, 2006), which supports model checking using UPPAAL (Behrmann et al., 2004) and simulation using the TASM Toolset (Ouimet and Lundqvist, 2007). It is a good way to provide a basis for the Coq mechanization. Finally, we envision the extraction of a complete tool from the mechanization in the future, that is the verified tool chain. Underlying the tool is the formal translational semantics (Combemale et al., 2009; Cleenewerck and Kurtev, 2007; Gargantini et al., 2009) of AADL by a mapping to TASM, namely, the sentences of the target language express the semantics of AADL. To enable the proof of semantics preservation of the model transformation: (1) the informal execution semantics formalized directly using Timed Transition System (TTS), is considered as a reference semantics, because we cannot directly prove that the translational semantics is equivalent with the informal one which is provided by the AADL standard; (2) combining the translational semantics (expressed by the TASM sentences) with the semantics of TASM, we can obtain another way to execute the AADL model, and it is constructed as another TTS; (3) the reference semantics is supposed to be correct, and if there is a simulation equivalence relation between the two TTSs, we say the translation preserves the AADL semantics.

The goal of this paper is to verify the translation from AADL to TASM. The main contributions are as follows: (1) a reference semantics of a subset of AADL is formalized in TTS, including periodic threads, data port communications, mode changes and the behavior annex; (2) a formal translational semantics of the subset of AADL by translating it to TASM; (3) a mechanized proof of the semantics preservation of the transformation from AADL to TASM based on (1) and (2).

The rest of the paper is organized as follows. Section 2 introduces Timed Transition System and its operations. Section 3 presents an overview of the AADL and the abstract syntax of the chosen subset of AADL. The abstract syntax of TASM is expressed in Section 4. Section 5 presents the two formal semantics of the subset of AADL. Section 6 shows the mechanized proof of semantics preservation. We present some discussion about the model transformation tool prototype AADL2TASM in Section 7. Section 8 discusses the related work, and Section 9 gives some concluding remarks.

#### 2. Timed Transition Systems

TTS is a well-known model used to express real-time behaviors and is often used to compare semantics equivalence between different real-time specification languages (Bérard et al., 2005, 2008). However, there are different definitions and operations on TTS for different uses. For example, some definitions use clock variables to express time in TTS (Hune and Nielsen, 1998), others express time by associating delays, or time intervals to transitions (Henzinger et al., 1994). In this paper, we use a variant of the TTS defined by Bérard et al. (2005, 2008), where we add a global state to allow communication through shared variables.

Given a global state  $S^G$  with its initial set  $I^G$  and  $\mathbb{R}^+$  the set of nonnegative reals, a TTS is defined as follows.

**Definition 1** (*Timed Transition Systems*). A TTS defined over  $S^C$  and  $I^C$  is a tuple  $\Gamma = \langle S^L, I^L, \Sigma, P, \rightarrow , L \rangle$  such that:

- $S^L$  is a set of local states,

- $I^L \subseteq S^L$  is the set of initial local states,

- $\Sigma$  is a finite set of *labels*,

- *P* is a set of *predicates*,

- $\rightarrow \subseteq S \times (\Sigma \cup \mathbb{R}^+) \times S$  is the *transition* relation,

- $L: S \to 2^p$  is a labeling function, L maps each state to the set of predicates which are true in that state,

where  $S = S^G \times S^L$ .

We write  $s \xrightarrow{\delta} s'$  for  $(s, \delta, s') \in \to$ . Here s, s' are values of the type S, and  $\delta \in (\Sigma \cup \mathbb{R}^+)$ . There are two kinds of transition relations: discrete and continuous. Continuous transitions are typically required to obey the following properties  $(\forall d, d' \in \mathbb{R}^+)$ :

- 0-delay:  $s \xrightarrow{0} s' \Leftrightarrow s = s'$ ,

- additivity:  $s \xrightarrow{d} s' \wedge s' \xrightarrow{d'} s'' \Rightarrow s \xrightarrow{d+d'} s''$ , continuity:  $s \xrightarrow{d+d'} s' \Rightarrow (\exists s'')(s \xrightarrow{d} s'' \wedge s'' \xrightarrow{d'} s')$ ,

- time-determinism:  $s \xrightarrow{d} s' \wedge s \xrightarrow{d} s'' \Rightarrow s' = s''$ .

Then, we consider operations on TTS, including synchronous product and simulation equivalence.

Synchronous product (Arnold, 1994) is used to define the semantics of an AADL model as the composition of the semantics of its constituents. This way, the equivalence proof can be obtained in a compositional way from the correctness of the translation of elementary AADL model elements such as threads, connections and modes.

**Definition 2** (*Synchronous product*). Consider *n* TTSs over the same alphabet Σ and the global state  $S^G$ ,  $\Gamma_i = \langle S^L_i, I^L_i, \Sigma, P_i, \rightarrow_i, L_i \rangle$ , i = 1, ..., n, where the set of predicates  $P_i$  are supposed to be pair-wise disjoint. The synchronous product is a TTS:  $\Gamma = \prod_{i=1,...,n} \Gamma_i = \langle S^L, I^L, \Sigma, P, \rightarrow, L \rangle$ ,

such that:

- $$\begin{split} \bullet \ S^L &= S_1^L \times \dots \times S_i^L \times \dots \times S_n^L, \\ \bullet \ I^L &= I_1^L \times \dots \times I_i^L \times \dots \times I_n^L, \\ \bullet \ P &= \bigcup_{i=1,\dots,n} P_i, \end{split}$$

- → satisfies the following rules:

$$\frac{\forall i, (g, l_i) \overset{e}{\rightarrow}_i (g', l'_i)}{(g, (l_1, \dots, l_i, \dots, l_n)) \overset{e}{\rightarrow} (g', (l'_1, \dots, l'_i, \dots, l'_n))}, e \in \Sigma$$

$$\frac{\forall i, (g, l_i) \overset{d}{\rightarrow}_i (g', l_i')}{(g, (l_1, \dots, l_i, \dots, l_n)) \overset{d}{\rightarrow} (g', (l_1', \dots, l_i', \dots, l_n'))}, d \in \mathbb{R}^+$$

The rules represent that all TTSs make a step at the same time with compatible updates of the global state, and we consider discrete transitions and continuous transitions separately.

•  $L = \{(g, (l_1, \ldots, l_n)) \mapsto \bigcup_{i=1,\ldots,n} L_i(g, l_i)\}.$

Bisimulation and its variants (Milner, 1989) are usually formulated over TTSs. In this work, what is proved in Cog is strong simulation equivalence which implies ACTL (the universal fragment of Computation Tree Logic) and ECTL (the existential fragment of Computation Tree Logic) preservation (Baier and Katoen, 2008) and thus preservation of the UPPAAL query language.

**Definition 3** (Strong simulation). Given an alphabet  $\Sigma$  and two TTSs over the two global state  $S_1^G$  and  $S_2^G$ ,  $\Gamma_1 = \langle S_1^L, I_1^L, \Sigma, P, \rightarrow_1, L_1 \rangle$  and  $\Gamma_2 = \langle S_2^L, I_2^L, \Sigma, P, \rightarrow_2, L_2 \rangle$ , we say that  $\Gamma_2$  strongly simulates  $\Gamma_1$ , denoted  $\Gamma_1 \preceq \Gamma_2$ , if there exists a relation  $R \subseteq S_1 \times S_2$  called a strong simulation relation where  $S_1 = S_1^G \times S_1^L$  and  $S_2 = S_2^G \times S_2^L$ , such that:

- $\forall s_1^0 \in I_1^G \times I_1^L$ , there exists  $s_2^0 \in I_2^G \times I_2^L$ , such that  $(s_1^0, s_2^0) \in R$ ,

- $\forall (s_1, s_2) \in R$ ,  $\forall e \in \Sigma$ ,  $\forall s_1'$  such that  $s_1 \xrightarrow{e} 1s_1'$ , there exists  $s_2' \in S_2$  such that  $s_2 \xrightarrow{e} 2s_2'$  and  $(s_1', s_2') \in R$ ,

- $\forall (s_1, s_2) \in R$ ,  $\forall d \in \mathbb{R}^+$ ,  $\forall s_1'$  such that  $s_1 \xrightarrow{d} 1s_1'$ , there exists  $s_2' \in S_2$  such that  $s_2 \xrightarrow{d} 2s_2'$  and  $(s_1', s_2') \in R$ ,

- $\forall (s_1, s_2) \in R$ , then  $L_1(s_1) = L_2(s_2)$ .

Here the simulation relation *R* is general. It will be specialized when used in the proof (see Section 6). Additionally, discrete transitions and continuous transitions are treated separately.

**Definition 4** (Strong simulation equivalence). if  $\Gamma_1 \preceq \Gamma_2$  and  $\Gamma_2 \preceq \Gamma_1$ , then we say there is a strong simulation equivalence relation between  $\Gamma_1$  and  $\Gamma_2$ , i.e. two-directions strong simulation, noted  $\Gamma_1 \simeq \Gamma_2$ .

#### 3. A subset of AADL

In this section, we first give an overview of the AADL, and then we elaborate the language subset that we will consider for translation. Finally, the abstract syntax of the considered subset is presented.

#### 3.1. Overview of the AADL

AADL describes a system as a hierarchy of software and hardware components. It offers a set of predefined component categories as follows:

- Software components: thread, thread group, subprogram, data and process.

- Hardware components: processor, memory, bus, device, virtual processor and virtual bus.

- System components which represent composite sets of software and hardware components.

A component is given by its *type* and its *implementation*. The type specifies the component's external interface in terms of *features*. Features can be ports, server subprograms or data accesses depending on the chosen communication paradigm. Implementations specify the internal structure of the components in terms of a set of *subcomponents*, their *connections*, *modes* that represent operational states of components, and *properties* that support specialized architecture analysis.

However, system behaviors do not only rely on the *structure* defined by the above components but also rely on the runtime environment (like operating system or virtual machine) (Feiler and Gluch, 2013). AADL offers an *execution model* that covers most of the runtime needs of real-time systems: (1) a set of execution model attributes can be attached to each AADL declaration, such as thread dispatch protocols, communication protocols, scheduling policies, mode change protocols, and partition mechanisms (support of ARINC 653 standard in avionic systems) (Delange et al., 2009), etc.; (2) the semantics of the execution model is also given, namely the execution semantics of AADL.

Moreover, the *behavior annex* (SAE, 2011) describes more precisely the behaviors of threads and subprograms. The behavior annex has an independent syntax and semantics. So, an AADL model is composed of its structure, its execution model and its behavior annex. Correspondingly, the AADL model transformation and translational semantics, should cover these three aspects (Abdoul et al., 2008).

# 3.2. The considered subset of AADL

AADL execution model mixes synchronous and asynchronous aspects (SAE, 2009; França et al., 2007; Filali-Amine and Lawall, 2010). A synchronous execution model is obtained by considering logically synchronized periodic threads communicating through data ports. In the asynchronous execution model, it is possible to raise events, to specify sporadic and aperiodic threads, communication through shared variables, and remote procedure calls, etc. As a main difference with the existing approaches, we focus on the verification of the AADL model transformation. However, describing the formal semantics of the whole AADL is a very hard and time consuming task, as well as formally proving the correctness of its translation to another formalism. Thus we have identified a subset and restricted the correctness proof to this subset. In this paper, we consider the synchronous one, including periodic threads, data port communications, mode changes and the behavior annex. This subset is usually used in safety-critical systems, to guarantee the determinism and predictability of system behaviors. Here multi-partitions and multi-processors mechanisms are excluded, and we just consider simple scheduling features: single-processor and non-preemption.

A quick overview of the considered subset of AADL is given, including the structural elements and the execution model attributes. Its execution semantics will be given and formalized in Section 5.

# 3.2.1. Periodic threads

Based on the modes of the system, a thread may be *active*, *inactive*, or *halted*. In AADL, only active threads can be dispatched and scheduled for execution.

A thread can have input ports and output ports to receive and send messages. AADL defines three types of ports: *data*, *event* and *event data* ports. Event and event data ports support queuing buffers, but data ports only keep the latest data. We consider data ports. However, out event ports used to trigger mode changes are also considered.

AADL supports the classical thread dispatch protocols: Periodic, Aperiodic, Aperiodic and Background. Periodic dispatch is the only protocol considered in this paper, and its execution model attribute is expressed as: Dispatch\_Protocol  $\Rightarrow Periodic$ .

Moreover, several properties can be assigned to a periodic thread, such as: period given by the *Period* property in the form of Period  $\Rightarrow$  100 ms (i.e. Frequency = 10 Hz), execution time through the *Compute\_Execution\_Time* property or the *computation(BCET, WCET)* statement of the behavioral annex, and *Deadline*. By default, when the deadline is not specified it equals the period.

#### 3.2.2. Data port communications

Port connections link ports to enable the exchange of messages among components. In order to ensure deterministic data communication between the data ports of periodic threads, AADL offers two communication protocols: Immediate and Delayed. The execution model attribute is attached to the data ports, and expressed as:  $Timing \Rightarrow \{Immediate, Delayed\}$ .

For an immediate connection, the execution of the recipient thread is suspended until the sending thread completes its execution when the dispatches of sender and receiver threads are simultaneous. For a delayed connection the output of the sending thread is not transferred until the sending thread's deadline, typically the end of the period. Notice that they have not necessarily the same period, which allows over-sampling and under-sampling. A port connection can also be declared with modes specifying whether the connection is part of specific modes or is part of the transition between two specific modes.

#### 3.2.3. Mode change

A *mode* represents an operational state, which manifests itself as a configuration of contained sub components, connections, and mode-specific property values. When multiple modes are declared for a component, a *mode state machine* identifies which event arrival fires a mode transition, and the new mode. The clause *in modes* indicates which subcomponents and connections are active in a given mode. Connections can also be active during mode transitions.

An AADL model is a tree of components, and each component has one or more operating modes. Thus, AADL uses the concept of *system operation mode* (SOM) to define the hierarchical composition of component modes. A SOM is a vector of modes (Bertrand et al., 2008), where each element is associated to a component. If a component is active, the associated element is valued with the *current mode* of the component. If a component is inactive, the associated element is tagged inactive.

A system has exactly one *initial SOM*, which is the set of initial modes of each component. *SOM transitions* define how a system transits from one SOM to another due to some stimulus. SOM transitions can be declared at each level, and extracting them from a set of mode state machines can be based on a breadth-first walk algorithm among the component tree (Bertrand et al., 2008). When a mode change is requested, a SOM transition is engaged. The new SOM is obtained from the old SOM, by changing the values of the vector elements that are involved in the mode change. In this paper, we mainly consider the relation between SOM transitions and threads/connections.

AADL offers two mode change protocols: *Emergency* and *Planned*. They differ on the instant where mode change actually occurs. The execution model attribute is attached to the mode transitions, and expressed as: Mode\_Transition\_Response  $\Rightarrow$ {*Emergency*, *Planned*}. To guarantee determinism, we consider the planned one.

#### 3.2.4. Behavior annex

The behavior annex can be used to describe a set of legal behaviors for a thread or a subprogram. It is described using a transition system with annotated *states*: *initial* specifies a start state, *return* specifies the end of a subprogram, *complete* specifies completion of a thread, and zero or more intermediate execution states. *Transitions* define system transitions from a *source* state to a *destination* state. Transitions may be guarded by *conditions* and trigger *actions*. Conditions and actions include sending or receiving messages, assigning variables and execution abstractions such as use of CPU time or delay, etc. Here, the specification of dispatch conditions for sporadic or aperiodic threads, and shared data communication, which imply loss of determinism, are excluded.

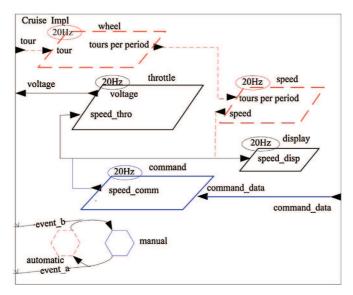

An AADL example. A simplified example of an Electronic Throttle Controller (ETC) (Ouimet et al., 2006) within our chosen subset is given (Fig. 2). A car may cruise automatically or be controlled by the driver at different speeds. The system is split into a system component, a process component (Cruise), and several thread components (wheel, throttle, speed, command, display). We focus on the modes of the process component, which contains two modes (automatic, manual). In the manual mode, the command component reads data from the driver, the throttle computes the voltage used to control the car, and display the speed parameter. When detecting the event\_a, the process switches to automatic mode. In the automatic mode, the tasks wheel and speed are released, command is deleted, throttle and display continue to execute. The speed component reads the tours of the wheel and computes the speed, then sends it to the throttle for controlling the car. These threads are periodic with data port connections, and each thread has a behavior annex specification.

Fig. 2. Architecture of the electronic throttle controller system.

We show the *Cruise* process and the *throttle* thread as an example and a part of the textual specification is given in Fig. 3. The behavior of the *throttle* thread is made very simple here: the computed voltage is the difference between the wanted speed and the current speed.

#### 3.3. Abstract syntax of the subset of AADL

We give the abstract syntax of the considered subset: an AADL model contains several threads, connections, and a SOM automaton. Each thread with its behavior annex belongs to a given SOM, and each connection can belong to a SOM or to a SOM transition. Here, the structural elements and the execution model attributes are expressed in an uniform abstract syntax.

Please notice that: (1) DURATION is a predefined type, EXPRESSION describes the expression language used in the annex and is not given here, VALUE is a type describing all possible values stored in ports, BASTATE and SOM are enumerations extracted from the actual AADL model; (2) the action language of the annex being complex, we abstract it as a function computing outputs from the value of its input ports. The CPU consumption of an action is directly modelled as a *Time* attribute.

```

Listing 1 The abstract syntax of the synchronous subset of AADL.

Type Thread:=

{ Iports: set of PORT; \ * Input Ports * \

Oports: set of PORT; \ * Output Ports * \

Period: DURATION;

BCET: DURATION;

WCET: DURATION;

Deadline: DURATION;

Behavior: BehaviorAnnex;

Modes: set of SOM;

Type Connection:=

{ SrcThread: Thread; \ * Source Thread * \

DstThread: Thread; \ * Destination Thread * \

SrcPort: PORT; \ * Source Port * \

DstPort: PORT; \ * Destination Port * \

ConnectionType: {Immediate, Delayed};

Modes: set of SOM;

\mathbf{Type} \ \mathrm{BehaviorAnnex}{:=}

{ States: set of BASTATE;

Transitions: set of BA_Transition;

Type BA_Transition:=

{ SrcState: BASTATE; \ * Source State * \

DstState: BASTATE; \ * Destination State * \

Time: DURATION;

Guard: EXPRESSION;

Computation:((Iports(th) \rightarrow VALUE) \times Oports(th)) \rightarrow VALUE;

Type SOM_Transition:=

{ SrcMode: SOM; \ * Source Mode * \

DstMode: SOM; \ * Destination Mode * \

MCR_Th: Thread;

MCR_Port: Oports(MCR_Th);

Type Model:=

{ Threads: set of Thread;

Connections: set of Connection;

Initial_Mode: SOM;

Mode_Transitions: set of SOM_Transition;

```

# 4. Timed Abstract State Machine

In this section, we first introduce the basic concepts of the TASM language, then we give its abstract syntax.

```

process implementation Prc_Cruise.impl

subcomponents

wheel: thread Th_wheel.impl in modes (automatic);

command: thread Th_command.impl in modes (manual);

connections

data port tour -> wheel.tour in modes (automatic);

manual: initial mode;

automatic: mode;

manual -[ event_a \rightarrow automatic;

automatic -[ event_b] \rightarrow manual;

end Prc_Cruise.impl;

thread implementation Th_throttle.impl

properties

Dispatch_Protocol => Periodic;

Period => 50ms:

Compute_Execution_Time => 15ms..15ms;

Deadline => 50ms;

annex behavior_specification **

states

s0: initial complete state;

transitions

s0 -[\rightarrow s0 \ \{computation(15ms); voltage:= speed_through

- current_speed };

** };

end Th_throttle.impl;

```

Fig. 3. A part of textual specification of the AADL model of the ETC system.

#### 4.1. A brief introduction to TASM

TASM extends the Abstract State Machine (Börger, 2002) to enable the expression of timing and resource consumption. A basic definition of a TASM specification is given as follows:

#### **Definition 5 (A TASM specification).** A TASM specification is a pair $\langle E, ASM \rangle$ where:

- $E = \langle EV, TU, ER \rangle$  is the environment, including:

- EV denotes the Environment Variables, which are the global variables that affect and are updated by machine execution,

- TU is the Types of environment variables that include integer, boolean, and user-defined types,

- ER is the set of named Resources,  $ER = \{(rn, rs)|rn$  is a resource name, and rs is the resource size}. Examples of resources include memory, power, bus bandwidth, etc.

- $ASM = \langle MV, CV, IV, R \rangle$  is a machine, including:

- MV denotes the Monitored Variables, which are the set of environment variables that affect the machine execution,

- CV denotes the Controlled Variables, which are the set of environment variables that the machine updates,

- *IV* denotes the *Internal Variables*, which are the set of local variables, and their scope being limited to the machine where they are defined.

- R is the set of Rules, R = { (n, t, RR, r) | n is the rule name; t is the duration of the rule execution, which can take the form of a single value, an interval [t<sub>min</sub>, t<sub>max</sub>], or the keyword next, the "next" construct essentially states that time should elapse until an event of interest occurs, which is especially helpful for a machine which has no enabled rules, but which does not wish to terminate; RR is the resource consumption during the rule execution with the form rn:=rs; r is a rule of the form "if condition then action", where condition is an expression depending on the monitored variables, and action is a set of updates of the controlled variables. We can also use the rule "else then action".}. A restriction on the set of rules is that they are mutually exclusive, that is, only one rule can be executed at each step.

The concepts of hierarchical composition, parallelism, and communication are also supported by TASM. It uses a set of *main machines* that execute in parallel, to support the specification of parallel behaviors, and provides *sub-machine* and *function-machine* calls to support the specification of hierarchical behaviors. Communications are only between main machines and can use channel synchronization and shared variables

Simply, the semantics of a main machine can be given as follows: read the shared variables, select a rule of which condition is satisfied, wait for the duration of the execution while consuming the resources, and apply the update set. If there are communications with other machines, it also needs to synchronize.

We give a simplified TASM specification of the *throttle* thread in the example of Section 3 (Fig. 4), and we assume power and memory are consumed during the execution. *Rule1* defines the actual execution of the thread. *Rule2* is triggered at completion and updates the thread state at the next dispatch. Notice that this TASM translation of an AADL thread is correct only if the thread execution time is exactly known and no other threads have access to the processor. The actual translation will need two TASM machines (see Section 5).

```

ENVIRONMENT:

USER-DEFINED TYPES:

State:= {dispatch,completed};

RESOURCES:

Power:=[0,100]; Memory:=[0,100];

VARIABLES:

State CurrentState:= dispatch;

MAIN MACHINE Throttle

MONITORED VARIABLES:

CurrentState;

CONTROLLED VARIABLES:

CurrentState:

RULES:

Rule1: execution

\{ t := 15;

Power:= [5,10];

Memory:= [20,50];

if CurrentState = dispatch then

CurrentState:= completed;

Rule2: next_period

\{ t := 35;

if CurrentState = completed then

CurrentState:= dispatch;

```

Fig. 4. A TASM example.

#### 4.2. Abstract syntax of TASM

The abstract syntax of TASM is given as follows:

```

P ::= x := \exp \\ | skip \\ | if Bexp then P \\ | else then P \\ | time (t_{\min}, t_{\max}) \rhd P \\ | time next \rhd P \\ | resource r (r_{\min}, r_{\max}) \rhd P \\ | P \oplus P \\ | P \otimes P \\ TASM ::= \langle E, P || P || \cdots || P \rangle

```

In this paper, we use shared variables to achieve communication. P defines the behaviors of a main machine, x := exp updates the value of the controlled variable x, time specifies the duration of P, resource specifies the resource usage during the execution of P, r is the name of a resource,  $P \oplus P$  is the choice operator that connects several rules within a main machine,  $P \otimes P$  is a synchronous parallel operator which connects statements within rule actions, the statements must not update the same variables, and P||P| is a parallel operator which connects main machines. Composition is synchronous if updates are simultaneous, else asynchronous.

To get a complete formalization of TASM, an interested reader can refer to (Ouimet and Lundqvist, 2006).

# 5. Two formal semantics for the subset of AADL

In order to enable the proof of semantics preservation of the model transformation, the informal execution semantics of the subset of AADL formalized directly using TTS, is considered as a reference semantics, because we cannot directly prove that the translational semantics is equivalent with the informal one which is provided by the AADL standard. As the behavior is explicitly expressed by atomic transitions, the TTS-based semantics is easy to understand. However, TTSs are mainly a mathematical model which cannot be used to automatically verify properties of a given AADL model. TASM-based translational semantics (for verification purpose) is more complex than the TTS-based one, because we need to know the rather complex TASM semantics to understand the translated TASM sentences. In this paper, the TTS-based semantics is supposed to be correct, and it gives a reference expression of AADL semantics which can be compared with the TASM-based translational semantics.

The TTS-based semantics will be defined as a synchronous product of TTSs communicating through a global state (shared variables). For this purpose, each TTS can leave some variables unspecified, and these variables are assigned by other parallel TTSs; other variables will be modified using the record update notation s' = s with  $\{\cdots\}$ . So, variables not present in the record update and not declared as unspecified are supposed to be unchanged. Furthermore, in order to avoid deadlocks, we suppose that each deadlock state has a default transition

which lets all the variables unchanged. Moreover, as communication between TTSs relies on shared variables, discrete labels are not used and considered to be  $\tau$ , that is  $\Sigma = \{\tau\}$ .

As mentioned in Section 3.3, an AADL model (m) contains several threads, connections, and a SOM automaton. Each thread (th) with its behavior annex belongs to a given SOM, and each connection (cn) can belong to a SOM or to a SOM transition (tr). Concretely speaking, the operational semantics of a periodic thread with data port communications is defined as the synchronous product of two TTSs:  $TTS_{thread\_basic}$  and  $TTS_{dispatcher}$ , while the computation of the thread will be refined by the behavior annex. For an immediate connection, the execution of the recipient thread is suspended until the sending thread completes its execution when the dispatches of sender and receiver threads are simultaneous. We use an abstract scheduler to manage it and the scheduler only ensures the static alignment of thread execution order implied by the immediate connection. The operational semantics of the scheduler is defined as  $TTS_{scheduler}$ . The operational semantics of the SOM automaton is defined as  $TTS_{mode\_change}$ . Thus, the operational semantics of the considered subset of AADL is the composition of a set of TTSs. The definitions of these TTSs will be given later.

Here, we first define the sets  $S^G$  and  $I^G$ .

• The global state is defined by the partial valuation of a set of variables. An *IportBuffer* variable is defined for each input port of each thread. The sender copies values of output ports to the buffer, and the recipient copies values from the buffer to the input ports. Each *IportBuffer* is associated to a boolean variable *NewData* which is true when the input buffer has got the latest data. It is used to guarantee the deadline of the sender occurs before the dispatch of the recipient when they are logically simultaneous and the connection type between them is Delayed. *CurrentTime* represents the global current time.

```

S^G = \{ \begin{array}{ll} & \text{CurrentMode}: SOM, \\ & \text{Activation\_TH}(th): \{true, false\}, \\ & \text{Activation\_CN}(cn): \{true, false\}, \\ & \text{State}(th): \{ \ waiting\_mode, waiting\_dispatch, \\ & \ waiting\_execution, execution, \\ & \ computed, completed\}, \\ & \text{Dispatch}(th): \{true, false\}, \\ & \text{Get\_CPU}(th): \{true, false\}, \\ & \text{Iport}(th): \text{Iports}(th) \rightarrow VALUE, \\ & \text{Oport}(th): \text{Oports}(th) \rightarrow VALUE, \\ & \text{IportBuffer}(th): \text{Iports}(th) \rightarrow VALUE, \\ & \text{NewData}(th): \text{Iports}(th) \rightarrow \{true, false\}, \\ & \text{DispatchTime}(th): DURATION, \\ & \text{CurrentTime}: DURATION\}. \end{array}

```

```

• I^G = \{ \text{ CurrentMode} \mapsto Init\_Mode(m), \\ \text{Activation\_TH} \mapsto \left\{ \begin{array}{l} th \mapsto true \mid Init\_Mode(m) \in Modes(th) \\ th \mapsto false \mid Init\_Mode(m) \not\in Modes(th) \end{array} \right\},

\text{Activation\_CN} \mapsto \left\{ \begin{array}{l} cn \mapsto true \mid Init\_Mode(m) \notin Modes(cn) \\ cn \mapsto false \mid Init\_Mode(m) \notin Modes(cn) \end{array} \right\},

\text{State}(th) \mapsto waiting\_mode,

\text{Dispatch}(th) \mapsto false,

\text{Get\_CPU}(th) \mapsto false,

\text{Iport}(th) \mapsto \{ip \mapsto 0 \mid ip \in \text{Iports}(th)\},

\text{Oport}(th) \mapsto \{op \mapsto 0 \mid op \in \text{Oports}(th)\},

\text{IportBuffer}(th) \mapsto \{ip \mapsto 0 \mid ip \in \text{Iports}(th)\},

\text{NewData}(th) \mapsto \{ip \mapsto true \mid ip \in \text{Iports}(th)\},

\text{DispatchTime}(th) \mapsto 0,

\text{CurrentTime} \mapsto 0\}.

```

Here, messages exchanged by threads are supposed to be of type Integer.

As the analysis of AADL in Section 3, the translational semantics should take into account the structural aspect, the execution model and the behavior annex. The semantics function has two parts: the mapping of the structural aspect to the TASM environment (such as thread-related variables, connection-related variables, and mode-related variables), and the mapping of the dynamic aspect to the TASM

machines (such as the execution of threads, connections, mode change and the behavior annex). The auxiliary functions, for example  $Trans\_Thread(th)$  and  $Trans\_Thread(th)$ , will be defined later.

```

Translate(m:Model) =

U

Trans\_ThreadData(th)

th \in Threads(m)

Trans\_BehaviorAnnexData(th))

U

th \in Threads(m)

Trans\_ConnectionData(cn))

IJ

cn \in Connections(m)

[] Trans_ModeData,

||_{th \in Threads(m)} Trans\_Thread(th)|

\| (\|_{th \in Threads(m)} \ Trans\_BehaviorAnnex(th)) \|

\| (\|_{cn \in Connections(m)} Trans\_Connection(cn)) \|

\parallel Trans\_Scheduler

\parallel Trans\_Mode \rangle

```

We will give the informal interpretation, the operational semantics using TTSs, and the translational semantics by translating into TASM of the subset of AADL in a modular manner.

#### 5.1. Periodic threads with data port communications

#### 5.1.1. Informal interpretation

The *current mode* determines the set of threads that are considered *active*. Only the active threads can be dispatched and scheduled for execution and other threads are in the *waiting mode* state or the *halted* state.

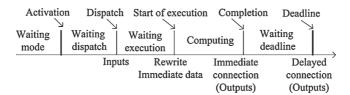

*Periodic threads*. A periodic thread is dispatched periodically, and its inputs received from other threads are frozen at dispatch time (by default), i.e. at time zero of the period. As a result the computation performed by a thread is not affected by the arrival of new inputs. Similarly, the outputs are made available to other threads at completion or deadline time, depending on the connection.

Data port communications between periodic threads. First, the communication affects the input/output timing of the periodic threads. (1) For an immediate connection, the execution of the recipient is suspended until the sender completes its execution. As mentioned above, the inputs have been copied at dispatch time, so the recipient needs to replace the old data using the data got from the sender at the start of execution. (2) For a delayed connection, the value from the sender is transmitted at its deadline and is available to the recipient at its next dispatch. The recipient just needs the last dispatch data from the sender. Second, the immediate connection implies a static alignment of thread execution order, i.e., it deals with the scheduling of the sending of messages and the processing of the received messages.

In conclusion, the time line of a periodic thread with data port communications is represented in Fig. 5.

#### 5.1.2. Operational semantics

Now we give the operational semantics of a periodic thread (th) with data port communications, which is defined as the synchronous product of two TTSs:  $TTS_{thread\_basic}$  and  $TTS_{dispatcher}$ .

**Definition 6** ( $TTS_{thread,basic}$ ). The basic behavior of a periodic thread (th) with data port communications is a timed transition system defined over  $S^G$  and  $I^G$ , that is  $TTS_{thread,basic} = \langle S^L, I^L, \Sigma, \rightarrow \rangle$  where:

•  $S^L = \{ StartofExeTime(th) : DURATION \}.$

As mentioned above, for an immediate connection, the execution of the recipient is suspended until the sender completes its execution. So we save the start time of execution of the thread.

- $I^L = \{ StartofExeTime(th) \mapsto 0 \}.$

- $\Sigma = \{\tau\}.$

- $\rightarrow$  is defined by the following rules, including discrete transitions and continuous transitions. s and s' are values of the type  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$ . While  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$  in  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$  in  $S(S = S^G \times S^L)$  in  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ . The shared variables  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$  in  $S(S = S^G \times S^L)$  in  $S(S = S^G \times S^L)$  is  $S(S = S^G \times S^L)$ .

Fig. 5. The time line of an AADL periodic thread with data port communications.

**ACTIVATION**. Two rules are used to deal with the relation between the periodic thread *th* and mode change (in Section 5.3). A shared variable Activation \_TH(*th*): {*true*, *false*} is used. ACTIVATION[1] means the thread is in the current mode, while ACTIVATION[2] represents the thread waits to be active. The delay is controlled by the TTS associated to the mode change.

```

s(State(th)) = waiting\_mode,

s(Activation\_TH(th)) = true,

s' = s \text{ with } \{State(th) = waiting\_dispatch\} \\ \hline s \rightarrow s' \\ - ACTIVATION[1]

s(State(th)) = waiting\_mode,

s(Activation\_TH(th)) = false,

s' = s \text{ with } \{CurrentTime = \\ s(CurrentTime) + d\} \\ \hline - \frac{s(CurrentTime) + d}{s \xrightarrow{d} s'} \\ - ACTIVATION[2]

```

**DISPATCH**. The rule DISPATCH[1] represents the dispatch of a thread. On the dispatch event, the input ports are read. For this purpose, we must wait for the data transfer made by the sender threads through delayed connections when their deadline occurs at the same logical time as the dispatch of the recipient thread. This condition is defined by the *DelayedSyncCond* predicate. As mentioned in Section 3.2, the thread can trigger mode change requests (MCRs) by raising an event. Here we use the same ports for data and event, and say that event is a value satisfying the *isEvent* predicate. The event buffer can be reset by writing the *None* value. This is done at dispatch time. The rule DISPATCH[2] represents the thread waits to be dispatched. The delay is controlled by the TTS associated to the dispatcher.

```

s(State(th)) = waiting\_dispatch,

s(Dispatch(th)) = true,

DelayedSyncCond(th, s),

s' = s with {

State(th) = waiting\_execution,

DispatchTime(th) = s(CurrentTime),

Iport(th) = \{ip \mapsto s(IportBuffer(th, ip)) \mid ip \in Iports(th)\},\

||_{ip \in Iports(th)} \underbrace{NewData(th, ip)}_{Oports(th)|isEvent(s(Oport(th, op)))} Oport(th, op) = None

_____DISPATCH[1]

where DelayedSyncCond(th, s) \equiv

\forall cn \in Connections(m),

s(DispatchTime(SrcThread(cn))) +

Period(SrcThread(cn)) = s(CurrentTime)

\land DstThread(cn) = th

\land \ ConnectionType(cn) = Delayed

\Rightarrow s(NewData(th, DstPort(cn))) = true

s(State(th)) = waiting\_dispatch,

s(Dispatch(th)) = false,

s' = s \text{ with } \{CurrentTime = s(CurrentTime) + d\}

s \xrightarrow{d} s'

DISPATCH[2]

```

**WAITING\_EXE**. When the thread is dispatched, its execution is managed by a scheduler. Specially, in presence of immediate connection, the scheduler must ensure that the sender completes before the start of execution of the recipient. Moreover, ports of which incoming connection is immediate must be rewritten. The rule WAITING\_EXE[1] means that the thread gets CPU, while the rule WAITING\_EXE[2] represents the thread waits to be scheduled. The delay is controlled by a TTS associated to the scheduler (in Section 5.2).

```

s(State(th)) = waiting\_execution, \\ s(Get\_CPU(th)) = true, \\ s' = s \text{ with } \{ \\ State(th) = execution, \\ Iport(th) = s(Iport(th)) \Leftrightarrow \\ \{ip \mapsto s(IportBuffer(th, ip)) \mid \text{isImmediate}(th, ip)\}, \\ StartofExeTime(th) = s(CurrentTime) \\ \\ \} \\ \hline \\ s \mapsto s' \\ WAITING\_EXE[1]

```

where isImmediate (th, ip) checks if the input port ip of thread th is the destination of an immediate connection. This predicate is defined as follows:

```

\exists cn \in Connections(m), DstPort(cn) = ip \\ \land ConnectionType(cn) = Immediate \\ \land ip \in Iports(th)

```

```

s(State(th)) = waiting\_execution,

s(Get\_CPU(th)) = false,

s' = s \text{ with } \{CurrentTime = s(CurrentTime) + d\}

\xrightarrow{s \xrightarrow{d} s'} WAITING\_EXE[2]

```

**EXECUTION**. Here, the execution is abstracted by a function  $Computation (Inputs:Iports(th) \rightarrow VALUE): Oports(th) \rightarrow VALUE which consumes CPU time during the interval [BCET, WCET] of the thread, and it will be refined by the AADL behavior annex (in Section 5.4). The rule EXECUTION[1] represents that the thread is in the progress of its execution. The rule EXECUTION[2] is used to write the computation results into the output ports of the thread.$

```

s(State(th)) = execution,

s(CurrentTime) - s(StartofExeTime(th)) + d \leq WCET(th),

s' = s \text{ with } \{CurrentTime = s(CurrentTime) + d\}

= s(State(th)) = execution,

BCET(th) \leq (s(CurrentTime) - s(StartofExeTime(th))) \leq WCET(th),

s' = s \text{ with } \{State(th) = computed,

Oport(th) = ||_{op \in Oports(th)} Computation

(\{ip \mapsto s(Iport(th)) \mid ip \in Iports(th)\}, op)

= execution

EXECUTION[2]

```

**WRITE\_IMM\_DATA.** It is used to copy the data of the output ports of the sender to the *IportBuffer* of the recipient at the completion time of the sender. This copy is only done when the two threads are dispatched at the same time.

WAITING\_DEADLINE. This rule is used to wait for the deadline (i.e. the period here for the sake of simplicity) of the thread.

```

\begin{split} s(State(th)) &= completed, \\ s(Get\_CPU(th)) &= false, \\ s(CurrentTime) + d \\ &\leq s(DispatchTime(th)) + Period(th), \\ s' &= s \text{ with } \{CurrentTime = s(CurrentTime) + d\} \\ \hline & s \xrightarrow{d} s' \end{split}

```

**Definition 7** ( $TTS_{dispatcher}$ ). The behavior of the dispatcher of a periodic thread (th) is a timed transition system defined over  $S^G$  and  $I^G$ , that is  $TTS_{dispatcher} = \langle S^L, I^L, \Sigma, \rightarrow \rangle$  where:

- *S<sup>L</sup>* = {WaitNextDispatch(*th*): {*true*, *false*}}. Here, an auxiliary variable WaitNextDispatch(*th*) is used.

- $I^L = \{ \text{WaitNextDispatch}(th) \mapsto false \}.$

- $\Sigma = \{\tau\}$ .

- → is defined by the following rules. The shared variables State(th), IportBuffer(th), NewData(th), Dispatch(th) and CurrentTime will be modified by this TTS, while others are declared as unspecified.

**DISPATCH\_THREAD**. This rule is used to dispatch the thread, and synchronize with the thread using the shared variable Dispatch(*th*).

```

s(Activation\_TH(th)) = true,

s(State(th)) = waiting\_dispatch,

s(Dispatch(th)) = false,

s' = s \text{ with } \{Dispatch(th) = true,

WaitNextDispatch(th) = true\}

s \rightarrow s'

DISPATCH\_THREAD

```

WAITING\_PERIOD. This rule does nothing, and it is just used to wait the period of the thread.

```

s(WaitNextDispatch(th)) = true, \\ s(CurrentTime) + d \\ \leq s(DispatchTime(th)) + Period(th), \\ s' = s \text{ with } \{CurrentTime = s(CurrentTime) + d\} \\ \hline \\ s \xrightarrow{d} s'

WAITING\_PERIOD

```

**REACH\_PERIOD**. This rule represents that the thread arrives at its period. The output of the delay connections is also expressed in this rule, namely, copy the data of the output ports of the sender to the *IportBuffer* of the recipient at the deadline of the sender. We also set the *NewData* variable to true in order to indicate the data transfer has been done.

```

s(WaitNextDispatch(th)) = true, \\ s(CurrentTime) = s(DispatchTime(th)) + Period(th), \\ s' = s \text{ with } \{ \\ State(th) = waiting\_mode, \\ WaitNextDispatch(th) = false, \\ Dispatch(th) = false, \\ IportBuffer = IportBuffer \Leftrightarrow \\ \{DstThread(cn) \mapsto s(Oport(th))\} \mid \text{isDelayOut}(th), \\ NewData(DstThread(cn)) = true \\ \} \\ \hline \qquad \qquad \qquad REACH\_PERIOD

```

where is DelayOut(th) checks if the thread th is the source thread of a delayed connection. This predicate is defined as follows:

```

\exists cn \in Connections(m), \quad SrcThread(cn) = th \\ \land ConnectionType(cn) = Delayed

```

WAIT. This rule is used to deal with the waiting time when the conditions of other rules are not satisfied.

```

s(Activation\_TH(th)) = false,

s' = s \text{ with } \{CurrentTime = s(CurrentTime) + d\}

s \xrightarrow{d} s'

WAIT

```

#### 5.1.3. Translational semantics

The TASM environment associated to each thread is defined as a set of typed variables such as the *state* and the *resource consumption* of the thread. Messages exchanged by threads are supposed to be of type Integer. The variables associated to connections are defined as well.

```

Listing 2 The TASM environment of an AADL periodic thread with data port communications.

Trans_ThreadData(th)=

{ State: {waiting_mode, waiting_dispatch, waiting_execution, execution, computed, completed} := waiting_mode;

Iport:Iports(th) → Integer;

Oport:Oports(th) → Integer;

RscUsage:RESOURCE → Integer;

WaitNextDispatch:Boolean;

...

}

```

The dynamic behavior of a periodic thread with data port communications is defined as two TASM machines in parallel: *TASM\_Thread(th)* and *Periodic\_Dispatcher(th)*, as shown in Listing 3.

- A periodic thread (th) is expressed by TASM\_Thread(th) with six rules: Activation, Dispatch, Waiting Execution, Execution, Write Immediate Data, and Waiting Next Event. In the rule Execution, the duration of execution is [BCET, WCET] and processor consumption is 100%. The rule Waiting Next Event is used to deal with the waiting time when activation, dispatch and execution conditions are not satisfied. Additionally, the behavior of a connection is separated in two parts: Read and Write.

- The dispatcher of a periodic thread (th) is expressed by Periodic\_Dispatcher(th) with three rules: Dispatch Thread, Waiting Period, and Waiting Next Event. The rule Waiting Period corresponds to the rules WAITING\_PERIOD and REACH\_PERIOD of TTS\_dispatcher (Definition 7). According to the TASM semantics (Section 4.1), the system will wait for the duration of the execution of the rule, then apply the update set (i.e. actions). Thus, the TASM-based translational semantics hides implicit behaviors provided by the TASM semantics.

Translation rules are written using an ML-like language (close to the Coq notations) with bold font keywords as follows. References to other TASM machines are also bold.

- **LET** name = P **AND** . . . **IN** TASM.

- **IF** condition **THEN** P **ELSE** P.

```

Listing 3 The TASM machines of an AADL periodic thread with

data port communications.

Trans_Thread(th) =

\mathbf{LET} \; \mathrm{TASM\_Thread}(\mathrm{th}) =

// Rule Activation

Time 0 ▷ (if State(th)=waiting_mode and Activation_TH(th)=true then

State(th):=waiting_dispatch)

⊕ //Rule Dispatch

Time 0 ▷ (if State(th)=waiting_dispatch and Dispatch(th)=true then

State(th):=waiting_execution

⊗ Iport(th):=IportBuffer(th)

\bigotimes_{op \in Oports(th)|isEvent(Oport(th,op))}

Oport(th,op) := None)

\oplus //Rule Waiting Execution

Time 0 ▷ (if State(th)=waiting_execution and Get_CPU(th)=true then

State(th):=execution \otimes Trans_Connection_Read(th))

⊕ //Rule Execution

Time (BCET(th), WCET(th)) \triangleright Resource Processor 100 \triangleright

(if State(th)=execution then

Oport(th):=Computation(Iport(th)) \otimes State(th):=computed)

⊕ //Rule Write Immediate Data

Time 0 \triangleright (if State(th)=computed then

State(th):=completed \otimes Trans_Connection_Write_Imm(th))

⊕ //Rule Waiting Next Event

Time next \triangleright (else then

skip)

```

```

AND Periodic_Dispatcher(th)=

//Rule Dispatch Thread

time 0

(if Activation_TH(th)=true and State(th)=waiting_dispatch

and Dispatch(th)=false then

Dispatch(th):=true \otimes WaitNextDispatch(th):=true)

⊕ //Rule Waiting Period

time Period(th) ▷ (if WaitNextDispatch(th)=true then

WaitNextDispatch(th):=false

⊗ Trans_Connection_Write_Delay(th)

\otimes State(th):=waiting_mode

\otimes Dispatch(th):=false)

⊕ //Rule Waiting Next Event

time next \triangleright (else then

skip)

IN TASM_Thread(th) || Period_Dispatcher(th)

Trans\_Connection\_Read(th) =

ip:=IportBuffer(th,ip)

ip \in Iports(th)

\land cn \in Connections(m)

\wedge DstPort(cn) = ip

\land ConnectionType(cn) = Immediate

Trans_Connection_Write_Imm(th)=

IportBuffer(DstThread(cn),DstPort(cn)):=op

op \in Oports(th)

\land cn \in Connections(m)

\land SrcPort(cn) = op

\land ConnectionType(cn) = Immediate

Trans_Connection_Write_Delay(th)=

IportBuffer(DstThread(cn),DstPort(cn)):=op

op \in Oports(th)

\land cn \in Connections(m)

\land SrcPort(cn) = op

\land ConnectionType(cn) = Delayed

```

#### 5.2. Scheduler

# 5.2.1. Informal interpretation

As mentioned above, in presence of immediate connection, the scheduler must ensure that the sender completes before the start of execution of the recipient. Here, we give an abstract view of the scheduler. The given behavior allocates the CPU to a waiting thread *th* of which immediate data emitters that have been synchronously dispatched with *th* have completed their task.

# 5.2.2. Operational semantics

**Definition 8** ( $TTS_{scheduler}$ ). The behavior of the scheduler is a timed transition system defined over  $S^G$  and  $I^G$ , that is  $TTS_{scheduler} = \langle S^L, I^L, \Sigma, \rightarrow \rangle$  where:

- $S^L = \emptyset$ .

- $I^L = \emptyset$ .

- $\Sigma = \{\tau\}$ .

- $\rightarrow$  is defined by the following rules. The shared variables Get \_CPU(th) will be modified by this TTS, while others are declared as unspecified.

# ALLOCATE\_CPU. This rule is used to allocate the CPU to a waiting thread.

```

s(State(th)) = waiting\_execution,

\forall th' \in Threads(m)

s(Get\_CPU(th')) = false,

\forall cn \in Connections(m)

ConnectionType(cn) = Immediate

\land DstPort(cn) \in Iports(th)

\land s(DispatchTime(th)) = s(DispatchTime(SrcThread(cn)))

\rightarrow s(State(SrcThread(cn))) \in \{completed, waiting\_mode\},

s' = s \text{ with } \{Get\_CPU(th) = true\}

s \rightarrow s'

ALLOCATE\_CPU

```

FREE\_CPU. This rule frees the CPU allocated to a thread which has completed its task.

```

s(Get\_CPU(th)) = true,

s(State(th)) = completed,

s' = s \text{ with } \{Get\_CPU(th) = false\}

s \to s'

FREE\_CPU

```

#### 5.2.3. Translational semantics

The scheduler should avoid giving the processor to several threads at the same time. Its behavior is defined as a TASM machine with three rules: *Allocate CPU*, *Free CPU*, and *Waiting Next Event*.

```

Listing 4 The TASM machine of the scheduler.

Trans_Scheduler=

// Rule Allocate CPU

Time 0 \triangleright (if State(th)=waiting_execution

\bigwedge_{th' \in Threads(m)} (\widetilde{\operatorname{Get\_CPU}}(\operatorname{th'}) = \operatorname{false})

ConnectionType(cn) = Immediate

\land DstPort(cn) \in Iports(th)

\land DispatchTime(th)

= DispatchTime(SrcThread(cn))

\land State(SrcThread(cn))

\in \{completed, waiting\_mode\}

then

Get_CPU(th):=true)

\oplus //Rule Free CPU

Time 0 \triangleright (if State(th)=completed and Get_CPU(th)=true then

Get_CPU(th):=false

⊕ //Rule Waiting Next Event

Time next \triangleright (else then

skip)

```

# 5.3. Mode change

# 5.3.1. Informal interpretation

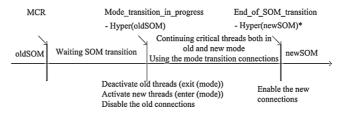

The behaviors of a SOM transition. The AADL mode change protocol comprises two phases: (1) waiting SOM transition; (2) SOM transition. In this paper, we consider the planned one. Fig. 6 shows the time line of an AADL SOM transition.

At the beginning, the system is in the source mode of a SOM transition (i.e. oldSOM). After a mode change request (MCR) has occurred, execution continues under the oldSOM until the dispatches of a set of critical threads that are active align at their hyper-period (called Hyper(oldSOM)), then the mode\_transition\_in\_progress state is entered. A periodic thread is considered as critical if its Synchronized\_Component property is true. That means, the duration from the oldSOM state to the mode\_transition\_in\_progress state is the distance to the next hyper-period of these critical threads.

In the *mode\_transition\_in\_progress* state, some threads enter the new mode (become active), some threads exit the old mode, the critical threads of both new and old modes continue to execute, and the connections belong to *oldSOM* will be deleted. The system is in the *mode\_transition\_in\_progress* state for a limited amount of time, which is the distance to a multiple of the hyper-period of the critical threads that continue to execute (called *Hyper(newSOM)\**). Finally, the system enters the destination mode of the SOM transition (i.e. *newSOM*).

When a MCR is responded, all of the other incoming MCRs will be ignored, and we don't consider the higher priority requests here.

Fig. 6. The time line of an AADL SOM transition.

#### 5.3.2. Operational semantics

Now, we give the operational semantics of the SOM automaton of the AADL model (m).

**Definition 9** ( $TTS_{mode\_change}$ ). The behavior of the SOM automaton is a timed transition system defined over  $S^G$  and  $I^G$ , that is  $TTS_{mode\_change} = \langle S^L, I^L, \Sigma, \rightarrow \rangle$  where:

```

\bullet \ S^L = \left\{ \begin{array}{l} \mathsf{ModeTransitionInProgress} : \{\mathit{true}, \mathit{false}\}, \\ \mathsf{GetMCR}(\mathit{tr}) : \{\mathit{true}, \mathit{false}\} \\ \mathsf{Here}, \ \mathsf{two} \ \mathsf{auxiliary} \ \mathsf{variables} \ \mathsf{are} \ \mathsf{used}. \\ \bullet \ \mathit{I}^L = \left\{ \begin{array}{l} \mathsf{ModeTransitionInProgress} \mapsto \mathit{false}, \\ \mathsf{GetMCR}(\mathit{tr}) \mapsto \mathit{false} \end{array} \right\}. \\ \bullet \ \Sigma = \{\tau\}. \end{aligned}

```

→ is defined by the following rules. The shared variables CurrentMode, Activation \_ TH(th), Activation \_ CN(cn), and CurrentTime will be modified by this TTS, while others are declared as unspecified.

**GET\_MCR**. This rule gets events sent by threads and selects a corresponding mode transition.

```

s(CurrentMode) = SrcMode(tr),

isEvent(s(Oport(th, op))),

MCR\_Th(tr) = th,

MCR\_Port(tr) = op,

s' = s \text{ with } \{

GetMCR(tr) = true\}

s \to s'

GET\_MCR

```

**ENTER\_MC\_PL**. This rule makes a random choice of one of the MCRs, other MCRs are disabled. The system goes to the *mode\_transition\_in\_progress* state, old threads and connections are deactivated, while new threads are activated.

```

s(CurrentMode) = SrcMode(tr), \\ s(GetMCR(tr)) = true, \\ s(CurrentTime) \ mod \ Hyper(CurrentMode) = 0, \\ s(ModeTransitionInProgress) = false, \\ s' = s \ \text{with} \ \{ \\ GetMCR = \{tr' \mapsto (tr = tr')\}, \\ Activation\_TH = \left\{ \begin{array}{c} th \mapsto true \mid DstMode(tr) \in Modes(th) \\ th \mapsto false \mid otherwise \end{array} \right\}, \\ Activation\_CN = \left\{ \begin{array}{c} cn \mapsto true \mid SrcMode(tr) \in Modes(cn) \\ cn \mapsto false \mid otherwise \end{array} \right\}, \\ ModeTransitionInProgress = true \} \\ S \rightarrow s' \\ ENTER\_MC\_PL

```

MC\_PL. This rule means that the system enters the new SOM.

```

s(ModeTransitionInProgress) = true, \\ s(GetMCR(tr)) = true, \\ s(CurrentTime) \ mod \ Hyper(DstMode(tr)) = 0, \\ s' = s \ \text{with} \ \{ \\ CurrentMode = DstMode(tr), \\ Activation\_CN = \left\{ \begin{array}{l} cn \mapsto true \mid DstMode(tr) \in Modes(cn) \\ cn \mapsto false \mid otherwise \end{array} \right\}, \\ ModeTransitionInProgress = false, \\ GetMCR(tr) = false \} \\ \hline s \rightarrow s' \\ MC\_PL

```

#### 5.3.3. Translational semantics

In the TASM environment, we introduce the *CurrentMode* variable valued in the set of SOM, and two booleans *ArriveHyperPeriod* and *ModeTransitionInProgress*.

```

Listing 5 The TASM environment of the SOM automaton.

Trans_ModeData=

{ CurrentMode: SOM;

ArriveHyperPeriod: SOM → Boolean;

ModeTransitionInProgress: Boolean;

...

}

```

The dynamic behavior of the SOM automaton is defined as two TASM machines in parallel: SOM\_Transition and Manage\_Hyper(mode).

- The basic behavior of the SOM automaton is expressed by SOM\_Transition with three rules: Get MCR, Mode Transition In Progress and Mode Transition. The machine uses the shared variable Activation \_ TH(th) to synchronize with the execution of periodic threads. The rule Get MCR gets events sent by threads and selects a corresponding mode transition. The rule Mode Transition In Progress expresses the behavior when waiting for the actual SOM transition after a MCR. The rule Mode Transition expresses the actual SOM transition.

- We use the machine Manage\_Hyper(mode) to manage the time Hyper(oldSOM) and Hyper(newSOM)\*.

```

Listing 6 The TASM machines of the SOM automaton.

Trans_Mode=

LET SOM_Transition=⊕ (

LET oldSOM=SrcMode(tr)

AND newSOM=DstMode(tr)

IN

//Rule Get MCR

time 0 \triangleright (if CurrentMode=oldSOM and

isEvent(Oport(MCR_Th(tr), MCR_Port(tr)))=true then

GetMCR(tr):=true)

⊕ //Rule Mode Transition In Progress

time 0 > (if CurrentMode=oldSOM and GetMCR(tr)=true

and ArriveHyperPeriod(oldSOM)=true

and ModeTransitionInProgress=false then

\otimes GetMCR(tr'):=false

\otimes ModeTransitionInProgress:=true

\otimes ArriveHyperPeriod(newSOM):=false

\otimes

Activation_TH(th):=true

th|newSOM \in Modes(th) \setminus oldSOM \in Modes(th)

\otimes

Activation_TH(th):=false

th|oldSOM\!\in\!Modes(th)\backslash newSOM\!\in\!Modes(th)

\otimes

Activation_CN(cn):=false)

cn|oldSOM\!\in\!Modes(cn)\backslash newSOM\!\in\!Modes(cn)

⊕ //Rule Mode Transition

time 0 \triangleright (if GetMCR(tr)=true and ModeTransitionInProgress=true

and ArriveHyperPeriod(newSOM)=true then

CurrentMode{:=}newSOM

Activation_CN(cn):=true

cn|newSOM \in Modes(cn) \setminus oldSOM \in Modes(cn)

\otimes \ ModeTransitionInProgress:=false\\

⊗ ArriveHyperPeriod(oldSOM):=false

\otimes \operatorname{GetMCR}(\operatorname{tr}) := \operatorname{false})

AND Manage_Hyper(mode)=

time Hyper(mode) \triangleright (if true then

ArriveHyperPeriod(mode):=true)

IN SOM_Transition \| (\|_{mode \in SOM} \text{ Manage\_Hyper(mode)})

```

#### 5.4. Behavior annex

AADL supports an input-compute-output model of computation and communication for threads. The input/output timing is defined by the execution model, and the computation can be refined by the behavior annex. So, there is a close relation between the AADL execution model and the behavior annex. The execution model specifies when the behavior annex is executed and on which data it is executed, while

the behavior annex acts in a thread (or a subprogram) and describes behaviors more precisely. Thus, the semantics specifications given as above will be enriched by the behavior annex.

#### 5.4.1. Informal interpretation

The behavior annex is described using a transition system in the following form:

State Variables represent the variables with the scope of the behavior annex, and they may hold the inputs, the intermediate results, and the outputs. States: initial specifies a start state, return specifies the end of a subprogram, complete specifies completion of a thread, and other states represent intermediate execution steps. Transitions define system transitions from a source state to a destination state. A transition can be guarded with execution conditions. An action part can be attached to a transition and it performs message sending, assignments or time consuming activities. However, the action part is related to the transition and not to the states: if a transition is enabled, the action part is performed and then the current state becomes the transition destination state. When the transition reaches a complete or return state, the thread or the subprogram will be completed.

#### 5.4.2. Operational semantics

The operational semantics of the behavior annex is defined as the refinement of the "Execution" rule of  $TTS_{thread,basic}$ , where the state  $S^L$  extends the semantics state of  $TTS_{thread,basic}$  with CurrentBAState and StartTransitionTime. The initial value of StartTransitionTime is the initial state of the behavior annex. StartTransitionTime is used to save the start time of the execution of the transition, and its initial value is the StartofExeTime of the thread.

**BA\_EXECUTION**. This rule expresses the execution of each transition of the behavior annex, and the *StartTransitionTime* is accumulated for each transition.

```

s(State(th)) = execution, \\ s(CurrentBAState) = SrcState(BA\_tr), \\ s(CurrentTime) = s(StartTransitionTime) + Time(BA\_tr), \\ s' = s \text{ with } \{ \\ CurrentBAState = DstState(BA\_tr), \\ Oport(th) = Action(BA\_tr)(Iport(th)), \\ StartTransitionTime = s(CurrentTime) \} \\ BA\_EXECUTION

```

if Guard(BA\_tr)=true,  $\forall BA\_tr \in Transitions(BA) \land BA = Behavior(th)$

**BA\_COMPLETE.** This rule means the execution of the behavior annex is completed. An auxiliary variable *isFinal* is used to denote the complete state of the behavior annex.

```

s(State(th)) = execution, \\ isFinal(s(CurrentBAState)) = true, \\ s' = s \text{ with } \{State(th) = computed\} \\ \hline s \rightarrow s' \\ BA\_COMPLETE

```

#### 5.4.3. Translational semantics

The translational semantics specification of the behavior annex contains three parts: structure, guards and actions.

Structure. State Variables are mapped to the TASM environment variables with general types such as integer, real numbers and booleans. States are translated into TASM internal variables. Each transition of the behavior annex is translated into a TASM rule. These rules will take the place of the "Execution" rule of the periodic thread.

In each TASM rule, the condition is built from the current state of the thread (State(th)), the source state of the transition, and the guards of the transition, while the actions of the rule include the actions of the transition and the destination state of the transition.

When all the transitions are translated, a new rule (*Behavior Annex Completion*) is added. Then the TASM machine executes the next rule (i.e. *Write Immediate Data*) of the periodic thread.

*Guards*. The execution conditions which are logical expressions based on the state variables are considered. Here, we do not detail the translation of behavior expressions. The corresponding function is denoted [Guard].

Actions. We mainly consider the basic actions including message sending, assignments to variables, and timing. (1) Message sending is expressed by the assignment of the port variables. (2) Assignments are expressed by the assignment of the corresponding environment variables. (3) The behavior annex introduces the statements computation(min,max) and delay(min,max), which express the use of the CPU and the suspension for a possibly non-deterministic period of time between min and max respectively. They are related to the transitions and not to the states, which is consistent with the TASM semantics. Thus, the timing actions are translated into the duration of the corresponding TASM rule.

In the TASM environment, we introduce the *CurrentBAState* variable valued in the set of states of the behavior annex and two booleans: *isInitial* and *isFinal*.

```

Listing 7 The TASM environment of the behavior annex of a periodic thread.

Trans_BehaviorAnnexData(th)=

{ CurrentBAState: BAState; isInitial: BAState → Boolean; isFinal: BAState → Boolean; ...

}

```

We consider all the transitions of the behavior annex of a periodic thread, and the basic semantics specification is presented in Listing 8. It can be detailed when more complex guards and actions are considered.

```

Listing 8 The TASM rules of the behavior annex of a periodic thread.

Trans_Thread(th) =

\oplus //Rule Execution

Trans_BehaviorAnnex(th)

\oplus //Rule Write Immediate Data

Trans_BehaviorAnnex(th) =

Time Time(BA_{tr}) \triangleright

BA = Behavior(th)

\land BA\_tr \in Transitions(BA)

(if State(th)=execution and CurrentBAState=SrcState(BA_tr)

and [ Guard(BA_tr) ] = true then

CurrentBAState:=DstState(BA_tr)

\otimes \operatorname{Oport}(\operatorname{th}) := \operatorname{Action}(\operatorname{BA\_tr})(\operatorname{Iport}(\operatorname{th}))

⊕ //Rule Behavior Annex Completion

Time 0 ▷ (if isFinal(CurrentBAState)=true then

State(th):=computed)

```

# 6. The proof of semantics preservation

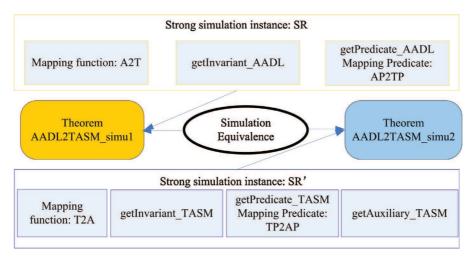

In this section, we give the main idea of the proof of semantics preservation of the transformation from AADL to TASM, i.e. the exact correspondence between execution steps defined by the AADL operational semantics and those defined by the semantics of the target TASM model. Here, the semantics preservation is defined as a strong-simulation equivalence between the TTSs related to the AADL model and to the TASM model respectively, which implies ACTL (the universal fragment of Computation Tree Logic) and ECTL (the existential fragment of Computation Tree Logic) preservation and thus preservation of the UPPAAL query language. After a brief introduction to Coq, we introduce the property language used to express atomic observers. Then, we introduce a generic definition of simulation equivalence based on a mapping function on states and a mapping function on predicates. At last, simulation equivalence is applied in a compositional manner on AADL and the obtained TASM models.

# 6.1. A brief introduction to Coq

Coq (Bertot and Castéran, 2004) is a theorem prover based on the Calculus of Inductive Constructions which is a variant of type theory, following the "Curry-Howard Isomorphism" paradigm, enriched with support for inductive and co-inductive definitions of data types and predicates. From the specification perspective, Coq offers a rich specification language to define problems and state theorems. From the proof perspective, proofs are developed interactively using tactics, which can reduce the workload of the users. Moreover, the type-checking performed by Coq is the key point of proof verification.

Here, we try to give an intuitive introduction to the Coq terminologies which are used in this paper. In the spirit of "Curry-Howard Isomorphism" paradigm, types may represent programming data-types or logical propositions. So, the Coq objects used in this paper can be sorted into two categories: the *Type* sort and the *Prop* sort:

- *Type* is the sort for data types and mathematical structures, i.e. well-formed types or structures are of type *Type*. Data types can be basic types such as *nat*, *bool*, *nat* → *nat*, etc., and can be *Inductive* structures or *Record*. We use *Fixpoint* definitions to define functions over inductive data types.

- *Prop* is the sort for propositions, i.e. well-formed propositions are of type *Prop*. We can define new predicates using *Inductive* and *Record* (for conjunctions of properties).

#### 6.2. Properties

In order to express complex properties on the models, we first introduce the atomic observers (*Predicate*) as for example "port p of thread th has value v", "thread th is in the given state s", and "thread th gets the CPU". From these observers, we build propositional formulas (*LP*), and give their semantics over the TTS states (through the *LPSat* function).

We now give the corresponding Coq definitions:

```

Variable Predicate: Type.

Inductive LP: Type :=

LPPred: Predicate → LP

| LPAnd: LP → LP → LP

| LPNot: LP → LP.

Variable State: Type.

Variable Sat: State → Predicate → Prop.

Fixpoint LPSat st f: Prop :=

match f with

LPPred p ⇒ Sat st p

| LPAnd f1 f2 ⇒ LPSat st f1 ∧ LPSat st f2

| LPNot f1 ⇒ ¬LPSat st f1

end.

```