# Object-Oriented Component-based Design using Behavioral Contracts: Application to Railway Systems

Sebti Mouelhi, Khalid Agrou, Samir Chouali, Hassan Mountassir

#### ▶ To cite this version:

Sebti Mouelhi, Khalid Agrou, Samir Chouali, Hassan Mountassir. Object-Oriented Component-based Design using Behavioral Contracts: Application to Railway Systems. [Research Report] FEMTO-ST. 2015. hal-01102947v1

# HAL Id: hal-01102947 https://hal.science/hal-01102947v1

Submitted on 13 Jan 2015 (v1), last revised 12 Sep 2015 (v2)

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **INSTITUT FEMTO-ST**

**UMR CNRS 6174**

# Object-Oriented Component-based Design using Behavioral Contracts: Application to Railway Systems

Sebti Mouelhi — Khalid Agrou — Samir Chouali — Hassan Mountassir

# Rapport de Recherche

DÉPARTEMENT DISC - January 13, 2015

# Object-Oriented Component-based Design using Behavioral Contracts: Application to Railway Systems

Sebti Mouelhi\*, Khalid Agrou<sup>†</sup>, Samir Chouali<sup>‡</sup>, Hassan Mountassir<sup>‡</sup>

# Département DISC VESONTIO

Rapport de Recherche – January 13, 2015 (23 pages)

Abstract: In this report, we propose a formal approach for the design of object-oriented component-based systems using *behavioral contracts*. This formalism merges interface automata describing communication protocols of components with the semantics of their operations. On grounds of consistency with the object-oriented paradigms, we revisit the notions of *incremental design* and *independent implementability* of interface automata by novel definitions of components compatibility, composition, and refinement. Our work is illustrated by a design case study of CBTC railway systems to argue their relevance in the safety-critical context.

**Key-words:** Object-oriented components, Behavioral contracts, Interface automata, Semantics, Refinement, Railway systems.

<sup>\*</sup> SafeRiver, 92120, Montrouge, France (sebti.mouelhi@safe-river.com).

<sup>&</sup>lt;sup>†</sup> UPMC Pro, 75005, Paris, France (khalid.agrou@free.fr).

<sup>&</sup>lt;sup>‡</sup> FEMTO-ST Institute, UMR CNRS 6174, 25030, Besançon, France ({schouali,hmountas}@femto-st.fr).

#### Conception par des Contrats Comportementaux des Systèmes à base de Composants Orientés Objet: Application aux systèmes Ferroviaires

Résumé: Dans ce rapport, nous proposons une approche formelle pour la conception de systèmes à base de composants orientés objet en utilisant les *contrats de comportement*. Ce formalisme fusionne les *automates d'interface* décrivant les protocoles de communication des composants avec la sémantique de leurs opérations. Pour des raisons de cohérence avec les paradigmes orientés objet, nous revisitons les notions de *conception incrémentale* et l'*implémentation indépendante* établies pour les automates d'interface en définissant autrement la compatibilité, la composition, et le raffinement des composants par le billet de leurs contrats de comportement. Notre travail est illustré par un cas d'utilisation des systèmes ferroviaires CBTC pour valoir leur pertinence dans le contexte de systèmes critique.

Mots-clés: Composants orientés objets, Contrats comportementaux, Automates d'interface, Sémantique, Raffinement, Systémes ferroviaire.

#### 1 Introduction

Component-based development approaches aim to reduce the cost of complex systems design by reusing prefabricated components. A software component is a black box unit of a third-party composition and deployment, with explicit dependencies to its environment [17]. It is exclusively reusable via its interface behavioral specification without disclosing implementation details. However, the design by composition often raises mismatches. A safe interoperability between components should fulfill two main properties: (1) their interactions do not lead to undesirable situations, and (2) the substitution of a component with a new one does not alter the compound system.

Commonly, the functional interoperability of components is usually checked at the signature, semantic and protocol levels. At the signature level, it is checked on the names and argument types of component operations. At the semantic level, it is verified on the meanings of operations generally modeled by pre/postconditions and invariants. The protocol level regards the consistency of the temporal scheduling of assumptions on the environment inputs to a component, its output behavior, and its local operations. Component protocols can be modeled naturally by interface automata [9] obedient to an optimistic approach of composition closely related to the object-oriented context: if they communicate within an environment allowing them to avoid deadlocks, they can be used without changes. In the industrial context, this approach allows errors detection during the design phase, and hence taking the appropriate decision: either keeping components as they was received from their manufacturer, or requesting their modification.

The first contribution of this report is to demonstrate how object-oriented component-based design (OOCBD) is more rigorous by means of behavioral contracts merging interface automata with the semantics of methods. The optimistic approach of interface automata composition is accordingly adapted to fulfill the interaction aspects of object-oriented components. The composition of two interface automata is computed by removing from their synchronized product all states from which the environment cannot prevent deadlock states (arising from semantic and protocol mismatches) by enabling controllable or autonomous actions [9, 4]. We define the concept of autonomous actions differently by reclassifying them into method, return, and exception actions.

The second is about the study of components refinement using behavioral contracts, intended to ensure an independent implementability of components. We present refinement as an expanding simulation between interface automata allowing (i) the introduction, in a component refinement, more details about common provided services with the abstraction, and (ii) providing more services than the abstraction. These features lead to consider the refinement relation as covariance on input and output events of a component: refinement issues (resp. provides) more outputs (resp. inputs) than the abstraction. A concrete version C' of a component refines an abstract one C if each input, output, or local event of C is simulated at least by the same event in C'. The refinement approach, originally proposed in [9], requires contravariance on input and output events of interface automata: refinement may accept more inputs, and may provide fewer outputs, than the abstraction. It is defined as an alternating simulation [5]: a component model C' refines a second one C if each input event of C can be simulated by C', and each output event of C' can be simulated by C. This approach is not quite consistent, from our perspective, with the object-oriented context.

All through the report, we justify the relevance of our approach for checking design integrity of railway systems. We propose a case study of trains protection functions in modern railway CBTC control systems to track the evolution of safety standards such as the European Norm

EN 50128 [1], and to give a new industrial perspective for the design of such critical systems using an object-oriented approach.

The report results appeared partially in preliminary formulations and other contexts in [8, 15]. In Section 2, we start by introducing informally our case study to avoid cluttering the contribution sections. It is nevertheless recalled gradually to validate the various introduced formal concepts. In sections 3 and 4, we proceed with the study of behavioral contracts, and our approach of components compatibility and composition. Section 5 is devoted to the study of refinement of behavioral contracts. Conclusions are presented in Section 6.

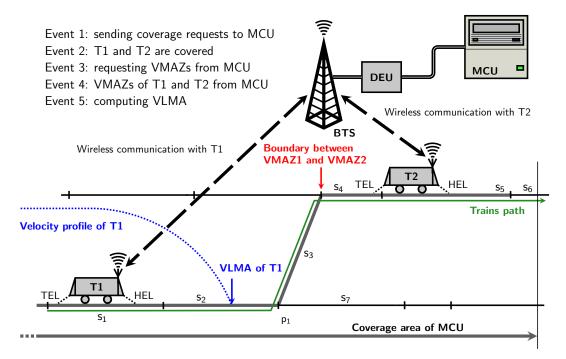

Figure 1: Simplified trains protection in CBTC systems.

# 2 Railway case study

In this section, we introduce a simplified case study of trains protection functions in CBTC (Communications-Based Train Control) systems [2], used to illustrate our work (cf. Figure 1). These systems are the next generation of railway control technology which is increasingly being adopted in subways and other similar means of transportation, as well as many industrial major projects worldwide, such as ERTMS/ETCS (European Rail Traffic Management System/European Train Control System) [11, 10]. A CBTC system is an automatic train controller independent of track circuits. It determines continuously, in real-time, precise locations of trains, and sends them back control signals by means of bidirectional train-to-wayside data communications. It has train-borne and wayside processor devices implementing automatic train protection (ATP) functions, as well as automatic train operation (ATO), and automatic train supervision (ATS) functions. ATP devices ensure safety-critical requirements (speed control and braking). ATO devices cover non safety-related requirements (doors opening and closing, etc). ATS devices handle the traffic management when necessary [2]. CBTC systems reduce significantly the amount of wayside equipments and allows benefits such as high traffic densities, better headways, reliability of anti-collision processing, adoption of automated trains, etc.

We consider trains control based on moving block regime. The positions of a moving train and its velocity are continuously computed based on its kinetic and potential energy, and then communicated via wireless to wayside equipments. Thus, a protected area of circulation is established for each train up to the next nearest obstacle. For the train T1 in Figure 1, this point is the tail of T2. The train is consequently able to adapt its speed and braking curves in order to not overcome the limit of this area, namely the danger point [16] and ensures a safe stopping before that point if necessary. ATO and ATS functions do not play a significant role on safety, and they are not considered in this report.

The On-Board Device (OBD) of each train computes two fictional locations: the tail and head external locations (TEL and HEL). The track fragment between them covers the whole train. Usually, this choice is caught on grounds of safety to keep a safe distance between trains in case of system malfunction. Locations are coordinates on the trains path composed of segments and set in a given direction according to the railroad switches positions. A segment is identified by a number, a length, and a beginning coordinate. In Figure 1, the switch  $p_1$  is positioned on the segment  $s_3$ , and the train path is the sequence  $s_1$ ,  $s_2$ ,  $s_3$ ,  $s_4$ ,  $s_5$ ,  $s_6$ , etc.

The OBDs of T1 and T2 initiate the protection process by asking if they are visible to a *Movement Control Unit* (MCU). There are several MCUs covering the entire line, with overlapping coverage sections allowing safe information handover between them. Only one is represented in our case study. The trains locations are sent by wireless to the nearest *Base Transmission Station* (BTS). The latter converts radio signals to digital data and transmits them to the *Data Exchange Unit* (DEU), which in turn transfers them to MCU (event 1). MCU determines whether the zone between TEL and HEL is completely or partially included within its coverage area, and responds T1 and T2. In Figure 1, T1 and T2 are both visible to MCU (event 2).

Next, each train asks from its covering MCUs the Vital Movement Authority Zone (VMAZ): the area (sequence of segments) in which the train can safely circulate (event 3). In Figure 1, MCU sends to T1 a VMAZ limited by the beginning of  $s_1$  (containing its TEL and HEL) and the end of  $s_3$ , and sends to T2 a VMAZ limited by the beginning of  $s_4$  (containing its TEL) and the end of  $s_5$ , the last segment covered by MCU (event 4). MCU ensures that VMAZs of successive trains never overlap to avoid collisions. VMAZs are computed by chaining segments according to the route informations. Chaining may be interrupted up to the nearest obstacle on the train trajectory: the end of MCU coverage area, an uncontrolled switch, or the beginning of the segment containing TEL of the next train, etc. This function is covered by a separate wayside component managing persistent informations (segment and switch locations) and variant ones (switch positions) of the route during the traffic.

Finally, the train computes the danger point, called *Vital Limit of Movement Authority* (VLMA), within the boundaries of the received VMAZ. To locate VLMA, OBD takes a fixed safety margin beforehand the limit of its VMAZ. The train velocity is gradually reduced to reach zero when HEL reaches VLMA (event 5).

#### 3 Behavioral contracts

The functional interoperability of object-oriented components is checked at the signature, semantic and protocol levels. Each of these levels alone is not sufficient to ensure a reliable interoperability. We combine interface automata with the semantics of methods in a single formalism called behavioral contracts. We start by introducing interface automata.

#### 3.1 Interface automata

Interface automata [9, 4] model the communication protocols of software components in terms of temporal scheduling of their *input*, *output*, and *hidden actions*. In OOCBD, input actions may represent the component public provided methods, the assignment of return values of their calls, and catching their exceptions. Output actions may represent method calls, and return or exception events. Private methods are implicit and not specified by actions. However, their calls, the assignment of their return values, and the catching of their thrown exceptions are modeled by hidden actions.

**Definition 1.** A interface automaton A is a tuple  $(\Upsilon_A, \iota_A, \Sigma_A^{\rm I}, \Sigma_A^{\rm O}, \Sigma_A^{\rm H}, \delta_A)$  where:  $\Upsilon_A$  is a finite set of states;  $\iota_A \in \Upsilon_A$  is the initial state;  $\Sigma_A^{\rm I}$ ,  $\Sigma_A^{\rm O}$ , and  $\Sigma_A^{\rm H}$  are resp. the sets of input, output, and hidden actions;  $\delta_A \subseteq \Upsilon_A \times \Sigma_A \times \Upsilon_A$  is the set of transitions. A is empty iff  $\Upsilon_A = \emptyset$ .

The alphabet of A consists of "a?" for  $a \in \Sigma_A^I$ , "a!" for  $a \in \Sigma_A^O$ , and "a;" for  $a \in \Sigma_A^H$ . The sets  $\Sigma_A^{\operatorname{Im}} \subseteq \Sigma_A^I$ ,  $\Sigma_A^{\operatorname{Om}} \subseteq \Sigma_A^O$ , and  $\Sigma_A^{\operatorname{Hm}} \subseteq \Sigma_A^H$ , are resp. actions of public provided methods, call of environment public methods, and calls of private methods. The set  $\Sigma_A^{\operatorname{m}}$  of  $\operatorname{method}$  actions of A is  $\Sigma_A^{\operatorname{Im}} \cup \Sigma_A^{\operatorname{Om}} \cup \Sigma_A^{\operatorname{Hm}}$ . Given a set of variables V, we define by  $\mathbb{T}[v]$  the type of  $v \in V$  i.e.  $v:\mathbb{T}[v]$ , and by  $\mathbb{T}[v] = \prod_{v \in V} \mathbb{T}[v]$  the type of V (cartesian product of  $\mathbb{T}[v]$  for all  $v \in V$ ). The signature of a method action  $a \in \Sigma_A^{\operatorname{m}}$  is  $a(i_1:\mathbb{T}[i_1], ..., i_k:\mathbb{T}[i_k]) \to o:\mathbb{T}[o] \not\equiv e$ . The set of input parameters of a is  $\Psi_A^i(a) = \{i_1, ..., i_k\}$ . The set of return parameters  $\Psi_A^o(a)$  of a is the singleton  $\{o\}$ . We define  $\mathbb{R}_A(a) = o$  the return action of a, and  $\mathbb{E}_A(a) = e$  the exception action of a. The set of attributes used by a is denoted by  $A_A(a)$  if  $a \in \Sigma_A^{\operatorname{Im}} \cup \Sigma_A^{\operatorname{Im}}$ . The absence of parameters, attributes, or exceptions is represented by a void. If  $\mathbb{R}_A(a)$  and  $\mathbb{E}_A(a)$  are defined, we set  $\Sigma_A^r$  and  $\Sigma_A^e$  resp. to  $\{\mathbb{R}_A(a) \mid a \in \Sigma_A^{\operatorname{m}}\}$  and  $\{\mathbb{E}_A(a) \mid a \in \Sigma_A^{\operatorname{m}}\}$ . We denote, by  $\Sigma_A^{\operatorname{rr}}$  and  $\Sigma_A^{\operatorname{res}}$ , resp. the sets  $\Sigma_A^r \cap \Sigma_A^e$  and  $\Sigma_A^e \cap \Sigma_A^e$  where  $*\in \{\mathbb{I}, \mathbb{O}, \mathbb{H}\}$ . It is worth to mention here that  $\Sigma_A = \Sigma_A^{\operatorname{m}} \cup \Sigma_A^r \cup \Sigma_A^e$ . We set  $Succ_A(s, a) = t$  such that  $(s, a, t) \in \delta_A$ . A run  $\sigma$  of A is a finite alternated sequence  $s_0[a_0]...[a_{n-1}]s_n$  of states and actions where  $(s_k, a_k, s_{k+1}) \in \delta_A$  for all  $k \in \mathbb{N}_{\leq n}$ . We set  $\Sigma_A \langle \sigma \rangle = \{a_k \in \Sigma_A \mid k \in \mathbb{N}_{\leq n}\}$  and  $\Sigma_A^*$  is reachable in A if  $\Theta_A(s) \neq \emptyset$ .

Assumptions: Interface automata are deterministic, i.e. for all  $(s, a, s_1), (s, a, s_2) \in \delta_A$ ,  $s_1 = s_2$ . All states  $s \in \Upsilon_A$  are reachable in A. Consider an action  $a \in \Sigma_A^{\mathrm{m}}$  where  $\mathsf{R}_A(a)$  and  $\mathsf{E}_A(a)$  are defined. If  $a \in \Sigma_A^{\mathrm{Im}}$  (resp.  $\Sigma_A^{\mathrm{Om}}$  and  $\Sigma_A^{\mathrm{Hm}}$ ), then  $\mathsf{E}_A(a) \in \Sigma_A^{\mathrm{O}} \setminus \Sigma_A^{\mathrm{m}}$  (resp.  $\Sigma_A^{\mathrm{I}} \setminus \Sigma_A^{\mathrm{m}}$  and  $\Sigma_A^{\mathrm{H}} \setminus \Sigma_A^{\mathrm{m}}$ ): a component providing or requiring a knows its exception. If  $a \in \Sigma_A^{\mathrm{Im}}$ , then  $\mathsf{R}_A(a) \in \Sigma_A^{\mathrm{O}} \setminus \Sigma_A^{\mathrm{m}}$ : the method a must output its return value. If  $a \in \Sigma_A^{\mathrm{Om}} \cup \Sigma_A^{\mathrm{Hm}}$ , then  $\mathsf{R}_A(a)$  may belong or not to  $(\Sigma_A^{\mathrm{I}} \cup \Sigma_A^{\mathrm{H}}) \setminus \Sigma_A^{\mathrm{m}}$ : a component invoking a may assign or not its return value.

#### Well-formedness

Object-oriented implementation rules should be covered by the runs of interface automata. A provided public non-void method should be specified at least by a sequence of events starting and ending resp. by an input method action and an output return one interposed, by calls of local private or environment public methods and the assignment of their return values. They may be interleaved optionally by catching or throwing exceptions events. A call of a non-void method, made by a component requiring the assignment of its return value, is followed necessarily by a return input action, and optionally by an exception catch one. All the actions of a component are *autonomous* (controllable), except method or exception input actions. It's up to the environment to enable or not these actions. In [9, 4], only output and hidden actions

are required to be autonomous. From our perspective, input return actions of non-void method calls, made by a component, are also autonomous because the environment is expected to provide their return values and the component has the option to assign them or not.

The set  $\Sigma_A^{\mathrm{aut}}$  of autonomous actions is  $\Sigma_A \setminus (\Sigma_A^{\mathrm{Im}} \cup \Sigma_A^{\mathrm{Ie}})$ . We define by  $\Sigma_A^*(s)$  where  $* \in \{\mathrm{I}, \mathrm{O}, \mathrm{H}, \mathrm{Im}, \mathrm{Om}, \mathrm{Hm}, \mathrm{Ir}, \mathrm{Or}, \mathrm{Hr}, \mathrm{Ie}, \mathrm{Oe}, \mathrm{He}, \mathrm{m}, \mathrm{r}, \mathrm{e}, \mathrm{aut}\}$  the set of actions in  $\Sigma_A^*$  enabled from  $s \in \Upsilon_A$ .  $\Sigma_A(s)$  is the set of all enabled actions from s. The run  $\sigma = s_0[a_0]...[a_{n-1}]s_n$  is called autonomous in A if  $\Sigma_A \langle \sigma \rangle \subseteq \Sigma_A^{\mathrm{aut}}$  for all  $k \in \mathbb{N}_{< n}$ . It is called exception-free if  $\Sigma_A \langle \sigma \rangle \subseteq \Sigma_A \setminus \Sigma_A^{\mathrm{e}}$  for all  $k \in \mathbb{N}_{< n}$ . A state  $s' \in \Upsilon_A$  is reachable autonomously (resp. without exceptions) from  $s \in \Upsilon_A$  in A if there is an autonomous (resp. exception free) run between s and s'.

**Definition 2.** An interface automaton A is well-formed iff for all state  $s \in \Upsilon_A$ , and action  $a \in \Sigma_A^{\mathrm{m}}(s)$  where  $\mathsf{R}_A(a) \in \Sigma_A^{\mathrm{r}}$ , there is at least a state  $t \in \Upsilon_A$ , where  $\mathsf{R}_A(a) \in \Sigma_A^{\mathrm{r}}(t)$ , reachable autonomously without exceptions from  $Succ_A(s,a)$ .

#### 3.2 Method semantics

The semantics of a provided method consists of: (i) a precondition representing the environment assumptions on input parameters, (ii) an abstract specification of the return parameter computation using input parameters and attributes, (iii) a termination postcondition on the return parameter depending on input parameters and attributes, and (iv) an extra postcondition describing exception conditions on parameters and attributes. A method call semantics is defined only by a precondition on input parameters and a postcondition on input and return parameters. Given a set of variables V, a condition on v is a subtype of  $\mathbb{T}[v]$ . A condition Q on V is a subtype of  $\mathbb{T}[V]$ . We denote by  $Q[w_1, ..., w_n]$  (or Q[W]), the projection of Q on variables in  $W = \{w_1, ..., w_n\} \subseteq V$ . These conditions can be concretely defined as predicates in a theory adapted to the variable types. Consider the set  $Z \subseteq W$ , and two conditions P and Q subtypes of  $\mathbb{T}[V]$ , we set the following equivalences to define semantic formulas in the rest of the report:

- $\bot \llbracket W \rrbracket \equiv P \llbracket W \rrbracket = \emptyset; \top \llbracket W \rrbracket \equiv P \llbracket W \rrbracket = \mathbb{T} \llbracket W \rrbracket; \neg P \llbracket W \rrbracket \equiv \mathbb{T} \llbracket W \rrbracket \setminus P \llbracket W \rrbracket;$

- $\bullet \quad P[\![Z]\!] \wedge Q[\![W]\!] \equiv (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cap Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] \equiv (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] \equiv (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] \equiv (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] \equiv (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] \equiv (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] \equiv (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] \equiv (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] \equiv (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] \equiv (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] \equiv (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W \setminus Z]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![W]\!]) \cup Q[\![W]\!]; \\ P[\![Z]\!] \vee Q[\![W]\!] = (P[\![Z]\!] \times Q[\![$

- $P[W] \Rightarrow Q[W] \equiv P[W] \subseteq Q[W]$ .

**Definition 3.** Given an interface automaton A, an input semantics  $I_a = (P_a, B_a, Q_a, E_a)$  of an action  $a \in \Sigma_A^{\operatorname{Im}}$  is defined by:

- a precondition  $P_a \subseteq \mathbb{T}[\![\Psi^i_A(a)]\!];$

- a specification  $S_a \subseteq \mathbb{T}[\![\Psi_A^i(a) \cup \Lambda_A(a) \cup \Psi_A^o(a)]\!];$

- a termination postcondition  $Q_a \subseteq \mathbb{T}[\![\Psi_A^i(a) \cup \Lambda_A(a) \cup \Psi_A^o(a)]\!];$

- an exception postcondition  $E_a \subseteq \mathbb{T}[\![\Psi_A^i(a) \cup \Lambda_A(a) \cup \Psi_A^o(a)]\!].$

An output semantics  $O_b = (P_b, Q_b)$  of an action  $b \in \Sigma_A^{Om}$  is defined by:

- a precondition  $P_b \subseteq \mathbb{T}[\![\Psi_A^i(b)]\!];$

- a postcondition  $Q_b \subseteq \mathbb{T}[\![\Psi_A^i(b) \cup \Psi_A^o(b)]\!]$ .

These conditions are denoted resp. by  $I_a.P$ ,  $I_a.S$ ,  $I_a.Q$ ,  $I_a.E$ ,  $O_b.P$ , and  $O_b.Q$ .

In the previous definition, we consider only the semantics of observable method actions  $(a \in \Sigma_A^{\operatorname{Im}} \cup \Sigma_A^{\operatorname{Om}})$ . We omit the semantics of private method actions  $(a \in \Sigma_A^{\operatorname{Hm}})$  because they are not relevant for interoperability. We define behavioral contracts as follows.

**Definition 4.** A behavioral contract B of a component is a tuple  $(A, \mathcal{I}, \mathcal{O})$  such that:

- A is an interface automaton;

- $\mathcal{I}$  is a map associating for each  $a \in \Sigma_A^{\mathrm{Im}}$ , an input semantics  $I_a$ ;

- $\mathcal{O}$  is a map associating for each  $a \in \Sigma_A^{\mathrm{Om}}$ , an output semantics  $O_a$ .

We denote by, B.A, the interface automaton of B, by B.I, the map I of B, and by B.O, the map O of B.

**Definition 5.** Given a behavioral contract B and an action  $a \in \Sigma_A^{\operatorname{Im}}$  where  $B.\mathcal{A} = A$  and  $B.\mathcal{I}(a) = (P_a, B_a, Q_a, E_a)$ , for all  $(i, f, o) \in \Psi_A^i(a) \times \Lambda_A(a) \times \Psi_A^o(a)$ ,

- a is correct with respect to  $B.\mathcal{I}(a)$  iff  $P_a[i] \wedge S_a[i, f, o] \Rightarrow Q_a[i, f, o]$ ;

- a terminates with respect to  $B.\mathcal{I}(a)$  iff  $P_a[i] \wedge S_a[i, f, o] \Rightarrow Q_a[i, f, o] \wedge \neg E_a[i, f, o];$

- a throws exceptions with respect to  $B.\mathcal{I}(a)$  iff  $P_a[i] \wedge S_a[i, f, o] \Rightarrow E_a[i, f, o]$ ;

The previous definition establishes the different relations between the specification and the pre/postconditions of an input method action  $a \in \Sigma_A^{\operatorname{Im}}$ . The stated conditions are based on the Hoare triplet [12]: a provided method is correct if its behavior under the precondition ensures the postcondition; it terminates if it is correct and the exception postcondition is not satisfied, and throws exceptions if the exception postcondition is satisfied.

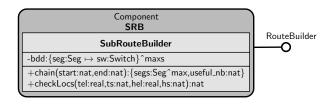

#### 3.3 Design of the railway case study

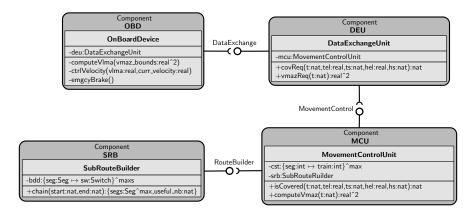

The UML-like component architecture in Figure 2 presents the different ATP equipments mentioned in Section 2. We count four component classes: OnBoardDevice, DataExchangeUnit, MovementControlUnit, and SubRouteBuilder instantiated resp. by the components OBD, DEU, MCU, and SRB. The last three ones implement resp. the interfaces DataExchange, Movement-Control, and RouteBuilder.

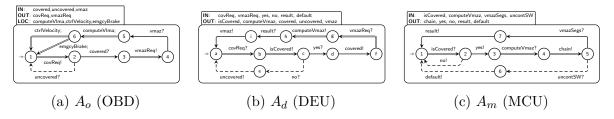

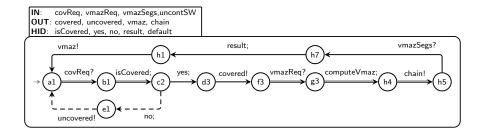

The component DEU implements the public (+) method covReq (coverage request), whose arguments are: tel and ts, resp. the coordinate of TEL, sent by OBD, and the identifier of the segment containing TEL, hel and hs, resp. the coordinate of HEL and the identifier of the segment containing HEL, and t, the train identifier. According to the interface automaton  $A_d$  of DEU (cf. Figure 3(b)), the method covReq transfers the coverage request to MCU by invoking the method isCovered. MCU responds OBD, via DEU, by returning 2 (resp. 1) if it covers completely (resp. partially) the train (signal covered), or by throwing uncovered if not.

Subsequently, if the train is covered by MCU, OBD requests its VMAZ (vmazReq). DEU transfers the request by calling computeVmaz implemented by MCU. In turn, MCU calls the method chain of SRB to perform chaining on segments in order to compute the VMAZ bounds within the sequence of segments from start to end, the arguments of chain. If MCU covers only hel, the argument start is set to the first segment in the trains path fully covered by MCU. Otherwise, it is set to ts. The argument end is always set to the last segment fully covered by MCU. According to  $A_m$  in Figure 3(c), if chaining is interrupted by an uncontrolled switch, MCU handles the exception uncontSW thrown by chain and in turn, throws default.

Based on the path database bdd, SRB returns VMAZ segments in the table segs of size max the maximum number of segments covered by MCU. The field  $useful\_nb \le max$  indicates the number of segments included in VMAZ. MCU computes accordingly the VMAZ bounds coordinates on the path frame based on informations of useful segments (identifiers, beginning coordinates, and lengths saved in data structures of type Seg). In the case where MCU covers

Figure 2: UML-like component architecture.

Figure 3: Interface automata of OBD, DEU, and MCU: method actions (double transitions); return actions (simple transitions); exception actions (dashed transitions).

| Table 1. Semantics of the method action conteq.          |                                                                       |  |  |

|----------------------------------------------------------|-----------------------------------------------------------------------|--|--|

| Output semantics $B_o.\mathcal{O}$                       | Input semantics $B_d.\mathcal{I}$                                     |  |  |

| $B_o.\mathcal{O}(covReq).P \equiv t \in \{0,,30\} \land$ | $B_d.\mathcal{I}(covReq).P \equiv t \in \{0,, 30\} \land$             |  |  |

| $ts, hs \in \{0,, 500\} \land$                           | $ts, hs \in \{0,,500\} \land$                                         |  |  |

| $tel, hel \in [0, 5000] \land tel < hel$                 | $tel, hel \in [0, 5000]$                                              |  |  |

|                                                          | $B_d.\mathcal{I}(covReq).S \equiv \bot[t, tel, hel, ts, hs, covered]$ |  |  |

| $B_o.\mathcal{O}(covReq).Q \equiv covered \in \{0,1,2\}$ | $B_d.\mathcal{I}(covReq).Q \equiv covered \in \{1, 2\}$               |  |  |

|                                                          | $B_d.\mathcal{I}(covReq).E \equiv covered = 0$                        |  |  |

Table 1: Semantics of the method action covReq

only a part of the train VMAZ, it returns a pair vmaz of coordinates where one of them is null and the other is a positive real. Otherwise, the two coordinates are positive reals. The map attribute cst (covered segments and trains) is finally updated such that segments covered both by MCU and VMAZ of the train are associated to its identifier.

According to  $A_o$  in Figure 3(a), OBD fixes finally VLMA by calling its private (-) method computeVlma before the final bound of VMAZ. It controls the train speed if HEL is sufficiently far from VLMA (ctrlVelocity), or performs an emergency brake (emgcyBrake) otherwise.

Let us consider three behavioral contracts  $B_o$ ,  $B_d$ , and  $B_m$  resp. for components OBD, DEU, and MCU where  $B_o$ . A is  $A_o$ ,  $B_d$ . A is  $A_d$ , and  $B_m$ . A is  $A_m$ . Table 1 shows a semantics of covReq in  $B_o$  and  $B_d$  whose signature is covReq (t, tel, ts, hel, hs)  $\rightarrow$  covered  $\sharp$  uncovered (parameter types are given in Figure 2). The semantics of covReq in  $B_o$  and  $B_d$  states that the minimal and maximal identifiers t of trains, are resp. 0 and 30, and those of segment identifiers (ts and hs), are resp. 0 and 500. The precondition of covReq in  $B_o$  states that the conditions tel,  $hel \in [0, 5000]$  and tel < hel have to be satisfied by calling the method, where 5000um (unit of measurement) is the size of the longest trains path. In  $B_d$ , the precondition states simply

that  $tel, hel \in [0, 5000]$ . In  $B_o$ , the postcondition of covReq states that the return parameter covered is a signal in  $\{0, 1, 2\}$ . However, in  $B_d$ , it states only that covered is a signal in  $\{1, 2\}$  because if it is equal to 0, the exception uncovered is thrown. The specification  $B_d.\mathcal{I}(covReq).S$  is not defined ( $\bot[t, tel, hel, ts, hs, covered]$ ): at the level of  $B_d$ , there is no parameter or attribute ( $\Lambda_{A_d}(covReq) = \emptyset$ ) describing how the return parameter covered is computed. MCU, after receiving the coverage request from OBD, is expected to ask SRB to check in bdd whether tel and hel are really placed resp. on ts and hs, as claimed by OBD. This function of SRB does not appear intentionally at this stage. We expect using this detail to justify refinement in Section 5

Finally, consider that  $\mathsf{R}_{A_o}(covReq)$  is  $covered \in \Sigma_{A_o}^{\mathrm{r}}$ ,  $\mathsf{R}_{A_o}(vmazReq)$  is  $vmaz \in \Sigma_{A_o}^{\mathrm{r}}$ , and  $\mathsf{E}_{A_o}(covReq)$  is  $uncovered \in \Sigma_{A_o}^{\mathrm{e}}$ , we can deduce that  $A_o$  is well-formed. The reader can easily deduce the well-formedness of  $A_d$  and  $A_m$  by finding their method, return and exception actions.

### 4 Components Composition

The composition of two behavioral contracts may induce deadlock situations caused by potential semantic or protocol incompatibilities. At the protocol level, the composition of two interface automata may contain *deadlock* states. From that states, one of the two interface automata requests an input not accepted by the other. For example, a component calls a method throwing exceptions without handling them. In Java, a deadlock state is the detection of a method call exception not included in a clause try/catch. The thrown exception is the output action and the try/catch freedom is considered as the absence of the corresponding input action.

At the semantic level, the synchronization of shared input/output method actions with incompatible semantics, leads to deadlock states. A component outputting a method call have more informations about its arguments. Thus, the call precondition is stronger than that of the method implementation: the environment is expected to provide input arguments included in the implementation precondition. In return, the component providing the method communicates to the environment a postcondition on its return parameter: it vouches to provide only return values that satisfy the postcondition. The calling component cannot have more detailed informations about the return parameter than the implementing one. That's why the postcondition of a method invocation is weaker than that provided by its implementation. Note that preconditions, like postconditions, of provided observable methods are required to be satisfiable. Not all calling environments satisfy the precondition, or expect return guarantees larger than the postcondition [4]. In this case, synchronization disparities are detected.

#### 4.1 Synchronization of interface automata and semantic compatibility

The synchronization of two interface automata  $A_1$  and  $A_2$  is possible only if they are mutually composable i.e.  $\Sigma_{A_1}^{\rm I} \cap \Sigma_{A_2}^{\rm I} = \Sigma_{A_1}^{\rm O} \cap \Sigma_{A_2}^{\rm O} = \Sigma_{A_1}^{\rm H} \cap \Sigma_{A_2} = \Sigma_{A_2}^{\rm H} \cap \Sigma_{A_1} = \emptyset$ . The set of shared input/output actions in  $A_1$  and  $A_2$  is  $Shared(A_1, A_2) = (\Sigma_{A_1}^{\rm I} \cap \Sigma_{A_2}^{\rm O}) \cup (\Sigma_{A_2}^{\rm I} \cap \Sigma_{A_1}^{\rm O})$ . For simplicity, we denote the couple of states  $(s_1, s_2)$  by  $s_1s_2$ . By synchronizing  $A_1$  and  $A_2$ , transitions labeled by shared actions synchronize and the others are interleaved asynchronously. The synchronized product  $A_1 \otimes A_2$  of  $A_1$  and  $A_2$  is an interface automaton where  $\Upsilon_{A_1 \otimes A_2} = \Upsilon_{A_1} \times \Upsilon_{A_2}$ ,  $\iota_{A_1 \otimes A_2} = \iota_{A_1 \iota_{A_2}}$ ,  $\iota_{A_1 \otimes A_2} = (\iota_{A_1}^{\rm I} \cup \iota_{A_2}^{\rm I}) \setminus Shared(A_1, A_2)$ ,  $\iota_{A_1 \otimes A_2}^{\rm O} = (\iota_{A_1}^{\rm O} \cup \iota_{A_2}^{\rm O}) \setminus Shared(A_1, A_2)$ ,  $\iota_{A_1 \otimes A_2}^{\rm H} = \iota_{A_1 \otimes A_2}^{\rm H} \cup \iota_{A_2}^{\rm H} \cup \iota_{A_2}^{\rm H} \cup Shared(A_1, A_2)$ , and  $\iota_{A_1 \otimes A_2}^{\rm H} = \iota_{A_1 \otimes A_2}^{\rm H} = \iota_{A_1 \otimes A_2}^{\rm H} \cup \iota_{A_2}^{\rm H} \cup Shared(A_1, A_2)$ , and  $\iota_{A_1 \otimes A_2}^{\rm H} = \iota_{A_1 \otimes A_2}^{\rm H} = \iota_{A_1 \otimes A_2}^{\rm H} \cup \iota_{A_2}^{\rm H} \cup Shared(A_1, A_2)$ , and  $\iota_{A_1 \otimes A_2}^{\rm H} = \iota_{A_1 \otimes A_2}^{\rm H} = \iota_{A_1 \otimes A_2}^{\rm H} = \iota_{A_1 \otimes A_2}^{\rm H} \cup Shared(A_1, A_2)$ , and  $\iota_{A_1 \otimes A_2}^{\rm H} = \iota_{A_1 \otimes A_2}^{\rm H} = \iota_{A_1 \otimes A_2}^{\rm H} = \iota_{A_1 \otimes A_2}^{\rm H} \cup Shared(A_1, A_2)$ , and  $\iota_{A_1 \otimes A_2}^{\rm H} = \iota_{A_1 \otimes A_2$

- $a \in Shared(A_1, A_2) \land (s_1, a, s'_1) \in \delta_{A_1} \land (s_2, a, s'_2) \in \delta_{A_2};$

- $a \notin Shared(A_1, A_2) \land ((s_1, a, s_1') \in \delta_{A_1} \land s_2 = s_2' \lor (s_2, a, s_2') \in \delta_{A_2} \land s_1 = s_1').$

Given tow behavioral contracts  $B_1$  and  $B_2$  where  $B_1 \cdot A = A_1$  and  $B_2 \cdot A = A_2$ ,  $B_1$  and  $B_2$  are composable if  $A_1$  and  $A_2$  are composable, and each  $a \in Shared(A_1, A_2) \cap \Sigma_{A_1}^m$  has the same signature in  $A_1$  and  $A_2$ . We deduce, from the composability of  $B_1$  and  $B_2$ , that for each  $a \in \Sigma_{A_i}^{\mathrm{m}} \cap Shared(A_1, A_2)$  for  $i \in \{1, 2\}$ , if  $\mathsf{R}_{A_i}(a), \mathsf{E}_{A_i}(a) \in \Sigma_{A_i}$  for all  $i \in \{1, 2\}$ , then  $R_{A_1}(a) = R_{A_2}(a) = r_a$ ,  $E_{A_1}(a) = E_{A_2}(a) = e_a$  and  $r_a, e_a \in Shared(A_1, A_2)$ . In the following definition, we provide the semantic compatibility conditions of input/output method actions shared between  $A_1$  and  $A_2$ .

**Definition 6.** Given an action  $a \in Shared(A_1, A_2) \cap \Sigma_{A_1}^m$ , for all  $(i, o) \in \Psi_{A_1}^i(a) \times \Psi_{A_1}^o(a)$ , if one of the following conditions holds, then the action a in  $B_1$  is semantically compatible with a in  $B_2$  i.e.  $SemComp_a(B_1, B_2)$ :

- $B_1.\mathcal{O}(a).P[i] \Rightarrow B_2.\mathcal{I}(a).P[i] \wedge B_1.\mathcal{O}(a).Q[i,o] \Leftarrow B_2.\mathcal{I}(a).Q[i,o] \text{ if } a \in \Sigma_{A_1}^{\mathrm{Om}}$ ;

- $B_1.\mathcal{I}(a).P[i] \Leftarrow B_2.\mathcal{O}(a).P[i] \land B_1.\mathcal{I}(a).Q[i,o] \Rightarrow B_2.\mathcal{O}(a).Q[i,o] \text{ if } a \in \Sigma_{A_1}^{\mathrm{Im}}.$

**Example 1.** According to our case study (cf. Section 3.3),  $B_o$ .  $\mathcal{A}$  and  $B_d$ .  $\mathcal{A}$  are composable. The set  $Shared(A_o, A_d)$  is defined by  $\{covReq, vmazReq, covered, uncovered, vmaz\}$ . Based on Table 1,  $SemComp_a(B_o, B_d)$  is true for a = covReq.

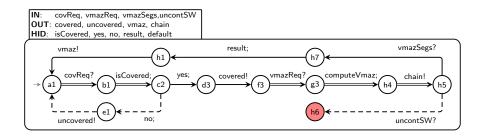

Figure 4: Interface automaton  $(B_d|B_m).\mathcal{A}$ .

**Definition 7.** Assume that  $B_1$  and  $B_2$  are composable, we define by  $B_1|B_2$ , the synchronized behavioral contract of  $B_1$  and  $B_2$  where:

- $(B_1|B_2).A$  is defined by  $A_1 \otimes A_2$  restricted to the set of reachable states from  $i_{A_{12}}$ ;

- $(B_1|B_2).\mathcal{I}$  is defined by:

- $B_1.\mathcal{I}(a)$  for all  $a \in \Sigma_{A_1}^{\operatorname{Im}} \setminus Shared(A_1, A_2)$ ;

- $-B_2.\mathcal{I}(a) \text{ for all } a \in \Sigma_{A_2}^{\operatorname{Im}} \setminus Shared(A_1, A_2);$

- $(B_1|B_2).\mathcal{O}$  is defined by:

- $B_1.\mathcal{O}(a)$  for all  $a \in \Sigma_{A_1}^{\mathrm{Om}} \setminus Shared(A_1, A_2);$   $B_2.\mathcal{O}(a)$  for all  $a \in \Sigma_{A_2}^{\mathrm{Om}} \setminus Shared(A_1, A_2).$

We denote  $(B_1|B_2).\mathcal{A}$  by  $A_{12}$  for simplicity. Deadlock states in  $A_{12}$  represent possible deadlocks during the communication between the components specified by  $B_1$  and  $B_2$  at the protocol and semantic levels. They are states  $s_1s_2$  such that (i) there exists at least  $a \in$  $Shared(A_1, A_2)$  enabled from  $s_1$  and not from  $s_2$  or inversely, or (ii) a is a method action enabled from  $s_1$  and  $s_2$  but, the condition  $SemComp_a(B_1, B_2)$  is falsified. The latter condition is essential for the calling component in order to define properly the output semantics of the method call with respect to the input semantics imposed by the environment: this allows the detection of the assumptions on components exchanged data as early as possible, and make the design more reliable.

**Definition 8.** The set of deadlock states  $Dead(A_1, A_2)$  in  $A_{12}$  is defined by  $\{s_1s_2 \in \Upsilon_{A_{12}} \mid (\exists a \in Shared(A_1, A_2). D_1(s_1s_2) \lor D_2(s_1s_2))\}$  where

$$\begin{split} D_1(s_1s_2) &\equiv (a \in \Sigma_{A_1}^{\rm O}(s_1) \land a \notin \Sigma_{A_2}^{\rm I}(s_2)) \lor (a \in \Sigma_{A_1}^{\rm Om}(s_1) \land a \in \Sigma_{A_2}^{\rm Im}(s_2) \land \neg SemComp_a(B_1, B_2)); \\ D_2(s_1s_2) &\equiv (a \in \Sigma_{A_2}^{\rm O}(s_2) \land a \notin \Sigma_{A_1}^{\rm I}(s_1)) \lor (a \in \Sigma_{A_2}^{\rm Om}(s_2) \land a \in \Sigma_{A_1}^{\rm Im}(s_1) \land \neg SemComp_a(B_1, B_2)). \end{split}$$

**Example 2.** According to Figure 3, the interface automata  $A_d$  and  $A_m$  are composable. Let us consider two composable behavioral contracts  $B_d$  and  $B_m$  where  $B_d$ .  $\mathcal{A} = A_d$  and  $B_m$ .  $\mathcal{A} = A_m$ . By supposing that actions is Covered and compute Vmaz are semantically compatible between  $B_d$  and  $B_m$ , the state h6 is the only deadlock state in  $(B_d|B_m)$ .  $\mathcal{A}$ : the exception action default  $\in \Sigma_{A_m}^e(6) \cap Shared(A_d, A_m)$  is not enabled from the state h in  $A_d$  (cf. Figure 4).

#### 4.2 Optimistic approach of composition

The incremental bottom-up design means that the compatibility checking between components can be performed for partial descriptions of the system. The optimistic approach of interface automata composition is closely consistent with the incremental design oncoming.

In this approach, the presence of deadlock states in  $A_{12}$  doesn't imply necessarily the incompatibility of  $B_1$  and  $B_2$ : the existence of a suitable environment E where  $E.\mathcal{A}$  provides good input steps and semantics for  $A_{12}$  and prevents reaching deadlock states, implies that they are *compatible*. E must satisfy the following conditions: (1) E and  $B_1|B_2$  are composable, (2)  $E.\mathcal{A}$  is non-empty interface automaton, (3)  $Dead(A_{12}, E.\mathcal{A}) = \emptyset$ , and (4) no state in the set  $Dead(A_1, A_2) \times \Upsilon_{E.\mathcal{A}}$  is reachable in  $((B_1|B_2)|E).\mathcal{A}$  [9].

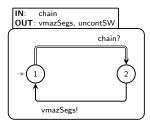

Figure 5: Interface automaton  $A_s$  of SRB.

**Example 3.** We assume that SRB does not throw the exception uncontSW if an uncontrolled switch is detected during chaining. The train VAMZ is limited by the switch position: for example, in Fig 1, if  $p_1$  is uncontrolled, VMAZ of T1 is bounded by the end of segment  $s_2$ . Let us consider a behavioral contract  $B_s$  for SRB composable with  $B_d|B_m$  where  $B_s.\mathcal{A} = A_s$  (cf. Figure 5) and  $SemComp_a(B_d|B_m, B_s)$  is valid for a = chain.  $B_s$  is a suitable environment for  $B_d|B_m$ . In  $((B_d|B_m)|B_s).\mathcal{A}$ , the states h61 and h62 are not reachable because from the state 2 in  $A_s$  the action uncontSW is not enabled. Consequently,  $B_d$  and  $B_m$  are compatible.

In the product  $A_{12}$ , all states  $s_1s_2$  from which deadlock states are autonomously reachable, are considered as incompatible and must be removed from  $A_{12}$ . No environment can prevent reaching deadlocks from those states as explained in Section 3.1. A state  $s_1s_2 \in \Upsilon_{A_{12}}$  is compatible in  $A_{12}$  if there is no state  $s_1's_2' \in Dead(A_1, A_2)$  autonomously reachable from  $s_1s_2$ . We denote, by  $Cmp(A_1, A_2)$ , the set of compatible states in  $A_{12}$ .  $B_1$  and  $B_2$  are compatible iff they are composable and  $i_{A_{12}} \in Cmp(A_1, A_2)$ . The interface automaton of the composition of two behavioral contracts is restricted to the compatible states of their synchronized product.

The composite interface automaton of the composition of two behavioral contracts is restricted to the set of compatible states of the interface automaton of their synchronization.

Figure 6: Interface automaton  $(B_d||B_m).\mathcal{A}$ .

**Definition 9.** The composition  $B_1||B_2$  of two compatible behavioral contracts  $B_1$  and  $B_2$  is defined by:

- $(B_1||B_2).\mathcal{A}$ , an interface automaton where  $\Upsilon_{(B_1||B_2).\mathcal{A}} = Cmp(A_1, A_2)$ ,  $\imath_{(B_1||B_2).\mathcal{A}} = \imath_{A_{12}}$ ,  $\Sigma^*_{(B_1||B_2).\mathcal{A}} = \Sigma^*_{A_{12}}$  for  $* \in \{I, O, H\}$ , and  $\delta_{(B_1||B_2).\mathcal{A}} = \{(s, a, s') \in \delta_{A_{12}} \mid s, s' \in \Upsilon_{(B_1||B_2).\mathcal{A}}\}$ ;

- $(B_1||B_2).\mathcal{I} = (B_1|B_2).\mathcal{I};$

- $(B_1||B_2).\mathcal{O} = (B_1|B_2).\mathcal{O}.$

**Example 4.** The interface automaton  $(B_d||B_m).\mathcal{A}$  (cf. Figure 6) is the restriction of  $(B_d|B_m).\mathcal{A}$  to the set of compatible states  $\Upsilon_{(B_d|B_m).\mathcal{A}} \setminus \{h6\}$ . Assume that  $A_d$  is not well-formed and do not expect to assign the return value of computeVmaz, h7 is a deadlock state in  $(B_d|B_m).\mathcal{A}$ . In this case, states h5, h4, and g3 are incompatible (the path between g3 and h7 is autonomous). The call of vmazReq leads inevitably to a deadlock for all possible environments.

The following property states the preservation of interface automata well-formedness by composition of behavioral contracts.

**Theorem 1.** If  $B_1$  is compatible with  $B_2$  and  $B_1$ . A and  $B_2$ . A are well-formed, then  $(B_1||B_2)$ . A is also well-formed.

Proof. We denote  $(B_1 \parallel B_2).\mathcal{A}$  by  $A'_{12}$ . Given  $s_1s_2 \in \Upsilon_{A'_{12}}$  and  $a \in \Sigma^{\mathrm{m}}_{A'_{12}}(s_1s_2)$  where  $\mathsf{R}_{A'_{12}}(a) \in \Sigma^{\mathrm{r}}_{A'_{12}}$ , we have to prove that, there is at least  $t_1t_2 \in \Upsilon_{A'_{12}}$ , where  $\mathsf{R}_{A'_{12}}(a) \in \Sigma_{A'_{12}}(t_1t_2)$ , reachable from  $Succ_{A'_{12}}(s_1s_2,a)$  by an autonomous exception-free run? We have the following assumptions: (i) if  $a \in \Sigma^{\mathrm{m}}_{A_1}(s_1)$  and  $\mathsf{R}_{A_1}(a) \in \Sigma^{\mathrm{r}}_{A_1}$ , then there is at least a state  $t_1 \in \Upsilon_{A_1}$  such that  $\mathsf{R}_{A_1}(a) \in \Sigma^{\mathrm{r}}_{A_1}(t_1)$  reachable from  $Succ_{A_1}(s_1,a)$  by an autonomous exception-free run  $\sigma_1 = s_1^1[a_1^1]...s_1^{k-1}[a_1^{k-1}]s_1^k$  where  $s_1^1 = Succ_{A_1}(s_1,a)$  and  $s_1^k = t_1$ ; (ii) if  $a \in \Sigma^{\mathrm{m}}_{A_2}(s_2)$  and  $\mathsf{R}_{A_2}(a) \in \Sigma^{\mathrm{r}}_{A_2}$ , then there is at least a state  $t_2 \in \Upsilon_{A_2}$  such that  $\mathsf{R}_{A_2}(a) \in \Sigma^{\mathrm{r}}_{A_2}(t_2)$  reachable from  $Succ_{A_2}(s_2,a)$  by an autonomous exception-free run  $\sigma_2 = s_2^1[a_2^1]...s_2^{l-1}[a_2^{l-1}]s_2^l$  where  $s_2^1 = Succ_{A_2}(s_2,a)$  and  $s_2^l = t_2$ .

- (1) If  $a \in \Sigma_{A_1}^{\mathrm{m}} \cap Shared(A_1, A_2)$ , we have  $\mathsf{R}_{A_1}(a) = \mathsf{R}_{A_2}(a) = r_a$  since  $B_1$  and  $B_2$  are composable. The transitions labeled by a enabled from  $s_1$  and  $s_2$  synchronize if  $SemComp_a(A_1, A_2)$ :

- (1.1) if  $r_a \in Shared(A_1, A_2)$ , then the transitions enabeled from  $s_1^k$  and  $s_2^l$  labeled by  $r_a$  synchronize. If  $(\Sigma_{A_1}\langle\sigma_1\rangle \cup \Sigma_{A_2}\langle\sigma_2\rangle) \cap Shared(A_1, A_2) = \emptyset$ , then the transitions of  $\sigma_1$  and  $\sigma_2$  are interleaved asynchronously and produce autonomous exception-free runs between  $s_1^1 s_2^1$  and  $s_1^k s_2^l$ . If  $(\Sigma_{A_1}\langle\sigma_1\rangle \cup \Sigma_{A_2}\langle\sigma_2\rangle) \cap Shared(A_1, A_2) \neq \emptyset$ , then all transitions labeled by shared actions in  $\sigma_1$  and  $\sigma_2$  synchronize and produce autonomous exception-free runs between  $s_1^1 s_2^1$  and  $s_1^k s_2^l$ . For each  $\sigma$  from those runs, if  $\Upsilon_{A_{12}}\langle\sigma\rangle \cup \{Succ_{A_{12}}(s_1^k s_2^l, r_a)\} \subseteq Cmp(A_1, A_2)$ , then  $\sigma$  remains in  $A'_{12}$  if  $s_1s_2 \in Cmp(A_1, A_2)$ . Otherwise,  $\sigma$  is removed in  $A'_{12}$  and  $s_1s_2 \notin \Upsilon_{A'_{12}}$ .

(1.2) if  $r_a \notin Shared(A_1, A_2)$  and  $a \in \Sigma_{A_1}^{Im}$ , then the transition enabling  $r_a$  as output action is interleaved form  $s_1^k t_2$  where  $t_2$  is reachable from  $s_2$  in  $A_2$ . If  $\Sigma_{A_1} \langle \sigma_1 \rangle \cap Shared(A_1, A_2) = \emptyset$ , the transitions of  $\sigma_1$  are interleaved and among the produced runs, we distinguish the autonomous exception-free run  $\sigma = s_1^1 t_2 [a_1^1] ... s_1^{k-1} t_2 [a_1^{k-1}] s_1^k t_2$  in  $A_{12}$  where  $t_2 = s_2^1$ : if  $\Upsilon_{A_{12}} \langle \sigma \rangle \cup \{Succ_{A_{12}}(s_1^k t_2, r_a)\} \subseteq Cmp(A_1, A_2)$ , then  $\sigma$  remains in  $A'_{12}$  if  $s_1 s_2 \in Cmp(A_1, A_2)$ . Otherwise,  $\sigma$  is removed in  $A'_{12}$  and  $s_1 s_2 \notin \Upsilon_{A'_{12}}$ . If  $\Sigma_{A_1} \langle \sigma_1 \rangle \cap Shared(A_1, A_2) \neq \emptyset$ , then all transitions labeled by shared actions of  $\sigma_1$  synchronize with their equivalents in  $A_2$  if they exist: either a deadlock state is hit and then  $s_1 s_2 \notin \Upsilon_{A'_{12}}$ , or there is an autonomous exception-free run  $\sigma$  between  $s_1^1 s_2^1$  and  $s_1^k t_2$  containing only actions in  $\Sigma_{A_1} \langle \sigma_1 \rangle$  where  $t_2$  is reachable from  $s_2$  in  $A_2$ . In the latter case, if  $\Upsilon_{A_{12}} \langle \sigma \rangle \cup \{Succ_{A_{12}}(s_1^k t_2, r_a)\} \subseteq Cmp(A_1, A_2)$ , then  $\sigma$  remains in  $A'_{12}$  if  $s_1 s_2 \in Cmp(A_1, A_2)$ . Otherwise,  $\sigma$  is removed in  $A'_{12}$  and  $a_1 s_2 \notin \Upsilon_{A'_{12}}$ . The same reasoning is adapted if  $a \in \Sigma_{A_2}^{Im}$ .

Finally, if  $\neg SemComp_a(A_1, A_2)$ ,  $s_1s_2$  is deadlock in  $A_{12}$  and removed in  $A'_{12}$ .

(2) If  $a \in \Sigma_{A_1}^m \setminus Shared(A_1, A_2)$ , we have  $\mathsf{R}_{A_1}(a) = r_a \not\in Shared(A_1, A_2)$ . The transition enabled from  $s_1^k$  labeled by  $r_a$  and that enabled from  $s_1$  labeled by a are interleaved in  $A_{12}$ . If  $\Sigma_{A_1} \langle \sigma_1 \rangle \cap Shared(A_1, A_2) = \emptyset$ , the transitions of  $\sigma_1$  are interleaved and among the produced runs, we distinguish the autonomous exception-free run  $\sigma = s_1t_2[a]s_1^1t_2[a_1^1]...s_1^{k-1}t_2[a_1^{k-1}]s_1^kt_2$  in  $A_{12}$  where  $s_1^1t_2 = Succ(s_1t_2, a)$  and  $s_1t_2$  is reachable in  $A_{12}$ : if  $\Upsilon_{A_{12}} \langle \sigma \rangle \cup Succ_{A_{12}}(s_1^kt_2, r_a) \subseteq Cmp(A_1, A_2)$ , then  $\sigma$  remains in  $A'_{12}$  if  $s_1t_2 \in Cmp(A_1, A_2)$ . Otherwise,  $\sigma$  is removed in  $A'_{12}$  and  $(s_1t_2, a, s_1^1t_2) \not\in \delta_{A'_{12}}$ . If  $\Sigma_{A_1} \langle \sigma_1 \rangle \cap Shared(A_1, A_2) \neq \emptyset$ , then all transitions labeled by shared actions of  $\sigma_1$  synchronize with their equivalents in  $A_2$  if they exist: either a deadlock state is hit and then all reachable states  $s_1t_2$  in  $A_{12}$  are removed in  $A'_{12}$ , or there is an autonomous exception-free run  $\sigma$  between all  $s_1t_2$  reachable in  $A_{12}$  and  $s_1^kt_2$  containing only actions in  $\{a\}\cup\Sigma_{A_1}\langle\sigma_1\rangle$ . In the latter case, if  $\Upsilon_{A_{12}}\langle\sigma\rangle\cup\{Succ_{A_{12}}(s_1^kt_2, r_a)\}\subseteq Cmp(A_1, A_2)$ , then  $\sigma$  remains in  $A'_{12}$  for all  $s_1t_2\in Cmp(A_1, A_2)$ . Otherwise,  $\sigma$  is removed in  $A'_{12}$  and  $(s_1t_2, a, s_1^1t_2)\not\in\delta_{A'_{12}}$ . The same reasoning is adapted if  $a\in\Sigma_{A_2}^{Im}$ . Consequently, from proofs (1) and (2), we can deduce that  $(B_1||B_2).A$  is well-formed.

The following theorem is in the heart of incremental design of component-based systems. It is a straightforward generalization of interface automata associativity [9] to behavioral contracts.

**Theorem 2.** The composition operation  $\parallel$  between compatible behavioral contracts is commutative and associative.

Proof. This proof is adapted from [4]. Let us consider three behavioral contracts  $B_1$ ,  $B_2$ , and  $B_3$  mutually composable and compatible. The proof of commutativity is trivial. It is also easy to check that  $((B_1||B_2)||B_3).\mathcal{I} = (B_1||(B_2||B_3)).\mathcal{I} = ((B_1||B_3)||B_2).\mathcal{I}$  and  $((B_1||B_2)||B_3).\mathcal{O} = (B_1||(B_2||B_3)).\mathcal{O} = ((B_1||B_3)||B_2).\mathcal{O}$ . The proof of associativity is mainly required at the level of interface automata. We denote  $B_1.\mathcal{A}$ ,  $B_2.\mathcal{A}$ , and  $B_3.\mathcal{A}$  resp. by  $A_1$ ,  $A_2$ , and  $A_3$ . We recall that the synchronization  $\otimes$  of interface automata is a commutative and associative operation (proof sketch in [7]): we have  $(A_1 \otimes A_2) \otimes A_3 = A_1 \otimes (A_2 \otimes A_3) = (A_1 \otimes A_3) \otimes A_2 = A_1 \otimes A_2 \otimes A_3$  (denoted  $A_{123}$ ). We consider projections  $A_i \otimes A_j$  (denoted  $A_{ij}$ ) of  $A_{123}$  for  $i, j \in \{1, 2, 3\}$  and  $i \neq j$ . A state  $s_1s_2s_3$  is a deadlock state in  $A_{123}$  if there is a deadlock state in one of the projections  $A_{ij}$ . A state  $s_1s_2s_3$  is incompatible in  $A_{123}$  if there is a deadlock state  $d_1d_2d_3$  in  $A_{123}$  autonomously reachable from  $s_1s_2s_3$ . For  $l \geq 0$ , a state  $s_1s_2s_3$  is l-incompatible if there is a deadlock state  $d_1d_2d_3$  autonomously reachable from  $s_1s_2s_3$  by enabling at most l transitions.

It is sufficient to show that  $(B_1||B_2||B_3)$ .  $\mathcal{A}$  (denoted  $A'_{123}$ ), for any insertion of parentheses, is the associative product  $A_{123}$  by removing incompatible states. We follow two steps: (1) we

demonstrate that a state  $s_1s_2s_3$  is incompatible in  $A_{123}$  if there is a state  $s_is_j$  incompatible in one of its projection  $A_{ij}$ ; (2) we demonstrate that if there are transitions labeled by non-autonomous actions  $(\Sigma_{A_{ij}}^{\text{Im}} \cup (\Sigma_{A_{ij}}^{\text{I}} \cap \Sigma_{A_{ij}}^{\text{e}}))$  reachable autonomously from  $s_is_j$  and removed in  $(B_i||B_j).\mathcal{A}$  (denoted  $A'_{ij}$ ), then in the product  $A_{123}$  without those transitions, there is always an autonomous run starting from  $s_1s_2s_3$  reaching a deadlock state.

- (1) Given a state  $s_1s_2s_3$  in  $A_{123}$  and a projection  $s_is_j$  of  $s_1s_2s_3$  k-incompatible in the product  $A_{ij}$ , we show that  $s_1s_2s_3$  is l'-incompatible with  $l' \leq l$  in  $A_{123}$ . Given  $\sigma$  the smallest autonomous run between  $s_is_j$  and a deadlock state  $d_id_j$  in  $A_{ij}$ . The proof is by induction: (base case 1) if  $s_is_j \in Dead(A_i, A_j)$ , then  $s_1s_2s_3$  is a deadlock state (0-incompatible in  $A_{123}$ ); (base case 2) if  $s_is_j \in Comp(A_i, A_j)$  and  $s_1s_2s_3 \in Dead(A_{ij}, A_k)$  for  $k \in \{1, 2, 3\} \setminus \{i, j\}$  (0-incompatible in  $A_{123}$ ); (step case) if the first transition of  $\sigma$  is labeled by an autonomous action, synchronized or interleaved in  $A_{123}$ , then the successor state  $t_1t_2t_3$  of  $s_1s_2s_3$  by enabling this action, is (l-1)-incompatible. The proof is iterated inductively until reaching a deadlock state  $d_1d_2d_3$  (one of the base cases).

- (2) Given a state  $s = s_1 s_2 s_3$  incompatible in  $A_{123}$ , we assume that there are transitions labeled by non-autonomous actions  $a \in \Sigma_{A_{ij}}^{\operatorname{Im}} \cup \Sigma_{A_{ij}}^{\operatorname{Ie}}$ , reachable from  $s_i s_j$  in a sub-product  $A_{ij}$  and removed in  $A'_{ij}$  and  $A'_{123}$ . Only transitions (t, a, v) where a is hidden in  $A_{123}$  and their projections onto  $A_{ij}$  are transitions  $(t_i t_j, a, v_i v_j)$  where a is non-autonomous and synchronized by its corresponding output action in  $A_k$  for  $k \in \{1, 2, 3\} \setminus \{i, j\}$ , can be removed in this way. Once (t, a, v) is removed from  $A_{123}$ , the input non-autonomous action is no longer enabled from  $t_i t_j$  because interface automata are deterministic. Consequently, the state  $t \in Dead(A_{ij}, A_k)$ . Hence, after removing (t, a, v) from  $A_{123}$  there is always an autonomous run between s and a deadlock state, especially t.

The compatibility check procedure of two behavioral contracts is similar to that described in [9] for interface automata, by considering the semantic layer of actions and the new definition of autonomous runs. The linear complexity of the proposed algorithm is extended by the satisfiability decision problems of the semantic compatibility conditions of shared method actions. The original algorithm becomes a semi-algorithm on account of the various satisfiability problems which are either decidable (propositional logic) or not (arithmetic, etc).

#### 5 Refinement

Refinement embodies with more details an abstract specification of a component in a more concrete one. It guarantees a safe substitutability of an abstract version of a component by a refined one. We propose a refinement approach for behavioral contracts at the protocol and semantic levels suitable to the object-oriented context. We start by introducing refinement at the level of interface automata.

#### 5.1 Expanding simulation

The original refinement approach of interface automata is contravariant [9]: a refined version of a component must accept the same or more inputs and provide the same or fewer outputs, than the abstraction. It is based on an alternating simulation relation [5]: an interface automaton A' refines an interface automaton A if each input event of A can be simulated by A', and each output event of A' can be simulated by A. At the protocol level in OOCBD, refinement ensures that a refined specification of component (i) may contain more details about the common provided

methods with the abstract one, which are output and hidden method calls encapsulated in their implementations, and (ii) may provide more methods than the abstract one. In order to satisfy the previous requirements, we define refinement as a *covariant expanding simulation* relation between interface automata: A' refines A if A' accepts (resp. issues) more inputs (resp. outputs) than A, and each input, output, or local event of A is simulated in A' by the same one followed or preceded by other events.

To formalize this relation, we define the *closure* set  $Clos_A(s, \Sigma)$  of  $s \in \Upsilon_A$  under actions in  $\Sigma \subseteq \Sigma_A$  by the largest set  $\Upsilon \subseteq \Upsilon_A$  such that  $s \in \Upsilon$  and if  $t \in \Upsilon$ ,  $t' = Succ_A(t, a)$ , and  $a \in \Sigma$ , then  $t' \in \Upsilon$  i.e.  $Clos_A(s, \Sigma)$  contains states reachable from the state s by enabling actions of  $\Sigma$ .

**Definition 10.** Given two interface automata A and A', a binary relation  $\gtrsim \subseteq \Upsilon_A \times \Upsilon_{A'}$  is an expanding simulation from A to A' iff for all states  $s \in \Upsilon_A$  and  $s' \in \Upsilon_{A'}$  such that  $s \gtrsim s'$ , for all  $a \in \Sigma_A(s)$  and  $t = Succ_A(s, a)$ , the following conditions hold:

- (1) if  $a \in \Sigma_A^{\text{Om}}(s) \cup \Sigma_A^{\text{Ir}}(s) \cup \Sigma_A^{\text{Ie}}(s)$ , then  $a \in \Sigma_{A'}(s')$  and  $t \gtrsim t'$  for  $t' = Succ_{A'}(s', a)$ ;

- (2) if  $a \in \Sigma_A^{\operatorname{Im}}(s) \cup \Sigma_A^{\operatorname{Hm}}(s)$ , then  $a \in \Sigma_{A'}(s')$ , and there is a set  $\Sigma \subseteq ((\Sigma_{A'}^{\operatorname{aut}} \setminus \Sigma_{A'}^{\operatorname{Or}}) \setminus \Sigma_{A'}^{\operatorname{e}}) \setminus \Sigma_A$  and a state  $t' \in Clos_{A'}(Succ_A(s',a),\Sigma)$  such that  $t \gtrsim t'$ ;

- (3) if  $a \in \Sigma_A^{\text{Or}}(s) \cup \Sigma_A^{\text{Hr}}(s)$ , then there is a state  $v' \in Clos_{A'}(s', \Sigma)$  such that  $a \in \Sigma_{A'}(v')$ ,  $\Sigma = ((\Sigma_{A'}^{\text{aut}} \setminus \Sigma_{A'}^{\text{Or}}) \setminus \Sigma_{A}, \text{ and } t \gtrsim t' \text{ for } t' = Succ_{A'}(v', a);$

- (4) if  $a \in \Sigma_A^{\text{Oe}}(s) \cup \Sigma_A^{\text{He}}(s)$ , then there is a state  $v' \in Clos_{A'}(s', \Sigma)$  such that  $a \in \Sigma_{A'}(v')$ ,  $\Sigma = ((\Sigma_{A'}^{\text{out}} \setminus (\Sigma_{A'}^{\text{Oe}} \cup \Sigma_{A'}^{\text{Or}})) \cup \Sigma_{A'}^{\text{Ie}}) \setminus \Sigma_A$ , and  $t \gtrsim t'$  for  $t' = Succ_{A'}(v', a)$ .

Our expanding simulation relation pinpoints where refinement details are added in the abstract version of an interface automaton. Condition (1) of Definition 10 states that every transition labeled by an output method action, or an input return or exception action must be matched by a transition labeled by the same action in A'. Method calls sent to the environment, the reception of their return values, and catching their thrown exceptions, cannot be refined.

Condition (2) states that every transition labeled by an input or hidden method action in A is matched in A' by a transition labeled by the same action followed by zero or more transitions labeled by a "subset" of new autonomous non-exception actions in  $((\Sigma_{A'}^{\text{aut}} \setminus \Sigma_{A'}^{\text{Or}}) \setminus \Sigma_{A}) \setminus \Sigma_{A}$ . A provided public method in the abstraction of a component can be refined by adding to its body new private or public method calls. In addition, since providing private methods is not specified by actions in interface automata (cf. Section 3), our simulation relation allows adding refinement details about private methods after their calls.

Condition (3) states that every transition labeled by an output or hidden return action a in A is matched in A' by zero or more transitions labeled by new autonomous non-exception actions in  $((\Sigma_{A'}^{\text{aut}} \setminus \Sigma_{A'}^{\text{Or}}) \setminus \Sigma_{A'}^{\text{e}}) \setminus \Sigma_{A}$  followed by a transition labeled by a. The return event of a private or public provided method in the abstraction is computed based on the return values of new calls of private or public methods added as refinement details.

Condition (4) states that every transition labeled by an output or hidden exception action a in A is matched in A' by zero or more transitions labeled either by new autonomous and hidden exception actions in  $(\Sigma_{A'}^{\text{aut}} \setminus (\Sigma_{A'}^{\text{Oe}} \cup \Sigma_{A'}^{\text{Or}})) \setminus \Sigma_A$ , or by new input exception actions in  $\Sigma_{A'}^{\text{Ie}} \setminus \Sigma_A$ , followed by a transition labeled by a. The exception events of a provided private or public method in the abstraction is the propagation of catching exception events of new calls of private or public methods added as refinement details.

From the previous definition, we establish the refinement relation between interface automata as follows.

**Definition 11.** A' refines A, denoted  $A \succeq A'$ , iff

- (1)  $\Sigma_A^{\mathrm{I}} \subseteq \Sigma_{A'}^{\mathrm{I}}$ ,  $\Sigma_A^{\mathrm{O}} \subseteq \Sigma_{A'}^{\mathrm{O}}$ , and  $\Sigma_A^{\mathrm{H}} \subseteq \Sigma_{A'}^{\mathrm{H}}$ ;

- (2) there is an expanding simulation  $\gtrsim$  from A to A' such that  $\iota_A \gtrsim \iota_{A'}$ .

A trivial consequence of condition (1) of Definition 11 is covariance from A to A' on method, return, and exception actions:  $\Sigma_A^{\rm m} \subseteq \Sigma_{A'}^{\rm m}$ ,  $\Sigma_A^{\rm r} \subseteq \Sigma_{A'}^{\rm r}$ , and  $\Sigma_A^{\rm e} \subseteq \Sigma_{A'}^{\rm e}$ . Condition (2) requires the existence of an expanding simulation from A to A' relating their initial states  $i_A$  and  $i_{A'}$  and recursively propagated to their successor states.

We infer from conditions of Definition 10 that extra new input method actions are not considered as refinement details by the expanding simulation relation, which obviously makes sense. By cons, it allows the extension of interface automata by adding protocols related to additional methods provided by a component extended interface. They can be enabled for example separately from the initial state.

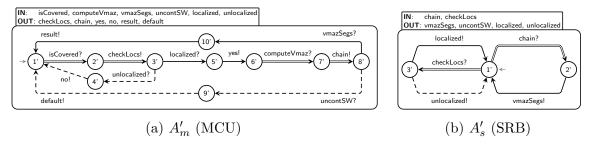

Figure 7: Extended version of SubRouteBuilder.

Figure 8: Refined interface automata of MCU and SRB.

Example 5. After receiving a train coverage request, MCU asks SRB to check if tel and hel are really on segments ts and hs respectively by calling the method checkLocs, presented in Figure 8(left), as a new service of the class SubRouteBuilder and the interface RouteBuilder. If true, SRB responds by sending the status (localized), and MCU in turn, responds OBD, via DEU, by returning yes if the train is completely (or partially) included in its coverage area. Otherwise, SRB throws the exception unlocalized to MCU, which in turn, propagates it to DEU by throwing the exception no. In  $A'_m$  shown in Figure 8(a), the method call checkLocs! is encapsulated in the runs describing the body of the method isCovered provided by MCU. Providing the public method checkLocs is equally depicted in the interface automaton  $A'_s$  shown in Figure 8(b) by a new input method action enabled separately from  $i_{A'_s} = 1'$ .  $A'_m$  and  $A'_s$  resp. refine  $A_m$  and  $A_s$  (shown resp. in Figure 3(c) and Figure 5): condition (1) of Definition 11 is met by  $A'_m$  and  $A_m$ , as well by  $A'_s$  and  $A_s$ , and there are two expanding simulations  $a_s = a_s = a_s + a_s$

#### 5.2 Semantic substitutability

The semantic substitutability of method actions between an abstract and a concrete versions of a component behavioral contract is based on behavioral sub-typing principles introduced in [6, 13]: in the refined specification, a common provided method must have a weaker precondition, a stronger termination postcondition, and does not introduce exceptions by supplying a stronger exception condition, than the abstraction. Inversely, a common method call must have a stronger precondition and a weaker postcondition than the abstraction. Given tow behavioral contracts B and B', we denote B.A by A and B'.A by A'.

**Definition 12.** Given an action  $a \in \Sigma_A^{\operatorname{Im}}$ ,  $B'.\mathcal{I}(a) = (P'_a, B'_a, Q'_a, E'_a)$  substitutes  $B.\mathcal{I}(a) = (P_a, B_a, Q_a, E_a)$  i.e.  $SemSub_a(B, B')$ , iff for all  $(i, f, o) \in \Psi_A^i(a) \times \Lambda_A(a) \times \Psi_A^o(a)$ , the following conditions hold:

- (1)  $P_a[i] \Rightarrow P_a'[i], Q_a[i, f, o] \Leftarrow Q_a'[i, f, o], \text{ and } E_a[i, f, o] \Leftarrow E_a'[i, f, o];$

- (2)  $P_a[i] \wedge S'_a[i, f, o] \Rightarrow S_a[i, f, o].$

Given an action  $b \in \Sigma_A^{\mathrm{Om}}$ ,  $B'.\mathcal{O}(b) = (P_b', Q_b')$  substitutes  $B.\mathcal{O}(b) = (P_b, Q_b)$  i.e.  $SemSub_b(B, B')$ , iff for all  $(i, o) \in \Psi_A^{\mathrm{i}}(b) \times \Psi_A^{\mathrm{o}}(b)$ , the following condition holds:

(3)  $P_b[i] \Leftarrow P_b'[i]$  and  $Q_b[i, o] \Rightarrow Q_b'[i, o]$ .

The following property is evident based on definitions 5 and 12. The correctness, termination and exception preservation is what we expect for a correct refinement at the level of provided methods semantics: if a refined semantics of a provided method satisfies the condition (2) of Definition 12, then any property holding for a specification S under the precondition in the abstract method semantics, holds also for the refined specification S' under the same precondition, and thus S' may be used instead of S [14, 3].

**Property 1.** Given  $a \in \Sigma_A^{\operatorname{Im}}$  where  $SemSub_a(B, B')$ , for all  $(i, f, o) \in \Psi_A^i(a) \times \Lambda_A(a) \times \Psi_A^o(a)$ ,

- $P_a[i] \wedge S'_a[i, f, o] \Rightarrow Q_a[i, f, o]$  if a is correct with respect to  $B.\mathcal{I}(a)$ ;

- $P_a[i] \wedge S'_a[i, f, o] \Rightarrow Q_a[i, f, o] \wedge \neg E_a[i, f, o]$  if a terminates with respect to  $B.\mathcal{I}(a)$ ;

- $P_a[i] \wedge S'_a[i, f, o] \Rightarrow E_a[i, f, o]$  if a throws exceptions with respect to  $B.\mathcal{I}(a)$ .

Property 2 says that the semantic compatibility validity of shared observable method actions, between a component behavioral contracts and its environment, is preserved by the semantic substitutability. The property is obvious based on Definition 6 and conditions (1) and (3) of Definition 12. Given a behavioral contract E, we set  $E \cdot A = A_E$ .

**Property 2.** Given an action  $a \in Shared(A, A_E) \cap \Sigma_A^m$ , for all  $(i, o) \in \Psi_A^i(a) \times \Psi_A^o(a)$ , if  $SemSub_a(B, B')$ , then  $SemComp_a(B, E) = SemComp_a(B', E)$ .

Finally, we can define refinement of behavioral contracts based on refinement of interface automata and the semantic substitutability of observable method actions.

**Definition 13.** B' refines B ( $B \supseteq B'$ ) iff  $A \succeq A'$  and for all  $a \in \Sigma_A^{\operatorname{Im}} \cup \Sigma_A^{\operatorname{Om}}$ ,  $SemSub_a(B, B')$ .

#### 5.3 Refinement properties

In this subsection, we present the properties and requirements under which our refinement approach allows independent implementability of components using their behavioral contracts.

#### Reflexivity and transitivity

Lemma 3 states that the expanding simulation between interface automata is a transitive relation. This result is necessary to prove that the refinement relation  $\supseteq$  is a preorder (Theorem 4) *i.e.* a behavioral contract can be gradually refined in several steps while remaining consistent with its abstract specification.

**Lemma 3.** given three interface automata A, A', and A'', and two expanding simulations  $\gtrsim' \subseteq \Upsilon_A \times \Upsilon_{A'}$  and  $\gtrsim'' \subseteq \Upsilon_{A'} \times \Upsilon_{A''}$ , then the composite relation  $\gtrsim'' \circ \gtrsim' \subseteq \Upsilon_A \times \Upsilon_{A''}$  is an expanding simulation.

Proof. We set some notations. Given an interface automaton M, a state  $s \in \Upsilon_M$ , and a set of actions  $\Sigma \subseteq \Sigma_M$ , we define recursively  $Clos_M^k(s,\Sigma)$  by:  $Clos_M^0(s,\Sigma) = \{s\}$  and  $Clos_M^k(s,\Sigma) = Clos_M^{k-1}(s,\Sigma) \cup \{t = Succ_M(s,a) \mid a \in \Sigma \land s \in Clos_M^{k-1}(s,\Sigma)\}$  for k > 0. We prove that  $\geq'' \circ \geq' = \{ss'' \in \Upsilon_A \times \Upsilon_{A''} \mid (\exists s' \in \Upsilon_{A'} \mid s \geq' s' \geq'' s'')\}$  is an expanding simulation. For all  $s \in \Upsilon_A$ , based on Definition 10, we state the following properties for all  $a \in \Sigma_A(s)$  and  $t = Succ_A(s,a)$ :

- (1) if  $a \in \Sigma_A^{\text{Om}}(s) \cup \Sigma_A^{\text{Ir}}(s) \cup \Sigma_A^{\text{Ie}}(s)$ ,  $a \in \Sigma_{A'}(s')$ ,  $a \in \Sigma_{A''}(s'')$ , and  $t \gtrsim' t' \gtrsim'' t''$  for  $t' = Succ_{A'}(s', a)$  and  $t'' = Succ_{A''}(s'', a)$ , that is  $t \gtrsim'' \circ \gtrsim' t''$ ;

- (2) if  $a \in \Sigma_A^{\operatorname{Im}}(s) \cup \Sigma_A^{\operatorname{Hm}}(s)$ , then  $a \in \Sigma_{A'}(s')$ , and there is a set  $\Sigma' \subseteq ((\Sigma_{A'}^{\operatorname{aut}} \setminus \Sigma_{A'}^{\operatorname{Or}}) \setminus \Sigma_A) \setminus \Sigma_A$  and a state  $t' \in Clos_{A'}(Succ_{A'}(s',a),\Sigma')$  such that  $t \gtrsim' t'$ . We have to prove that  $a \in \Sigma_{A''}(s'')$ , and there is a set  $\Sigma \subseteq ((\Sigma_{A''}^{\operatorname{aut}} \setminus \Sigma_{A''}^{\operatorname{Or}}) \setminus \Sigma_A) \setminus \Sigma_A$  and a state  $t'' \in Clos_{A''}(Succ_{A''}(s'',a),\Sigma)$  such that  $t \gtrsim' t' \gtrsim'' t''$ ? We consider  $Clos_{A'}^k(Succ_{A'}(s',a),\Sigma') \subseteq Clos_{A'}(Succ_{A'}(s',a),\Sigma')$  where k is the first natural such that  $t' \in Clos_{A'}^k(Succ_{A'}(s',a),\Sigma')$ . We define the states  $s_i' \in Clos_{A'}^k(Succ_{A'}(s',a),\Sigma') \cup \{s'\}$  inductively on  $0 \le i \le k+1$ :  $s_0' = s$ ,  $s_1' = Succ_{A'}(s_0',a)$ ,  $s_i' \in Clos_{A'}^{i-1}(s_1',\Sigma') \setminus Clos_{A'}^{i-2}(s_1',\Sigma')$  for i > 1. We define  $s_i''$  and  $\Upsilon_i''$  inductively on i:

- (2.1) i = 0:  $s_0'' = s''$  (we recall that  $s_0' \gtrsim'' s_0''$ );  $\Upsilon_0'' = \{s_0''\}$ ;

- $(2.2) \ i=1: \ a\in \Sigma_{A''}(s_0''), \ \text{there is a set} \ \Sigma_0''\subseteq ((\Sigma_{A''}^{\mathrm{aut}}\setminus\Sigma_{A''}^{\mathrm{Or}})\setminus\Sigma_{A''}^{\mathrm{e}})\setminus\Sigma_{A'} \ \text{and a state} \ s_1''\in Clos_{A''}(Succ_{A''}(s_0'',a),\Sigma_0'') \ \text{such that} \ s_1'\cong S_1''; \ \Upsilon_1''=\Upsilon_0''\cup Clos_{A''}(Succ_{A''}(s_0'',a),\Sigma_0'');$

- (2.3) i > 1: for all  $b_{i-1} \in \Sigma_{A'}(s'_{i-1}) \cap \Sigma'$  and  $s'_i = Succ_{A'}(s'_{i-1}, b_{i-1})$ , we have three cases:

- (2.3.1) if  $b_{i-1} \in \Sigma_{A'}^{\mathrm{Om}}(s'_{i-1}) \cup \Sigma_{A'}^{\mathrm{Ir}}(s'_{i-1})$ , then  $b_{i-1} \in \Sigma_{A''}(s''_{i-1})$  and  $s'_i \gtrsim'' s''_i$  where the state  $s''_i = Succ_{A''}(s''_{i-1}, b_{i-1}); \ \Upsilon''_i = \Upsilon''_{i-1} \cup \{s''_i = Succ_{A''}(s''_{i-1}, b_{i-1}) \mid b_{i-1} \in (\Sigma_{A'}^{\mathrm{Om}}(s''_{i-1}) \cup \Sigma_{A'}^{\mathrm{Ir}}(s''_{i-1})) \cap \Sigma'\};$

- $(2.3.2) \text{ if } b_{i-1} \in \Sigma_{A''}^{\text{Hm}}(s'_{i-1}), \ b_{i-1} \in \Sigma_{A''}(s''_{i-1}), \text{ and there is } \Sigma''_{i-1} \subseteq ((\Sigma_{A''}^{\text{aut}} \setminus \Sigma_{A''}^{\text{Or}}) \setminus \Sigma_{A'}^{\text{or}}) \setminus \Sigma_{A'}^{\text{or}} \text{ and } s''_{i} \in Clos_{A''}(Succ_{A''}(s''_{i-1}, b_{i-1}), \Sigma''_{i-1}) \text{ such that } s'_{i} \gtrsim'' s''_{i}; \Upsilon''_{i} = \Upsilon''_{i-1} \cup (\bigcup_{\phi} Clos_{A''}(Succ_{A''}(s''_{i-1}, b_{i-1}), \Sigma''_{i-1})) \text{ where } \phi \equiv b_{i-1} \in \Sigma_{A'}^{\text{Hm}}(s'_{i-1}) \cap \Sigma';$

- $(2.3.3) \text{ if } b_{i-1} \in \Sigma_{A'}^{\operatorname{Hr}}(s'_{i-1}), \text{ there is a state } v''_{i-1} \in \operatorname{Clos}_{A''}(s''_{i-1}, \Sigma''_{i-1}) \text{ such that } b_{i-1} \in \Sigma_{A''}(v''_{i-1}), \Sigma''_{i-1} = ((\Sigma_{A''}^{\operatorname{aut}} \setminus \Sigma_{A''}^{\operatorname{Or}}) \setminus \Sigma_{A''}) \setminus \Sigma_{A'}, \text{ and } s'_{i} \gtrsim'' s''_{i} \text{ for the state } s''_{i} = \operatorname{Succ}_{A''}(v''_{i-1}, b_{i-1}); \Upsilon''_{i} = \Upsilon''_{i-1} \cup (\bigcup_{\phi} \operatorname{Clos}_{A''}(s''_{i-1}, \Sigma''_{i-1})) \cup \{\operatorname{Succ}_{A''}(v''_{i-1}, b_{i-1}) \mid (\forall v''_{i-1} \mid \phi)\} \text{ where } \phi \equiv b_{i-1} \in \Sigma_{A'}^{\operatorname{Hr}}(s'_{i-1}) \cap \Sigma'.$

We deduce from (2.1) and (2.2) that  $a \in \Sigma_{A''}(s'')$ . Given  $s'_k \in Clos^k_{A'}(Succ_{A'}(s',a),\Sigma')$  where  $s'_k = t'$ , according to (2.3), there is a set  $\Upsilon''_{k+1} \subseteq Clos_{A''}(Succ_{A''}(s'',a),\Sigma)$  where  $\Sigma \subseteq ((\Sigma^{\text{aut}}_{A''} \setminus \Sigma^{\text{Or}}_{A''}) \setminus \Sigma^{\text{e}}_{A''}) \setminus \Sigma_A$  and  $t'' \in \Upsilon''_{k+1}$  such that  $t \gtrsim' t' \gtrsim'' t''$ , that is  $t \gtrsim'' \circ \gtrsim' t''$ .

(3) if  $a \in \Sigma_A^{\text{Or}}(s) \cup \Sigma_A^{\text{Hr}}(s)$ , there is  $v' \in Clos_{A'}(s', \Sigma')$  such that  $\Sigma' = ((\Sigma_{A'}^{\text{aut}} \setminus \Sigma_{A'}^{\text{Or}}) \setminus \Sigma_A, a \in \Sigma_{A'}(v')$ , and  $t \gtrsim' t'$  for  $t' = Succ_{A'}(v', a)$ . We have to prove that there is a state  $v'' \in Clos_{A''}(s'', \Sigma)$  such that  $\Sigma = ((\Sigma_{A''}^{\text{aut}} \setminus \Sigma_{A''}^{\text{Or}}) \setminus \Sigma_A, a \in \Sigma_{A''}(v''), and <math>t \gtrsim' t' \gtrsim'' t''$  for  $t'' = Succ_{A''}(v'', a)$ ? We consider  $Clos_{A'}^k(s', \Sigma') \subseteq Clos_{A'}(s', \Sigma')$  where k is the first

natural such that  $v' \in Clos_{A'}^k(s', \Sigma')$ . We define the states  $s'_i \in Clos_{A'}^k(s', \Sigma')$  inductively on  $0 \le i \le k$ :  $s'_0 = s'$  and  $s'_i \in Clos^i_{A'}(s', \Sigma') \setminus Clos^{i-1}_{A'}(s', \Sigma')$  for i > 0. For all  $b_i \in \Sigma_{A'}(s'_i) \cap \Sigma'$  and  $s'_{i+1} = Succ_{A'}(s'_i, b_i)$ , we define equally  $s''_i$  and  $\Upsilon''_i$  inductively on i:

- (3.1) i = 0:  $s_0'' = s'' (s_0' \ge s'' s_0'')$ ;  $\Upsilon_0'' = \{s_0''\}$ ;

- (3.2) i > 0: for all  $b_{i-1} \in \Sigma_{A'}(s'_{i-1}) \cap \Sigma'$  and  $s'_i = Succ_{A'}(s'_{i-1}, b_{i-1})$ , we have three cases:

- (3.2.1) if  $b_{i-1} \in \Sigma^{\text{Om}}_{A'}(s'_{i-1}) \cup \Sigma^{\text{Ir}}_{A'}(s'_{i-1})$ , then the definition goes as in (2.3.1); (3.2.2) if  $b_{i-1} \in \Sigma^{\text{Hm}}_{A'}(s'_{i-1})$ , then the definition goes as in (2.3.2);

- (3.2.3) if  $b_{i-1} \in \Sigma_{A'}^{\operatorname{Hr}}(s'_{i-1})$ , then the definition goes as in (2.3.3).