# Etude de la robustesse de transistors MOSFET SiC pour des applications aéronautiques

Dhouha Othman

### ▶ To cite this version:

Dhouha Othman. Etude de la robustesse de transistors MOSFET SiC pour des applications aéronautiques. Journées JCGE'2014 - SEEDS, Jun 2014, Saint-Louis, France. hal-01083936

HAL Id: hal-01083936

https://hal.science/hal-01083936

Submitted on 18 Nov 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Etude de la robustesse de transistors MOSFET SiC pour des applications aéronautiques

#### Dhouha OTHMAN

THALES Avionics Electrical Systems, 41, Boulevard de la République, 78400 Chatou, France SATIE, CNAM, CNRS, ENS Cachan, 61 Av. du Président Wilson, 94234 Cachan, France LTN IFSTTAR, 25 allée des Marronniers – Satory, 78000 Versailles, France othman.dhouha@satie.ens-cachan.fr

RESUME – L'objectif de cette étude est de maîtriser les aspects de robustesse des interrupteurs de puissance à technologie grand gap à base de carbure de silicium ainsi que l'étude de leur impact sur la conception des convertisseurs aéronautiques de nouvelle génération. Les travaux présentés portent sur des résultats expérimentaux préliminaires obtenus sur des transistors MOSFET 1200V en SiC. Cet article présente les résultats obtenus lors des essais de robustesse en régime de court-circuit et des essais de vieillissement accélérés montrant des modes de défaillance possibles dans des conditions réelles de fonctionnement.

MOTS-CLES – « Carbure de Silicium (SiC) », « MOSFET », « Caractérisation », « Vieillissement », « Robustesse », « court-circuit ».

#### 1. Introduction

Les études de marché des semi-conducteurs prédisent une expansion croissante dans le temps des composants à base de carbure de silicium. Les potentialités des semi-conducteurs SiC de puissance promettent des performances à la pointe de l'industrie et laissent présager des possibilités plus étendues que les composants en silicium : haut rendement, tenue en tension et fréquences de commutation élevées [5] [6], fonctionnement à haute température [1] et excellente robustesse en régime accidentel de fonctionnement [2] [3]. Aujourd'hui, les principaux fabricants et intégrateurs de composants et modules de puissance introduisent sur le marché des semi-conducteurs les premiers interrupteurs de puissance complets en carbure de silicium.

Dans le cadre de ses recherches, THALES mène des investigations sur ces nouvelles technologies de semi-conducteurs afin d'améliorer ses produits actuels et de développer des convertisseurs aéronautiques de nouvelle génération pour ses besoins futurs. En effet, les potentialités de ces interrupteurs de puissance sont remarquables et ouvrent de réelles possibilités de réduction globale masse/volume des convertisseurs.

Ces travaux sont réalisés dans le cadre d'une collaboration avec les laboratoires SATIE et LTN d'IFSTTAR. Ils ont pour objectif d'étudier les performances de cette technologie de composants à semi-conducteurs disponibles sur le marché, notamment les transistors MOSFET 1200V en SiC provenant de deux fabricants différents, ainsi que les contraintes spécifiques induites lors de leur intégration dans des convertisseurs aéronautiques.

Cet article présente une évaluation de la robustesse des transistors MOSFET en SiC soumis à des régimes extrêmes de fonctionnement, notamment des régimes de courts-circuits, mais également une évaluation de leur tenue au vieillissement accéléré. Un suivi régulier de différents indicateurs de vieillissement permettra d'analyser les modes de dégradation susceptibles d'apparaître ainsi que les mécanismes de défaillances. Les résultats expérimentaux présentés dans cet article concernent des transistors MOSFET d'un seul fabricant.

#### 2. Robustesse

#### 2.1 Estimation de l'énergie critique avant défaillance

Des tests de robustesse en régime de court-circuit sont réalisés à une température ambiante, T=25°C, afin d'évaluer l'énergie critique,  $E_C$  amenant à la défaillance. Cette dernière est définie comme étant l'énergie à partir de laquelle le composant est détruit lors du premier court-circuit. Pour une énergie dissipée supérieure à l'énergie critique, le composant est détruit immédiatement. En dessous de l'énergie critique le composant est à même de supporter la répétition de plusieurs régimes de court-circuit répétitifs [7].

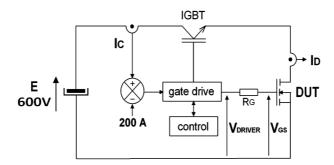

Le banc de test utilisé pour les essais de courts-circuits est présenté à la figure 1. Le dispositif sous test (DUT) est maintenu à l'état passant durant de la phase de court-circuit. Il est commandé en tension à travers une résistance de

grille externe, égale à 47 Ω. Le circuit de commande générique développé permet de régler indépendamment les niveaux de tension du driver, en les adaptant aux différentes technologies des transistors (MOSFET, JFET...). Un disjoncteur statique (IGBT 3,3 kV) est connecté en série avec le composant à tester en tant que dispositif de protection. Lorsque le courant de défaut dépasse un certain niveau de courant (arbitrairement fixée à 200 A ici), l'IGBT s'ouvre afin d'éviter l'explosion du dispositif sous test et sa dégradation complète.

Figure 1 : Schéma de principe du banc de test

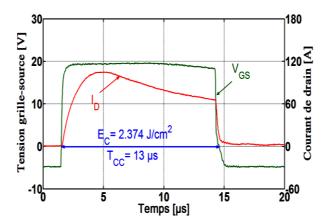

L'estimation de l'énergie critique est effectuée en appliquant des courts-circuits successifs et en augmentant progressivement la durée des courts-circuits à chaque fois d'une microseconde. Comme indiqué à la figure 2, jusqu'à une durée de court-circuit  $T_{CC}$ =13 µs, le MOSFET SiC 1200V assure l'ouverture du courant de court-circuit sans défaillance, ce qui correspond à une densité d'énergie dissipée égale à  $E_C$  =2,4 J/cm<sup>2</sup>.

Figure 2 : Essai de court-circuit avant la défaillance,  $V_{DS}\!=\!600V,\,T_{CC}\!=\!13~\mu s,\,T\!=\!25^{\circ}C$

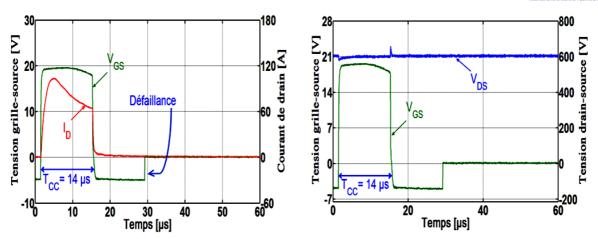

La défaillance apparaît pour une durée de court-circuit  $T_{CC}$  =14 µs. La figure 3 présente les formes d'ondes du courant  $(I_D)$  et des tensions  $(V_{DS}$  et  $V_{GS})$  à la défaillance. Dans un premier temps, le transistor assure l'ouverture du courant de court-circuit qui s'annule comme il est indiqué à la figure 3. Cependant, quelques microsecondes après la phase de court-circuit, un court-circuit inattendu apparaît entre la grille et la source. Ainsi, la défaillance de la grille, qui apparaît sous forme d'un court-circuit physique entre grille et source, se traduit ici par l'ouverture du transistor. Aucune défaillance n'est ainsi observée entre le drain et la source.

Figure 3 : Essai de court-circuit lors de la défaillance,  $V_{DS}$ =600V,  $T_{CC}$ =14  $\mu$ s,  $T_{amb}$  =25 $^{\circ}$ C

La défaillance du composant peut être due à la dégradation de la grille. En effet, selon [4] et [8], quand l'oxyde de la grille est détruit, le transistor devient incontrôlable. D'autre part, le délai entre la fin du court-circuit et l'apparition du défaut peut être dû à la diffusion de la température à l'intérieur du composant qui retarde l'échauffement de l'oxyde de grille et sa défaillance [11].

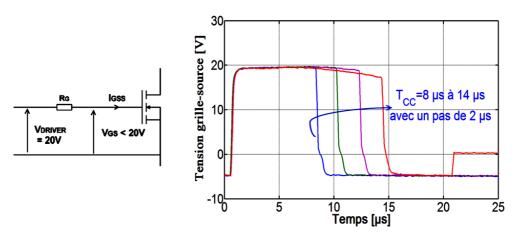

En outre, l'évolution de la tension de grille,  $V_{GS}$ , a été suivie durant ces essais, à chaque augmentation de la durée de court-circuit. Les résultats montrent qu'à partir d'une durée de court-circuit égale à  $T_{CC} = 10$  µs et lorsque le transistor est maintenu à l'état passant, la tension grille-source commence à diminuer comme il est indiqué à la figure 4. Cette chute de tension est probablement due à l'apparition d'un courant de fuite dans l'oxyde de grille et qui semble être responsable de la défaillance du composant. Un tel comportement n'a jamais été observé sur des composants silicium, il montre une éventuelle fragilité des oxydes de grille des transistors SiC et doit être analysé en détail afin d'évaluer précisément la robustesse des composants SiC et de mieux connaître leurs mécanismes de défaillance.

Figure 4 : Evolution de la tension  $V_{GS}$  durant les essais de courts-circuits successifs, mise en évidence d'un courant de fuite de grille pour les essais de C-C de longue durée

## 2.2 Vieillissement en régime de court-circuit

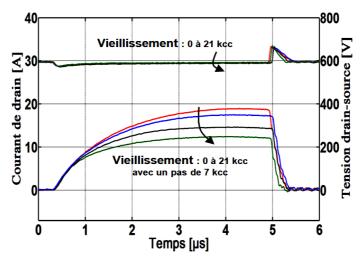

Des essais répétitifs en régime de court-circuit ont été réalisés afin d'étudier l'effet de ces modes de fonctionnement sur la robustesse des transistors. Un suivi régulier de l'évolution de différents paramètres électriques a été réalisé afin d'analyser l'effet de ces tests de vieillissement sur certains de ces paramètres représentatifs a priori de l'intégrité de la puce tels que : la résistance à l'état passant  $R_{DSON}$ , le courant de fuite de grille  $I_{GSS}$ , le courant de fuite de drain  $I_{DSS}$ , la tension de seuil  $V_{TH}$ , la tension de grille  $V_{GS}$  durant les essais, et le courant de court-circuit  $I_D$ .

Ces tests ont été effectués avec les conditions expérimentales suivantes: E = 600 V,  $R_G = 47\Omega$ ,  $T_{amb} = 25 ^{\circ} \text{ C}$ , et une courte durée de circuit  $T_{CC} = 5 \text{ } \mu \text{s}$  ( $T_{CC} < T_{critique}$ ) correspondant à une énergie dissipée nettement inférieur à l'énergie critique :  $E_{Dissipée} = 0.79 \text{ J/cm}^2 \le E_C = 2.374 \text{ J/cm}^2$ . Un cycle répétitif de 3 s a été choisi afin d'éviter tout échauffement moyen de la puce [13].

Les essais de courts-circuits répétitifs ont été menés jusqu'à 25000 courts-circuits et des caractérisations électriques régulières ont été effectuées tous les 2000 cycles. Ces tests ont été arrétés avant la défaillance du composant mais après une dégradation significative de differents indicateurs de vieillissement.

Dans des travaux antérieurs [9], une diminution de la tension  $V_{GS}$  pendant le régime de court-circuit a été observée pendant des essais destructifs. Cette chute de tension était probablement due à l'apparition d'un courant de fuite de grille pendant la phase de court-circuit et qui semble être responsable de la défaillance du composant [9]. Dans ce contexte, l'évolution du courant de fuite de grille et du courant de fuite de drain a été suivie afin d'étudier la dégradation de la grille au cours des essais de vieillissement.

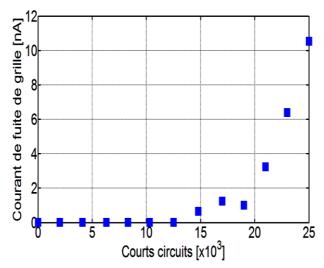

Les données enregistrées durant les premiers 10000 essais de vieillissement n'ont révélé aucune évolution de ces deux courants de fuite. Il a fallu attendre environ 15000 courts-circuits pour noter une augmentation significative de ces deux paramètres. La figure 5 présente l'évolution du courant de fuite de grille  $I_{GSS}$  durant le vieillissement en régime de court-circuit répétitif. Les résultats montrent une augmentation significative de ce courant, d'environ 10 nA, après 15000 courts-circuits. Ces résultats montrent clairement une dégradation de l'oxyde de grille.

Figure 5 : Courant de fuite de grille  $I_{GSS}$ ,  $V_{DS}$ =0V,  $V_{GS}$ =15V,  $T_{amb}$  =25°C

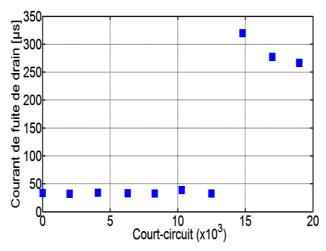

Des résultats similaires sont observés pour le courant de fuite de drain,  $I_{DSS}$ , comme le montre la figure 6. Le courant de fuite de drain a augmenté brutalement d'environ 250  $\mu$ A après 15000 courts-circuits et a dépassé 300  $\mu$ A au-delà de 21000 courts-circuits ce qui n'est pas visible sur la figure 6.

Figure 6 : Courant de fuite de drain  $I_{DSS}$ ,  $V_{DS}$ =1200V,  $V_{GS}$ =0V,  $T_{amb}$ =25°C

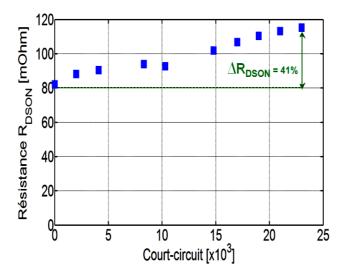

En outre, la résistance à l'état passant a aussi été suivie régulièrement durant le vieillissement du transistor MOSFET. La figure 7 présente l'évolution de  $R_{DSON}$  durant les essais répétitifs. Cette résistance a augmenté d'environ 41% après

21000 courts-circuits ce qui traduit une dégradation significative, soit au niveau des fils de bonding, soit au niveau de la métallisation de source, ce qui devra être analysé dans le détail par la suite. Des résultats similaires ont été observés sur des composants en silicium où l'augmentation de la résistance à l'état passant était également accompagnée d'une dégradation importante de la métallisation due à la reconstitution d'aluminium au cours du vieillissement [10] [13]. Néanmoins, cette évolution a besoin de plus d'investigations afin de corréler cette forte croissance de la résistance à l'état passant à la reconstruction de l'aluminium ou à un autre mécanisme de défaillance.

Figure 7: Résistance à l'état passant R<sub>DSON</sub>, V<sub>DS</sub>=1V, V<sub>GS</sub>=3V, T<sub>amb</sub>=25°C

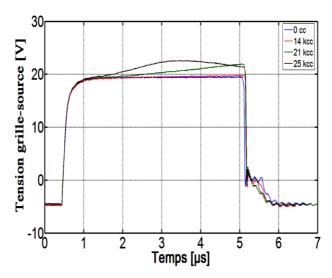

D'autres caractérisations ont été réalisées afin d'étudier le comportement de la grille, notamment l'évolution de la tension grille source  $V_{GS}$ , durant les essais de vieillissement. La figure 8 présente l'évolution de la tension  $V_{GS}$  appliquée entre grille et source durant les phases de vieillissement. Une augmentation de la tension  $V_{GS}$  est observée durant les essais de courts-circuits répétitifs et qui devient importante au-delà de 15000 courts-circuits. Cette évolution traduit bien une dégradation au niveau de l'oxyde de grille, mais cette fois elle concerne plus particulièrement une dégradation entre drain et grille. Cette dégradation coïncide avec l'apparition de forts courants de fuite entre drain et grille qui se traduit via la résistance du circuit de commande de grille par une augmentation de Vgs.

Ces résultats montrent en effet que l'augmentation de la tension  $V_{GS}$  est peut être due cette fois à l'apparition d'un courant de fuite entre le drain et la grille. Cette hypothèse nécessitera des investigations plus poussées telles qu'une caractérisation du courant de fuite entre le drain et la grille  $I_{GD}$  notamment à haute température.

Figure 8 : Tension grille-source  $V_{GS}$ ,  $V_{DS}$ =600V,  $R_G$ =47 $\Omega$ ,  $T_{amb}$ =25 $^{\circ}$ C

De plus, une diminution significative de courant de court-circuit a été observée pendant les essais de vieillissement de courts-circuits répétitifs.

Le courant de drain a en effet diminué d'environ 6 A après 21000 courts-circuits comme cela est observé à la figure 9. Ce comportement peut être corrélé avec l'augmentation de la résistance à l'état passant durant les tests répétitifs et qui se traduit par une diminution localisée de la tension entre grille et source réduisant de même le courant de court-circuit comme cela a déjà été montré sur des transistors JFET [14].

Figure 9 : Courant de drain  $I_D$ ,  $V_{DS}$ =600V,  $R_G$ =47 $\Omega$ ,  $T_{amb}$ =25 $^{\circ}$ C

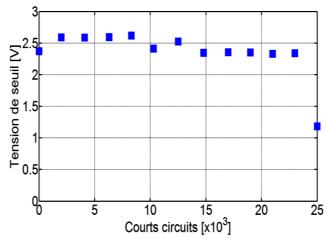

En ce qui concerne la tension de seuil,  $V_{TH}$ , aucune variation significative n'a été enregistrée au cours des premiers cycles des essais de vieillissement du transistor MOSFET SiC. Seule une légère diminution est observée au-delà de 15000 courts-circuits (d'environ 0,27 V) comme le montre la figure 10 et qui s'accompagne d'une diminution très importante de la tension de seuil juste avant de la défaillance.

Figure 10 : Evolution de la tension de seuil  $V_{TH}$  en cours de vieillissement,  $V_{DS}$ =600V,  $T_{amb}$ =25°C

#### 3. Conclusion

Cette étude traite de la robustesse des transistors MOSFET en technologie carbure de silicium. Des essais spécifiques ont été effectués en mode de court-circuit afin d'étudier d'une part les limitations de ces composants et d'autre par les modes de défaillance représentatifs ici des fragilités de ces composants.

La première partie de cet article a porté sur l'estimation de l'énergie critique,  $E_C$ , énergie à partir de laquelle le composant est détruit lors du premier court-circuit. Le transistor MOSFET SiC testé ici a été en mesure de supporter des essais de court-circuit sans défaillance jusqu'à une durée de court-circuit égale à 13 $\mu$ s et sous une tension drain-source de 600 V.

En outre, pendant les essais de court-circuit, le MOSFET SiC a montré une faiblesse au niveau de sa grille. En effet, le composant devient inopérant suite à une défaillance au niveau de la grille, sous la forme d'un court-circuit entre la grille

et la source. Cette défaillance se produit à l'état ouvert du transistor sous test, quelques microsecondes après la phase de court-circuit et maintient le transistor dans un état ouvert après sa défaillance entre grille et source.

La deuxième partie de ce document a présenté les principaux résultats expérimentaux obtenus pendant des essais de vieillissement du transistor MOSFET SiC soumis à des régimes de courts-circuits répétitifs. Durant ces tests, certains paramètres électriques ont été suivis afin de constituer des indicateurs de dégradations et d'identifier par la suite les mécanismes de défaillance. En effet, des caractérisations électriques régulières ont été réalisées afin de suivre l'évolution des courants de fuites de grille et drain, la résistance à l'état passant, la tension de grille, et le courant de court-circuit. Les principaux résultats ont montré une évolution de la résistance à l'état passant avec une augmentation de l'ordre de 41%, et des courants de fuites de grille et de drain ( $I_{GSS}$  et  $I_{DSS}$ ) avec une croissance significative au-delà de 15000 courts-circuits, indiquant la défaillance ou tout du moins une dégradation sévère de la grille.

Cependant, aucune évolution significative n'a été observée sur la tension de seuil durant les essais de vieillissement, seule une diminution significative de la tension de seuil a été mise en évidence juste avant la défaillance.

D'autres investigations doivent être menées afin d'étudier les mécanismes de défaillance des transistors MOSFET SiC suite à des tests de fatigue accélérée notamment à des tests de courts-circuits répétitifs. D'autres analyses fines telles que des observations au MEB et au FIB seront effectuées et qui permettront d'observer des zones susceptibles d'être à l'origine de la défaillance du transistor MOSFET SiC notamment le court-circuit entre grille et source.

#### 4. Références

- [1] Willander M, Friesel M, Wahab Q, Straumal B. Silicon carbide and diamond for high temperature device applications. J Mater Sci: Mater Electron 2006; 17:1–25.

- [2] Castellazzi A, Funaki T, Kimoto T, Hikihara T. Thermal instability effects in SiC power MOSFETs. Microelectron Reliab 2012; 52:2414–9.

- [3] Sheng H, Chen Z, Wang F, Millner A. Investigation of 1.2 kV SiC MOSFET for high frequency high power applications. In: IEEE vehicule power and propulsion conference (VPPC), September 2010.

- [4] Abbate C, Busatto G, Lannuzzo F. Unclamped repetitive stress on 1200 V normally-off SiC JFETs. Microelectron Reliab 2012; 52:2420–5.

- [5] Wang J, Zhao T, Li J, Huang AQ, Callanan R, Husna F, et al. Characterization, modeling, and application of 10-kV SiC MOSFET. IEEE Trans Electron Dev 2008; 55(8).

- [6] Knop A, Franke WT, Fuchs FW. Switching and conducting performance of SiCJFET and ESBT against MOSFET and IGBT. IEEE Trans Power Electron 2008:69–75.

- [7] F. Saint-Eve, «Influence des régimes extrêmes de fonctionnement sur la durée de vie des composants semi-conducteurs de puissance», Thèse de doctorat, ENS Cachan, 195 pages, 2004.

- [8] Abbate C, Busatto G, Lannuzzo F. Operation of SiC normally-off JFET at the edges of its safe operating area. Microelectron Reliab 2011; 51:1767–72.

- [9] Othman D, Berkani M, Lefebvre S, Ibrahim A, Khatir Z, Bouzourene A. Comparison study on performances and robustness between SiC MOSFET & JFET devices abilities for aeronautics application. Microelectron Reliab 2012;52:1859–64.

- [10] Martineau D, Mazeaud T, Legros M, Dupuy Ph, Levade C. Characterization of alterations on power MOSFET devices under extreme electro-thermal fatigue. Microelectron Reliab 2010; 50:1768–72.

- [11] Pietranico S, Pommier S, Lefebvre S, Khatir Z, Cadel E. Study of ageing of the metallization layer of power semiconductor devices. In: Proc power convers intell motion; 2010.

- [12] Arab M, Lefebvre S, Khatir Z, Bontemps S. Ageing of IGBT transistors under repetitive short-circuits operations. In: Proc power electron spec conf; 2008.

- [13] Detzel Th, Glavanovics M, Weber K. Analysis of wire bond and metallization degradation mechanisms in DMOS power transistors stressed under thermal overload conditions. Microelectron Reliab 2004; 44:1485–90.

- [14] Berkani M, Lefebvre S, Khatir Z. Saturation current and on-resistance correlation during repetitive short-circuit conditions on SiC JFET transistors. IEEE Trans Power Electron 2013;28(2):621–4.