## DEVELOPPEMENT D'UN CAPTEUR SUR PUCE AFIN D'ETUDIER LE COUPLAGE PARASITE DANS LES CIRCUITS INTEGRES DE TYPE " SMART POWER "

Marc Veljko Thomas Tomasevic, Alexandre Boyer, Sonia Ben Dhia

#### ▶ To cite this version:

Marc Veljko Thomas Tomasevic, Alexandre Boyer, Sonia Ben Dhia. DEVELOPPEMENT D'UN CAPTEUR SUR PUCE AFIN D'ETUDIER LE COUPLAGE PARASITE DANS LES CIRCUITS INTEGRES DE TYPE "SMART POWER". 17ème Colloque International et Exposition sur la Compatibilité ÉlectroMagnétique (CEM 2014), Jul 2014, Clermont-Ferrand, France. pp.1-5. hal-01068133v2

### HAL Id: hal-01068133 https://hal.science/hal-01068133v2

Submitted on 3 Mar 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### DEVELOPPEMENT D'UN CAPTEUR SUR PUCE AFIN D'ETUDIER LE COUPLAGE PARASITE DANS LES CIRCUITS INTEGRES DE TYPE « SMART POWER »

V. Tomasevic<sup>1</sup>, A. Boyer<sup>2</sup>, S. Ben Dhia<sup>3</sup>

$\frac{1}{vtomasev@laas.fr}; \frac{2}{aboyer@laas.fr}; \frac{3}{sbendhia@laas.fr}; \\ LAAS-CNRS$

Université de Toulouse ; UPS, INSA, INP, ISAE ; UT1, UTM, LAAS Toulouse, France

Résumé. De nos jours, dans le but d'intégrer sur une même puce les parties de puissance et les parties analogiques et numériques à basse tension, on a de plus en plus recours à de circuits de type SMART POWER. La commutation des transistors MOS de puissance, présents dans ce type de circuits, génère du bruit dans le substrat pouvant affecter les parties basse tension par couplage. Ceci est dû principalement à la génération des courants parasites dans le substrat dont les conséquences peuvent être néfastes au bon fonctionnement du circuit intégré. Cet article présente le développement d'un capteur sur puce permettant de caractériser l'impact du couplage substrat sur différents blocs d'un circuit SMART POWER.

#### INTRODUCTION

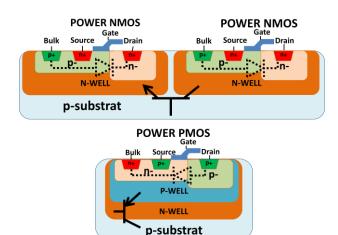

Les circuits SMART POWER, présents de plus en plus sur le marché des circuits intégrés, sont très utilisés dans de nombreuses applications électroniques embarquées (automobile, télécommunications...). Leur principal avantage est d'intégrer sur un seul circuit des composants haute tension, tels que des transistors MOS de puissance, avec des composants utilisés dans les parties analogiques et numériques basse tension [1]. La cohabitation entre étages de puissance et parties analogiques pose des problèmes de fiabilité dus au couplage substrat entre ces différents blocs fonctionnels. Aujourd'hui, lors du développement des circuits SMART POWER, les outils de conception (CAD) ne prennent pas en compte le couplage substrat activant les structures bipolaires parasites, tels que les transistors NPN et PNP, illustrés sur la figure 1.

En effet, la commutation des MOS de puissance, génère dans le substrat des courants de porteurs majoritaires et minoritaires, qui, à leur tour activent ces structures parasites bipolaires. Ces effets parasites peuvent être très néfastes pour le circuit (perturbations des parties basse tension : bruit pour l'analogique et disfonctionnement pour le numérique), voire destructeurs (phénomène de latchup) [5],[2],[3].

Cette étude a été mené grâce aux fonds du 7ème cadre Européen, un programme crée par l'Union Européene (Projet AUTOMICS, grant agreement no. 314135).

Fig. 1 : Structures bipolaires parasites autour des circuits SMART POWER (NMOS et PMOS de puissance)

Dans le cadre du projet AUTOMICS [4], va être développé et validé un modèle de substrat tenant compte des structures bipolaires parasites pouvant être utilisé dans les outils de conception CAD afin de prédire les effets d'un couplage substrat. Pour ce projet a été développé un capteur sur puce, directement intégré sur un circuit SMART POWER dans le but de détecter les fluctuations temporelles rapides des tensions de substrat et ainsi confirmer l'activation des structures parasites bipolaires.

Dans cet article nous traiterons du développement du capteur sur puce. Les mesures sur puce exposées serviront à valider indirectement la présence du courant substrat parasite.

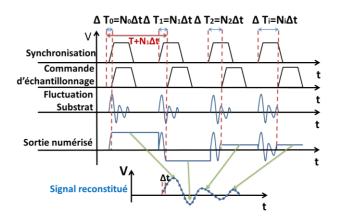

#### PRESENTATION GENERALE DU CAPTEUR

Le système de mesure proposé est échantillonneur bloqueur totalement intégré sur silicium. Pour extraire la forme temporelle des signaux mesurés le capteur fonctionne selon un mode de sous échantillonnage, décrit dans la figure 2. Le signal à mesurer doit être réitérable et synchronisé avec la commande d'échantillonnage du capteur. Cette commande externe, avec une période T, déclenche l'apparition de l'évènement que l'on cherche à mesurer.

Fig. 2: Le principe d'acquisition du signal et de reconstitution de sa forme temporelle par le capteur

Elle active aussi la cellule d'échantillonnage mais avec un certain délai  $\Delta T_i$  finement contrôlé. Ici  $\Delta T_i$  représente la résolution du délai, c'est-à-dire le pas « virtuel » d'échantillonnage que l'on peut obtenir et qui dépend directement de la précision du délai. La forme temporelle est reconstituée à partir des différents échantillons et en calculant leur instant d'apparition à partir de la commande d'échantillonnage. L'avantage de cette technique est la possibilité de numériser les signaux avec une large bande passante sans recourir à des circuits électroniques haute fréquence [6], [7].

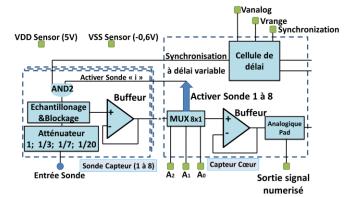

Le schéma-bloc du capteur est présenté à la figure 3. Il possède un bloc (cœur) analogique/numérique contrôlant 8 sondes pouvant être disposés sur la puce au plus près du point de mesure et mesurer des tensions allant de -0.6V à 50V. Ce bloc possède un multiple xeur analogique 8x1, un buffer de sortie ainsi qu'un système de génération de délai par rapport à la commande d'échantillonnage (Synchronisation).

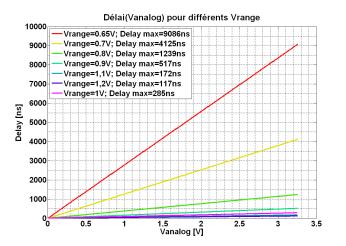

Le délai variable est contrôlé par deux signaux :  $V_{range}$  et  $V_{analog}$ . La Fig. 4 présente un résultat de mesures de l'évolution du délai en fonction de ces 2 signaux. Ces caractéristiques sont indispensables pour reconstituer la forme temporelle du signal mesuré. La fenêtre de mesure la plus large atteint 1.7  $\mu$ s. Le délai évolue de manière quasi linéaire avec  $V_{analog}$ .

Chacune des 8 sondes possède une cellule d'échantillonnage-blocage optimisée pour limiter l'offset de mesure, un buffer de sortie local et un atténuateur (1/20, 1/3, 1/5) selon la tension maximale du signal à échantillonner.

Pour la réalisation du capteur sur puce une des principales contraintes étaient les limitations de la surface occupée, les exigences sur la bande passante et la réduction de la capacité d'entrée du capteur. Une fois le layout du capteur réalisé, la superficie du noyau principal est de 396 µm x 77 µm et d'environs 50 µm x 120 µm pour les différentes sondes, selon la taille d'atténuateur utilisé. La bande passante de chaque sonde est de 1.7 GHz et leur capacité d'entrée est de 24,14 fF.

Fig. 3: Structure du capteur sur puce

Fig. 4 : Evolution du délai en fonction de signaux  $V_{analog}$  et  $V_{range}$  (mesuré)

#### ANALYSE EXPERIMENTALE ET MESURES

Un circuit intégré de test a été fabriqué en technologie CMOS AMS H35 50V à 4 niveaux de métaux. Celle-ci offre la possibilité d'isoler les structures basse et haute tension avec des caissons NWELL enterrés [8]. Le capteur sur puce a été entièrement conçu avec des transistors isolés MOS 5V. Deux expériences ont été prévues afin d'étudier le couplage parasite entre une structure « bruyante » et une structure sensible.

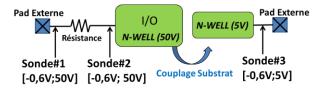

# I.1. Expérience 1: Couplage entre structures basiques par injection/collection des porteurs minoritaires et majoritaires dans le substrat

Le principe de l'expérience 1 est présenté sur la figure 5. La structure d'injection est constituée par un buffer de sortie dont on peut modifier le potentiel de sortie. Deux capteurs sont placés aux bornes d'une résistance série mise en sortie du buffer, pour mesurer le courant injecté dans le substrat lors d'une forte augmentation ou diminution du potentiel de sortie. Un troisième capteur mesure les fluctuations de potentiel d'un caisson Nwell distant qui collecte les porteurs injectés dans le substrat par le buffer.

Fig. 5: Couplage entre structures basques (NWELL)

Les variations du potentiel de sortie du buffer peuvent être provoquées par sa commutation lorsqu'elle est chargée par une charge inductive, ou lors d'injections de perturbations électromagnétiques ou d'impulsions ESD.

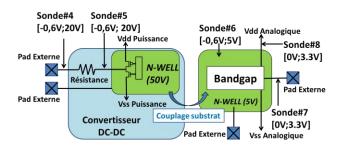

## I.2. Expérience 2: Couplage entre les parties de puissance et parties analogiques basse tension

Le but de cette expérience, décrit dans la figure 6, est d'observer les perturbations induites par la commutation d'un convertisseur DC/DC sur une structure analogique faible tension (référence de tension Bandgap). Les mesures de fluctuations rapides de tension sur l'alimentation du Bandgap (sonde #8), son NWELL enterré (sonde #6) et sa sortie (sonde #7) seront effectuées et comparés au courant injecté dans le substrat lors des commutations du convertisseur DC/DC (sondes #4 et #5 placées aux bornes d'une résistance en sortie du convertisseur).

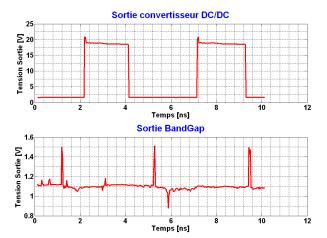

Sur la figure 7 sont présentés les résultats préliminaires de mesures de tensions en sortie du convertisseur DC/DC (non chargé) et de la sortie du Bandgap. La calibration en tension de tous les capteurs étant en cours, les mesures valides seront présentées dans la publication finale. Une analyse sera faite afin d'observer l'influence sur la sortie en tension du Bandgap en fonction de la variation de l'amplitude en sortie du convertisseur DC/DC. Le convertisseur DC/DC sera chargé avec une impédance inductive dont les rapides changements de tension sur ses bornes provoqueront en retour une injection de courant dans le substrat.

Fig. 6: Couplage entre les parties de puissance et parties analogiques basse tension

Fig. 7: Tension en sortie du convertisseur DC/DC et du Bandgap

#### **CONCLSION**

Cet article a présenté le développement d'un système de mesures sur puce permettant d'analyser l'impact du couplage substrat caractéristique aux circuits de type SMART POWER. Grâce à une évaluation plus précise de ces phénomènes parasites qu'offre ce capteur sur puce, on pourra analyser l'activation des structures parasites bipolaires sur de différents blocs de ce type de circuit.

D'un point de vue technique, le capteur sur puce avec sa large bande passante obtenue grâce à la méthode de sous-échantillonnage, permet de faire des mesures de tension non intrusives. Plus encore, la proximité du capteur du point mesuré permet de réduire le bruit supplémentaire provenant du couplage parasite de type capacitif ou inductif dû à l'interconnexion entre le capteur et du point mesuré.

La calibration du capteur et les mesures sont en cours d'élaboration (voir figure 4) et pour la publication finale elles seront incluses dans l'article.

Dans le futur, une analyse comparative sera effectuée entre les résultats obtenus ici et les résultats issus des simulations avec des nouveaux modèles SPICE de substrat développés au sein du projet AUTOMICS.

#### **REFERENCES**

- [1] H.Zitta, "Smart Power Integrated Circuits", UNSECO encyclopedia of life support system (EOLSS), Available from: http://www.eolss.net

- [2] F. Lo Conte, J.-M. Sallese, M. Pastre, F. Krummenacher and M. Kayal. "A circuit-level substrate current model for smart-power ICs, IEEE Transactions on Power Electronics", vol. 25, num. 9, p.2433-2439, 2010.

- [3] M. Schenkel, "Substrate Curent Effects in Smart Power ICs", Ph.D thesis, 2003, Technische Wissenschaften ETH Zürich, Nr. 14925, Available from: e-collection.library.ethz.ch, pp 1-24.

- [4] M. Schenkel, "Methodology for Characterizing Substrate Currents", Project Subsafe Deliverable 2.2.1 and IC&D Deliverable 6.2.1.4, 2001, Integrated Systems Laboratory, Swiss Federal Institute of Technology Zurich

- [5] AUTOMICS web site: <a href="https://www.automics.eu/">https://www.automics.eu/</a>

- [6] S. Ben Dhia, "Une nouvelle methodologie de caracterisation de l'integrite du signal en cmos submicronique profond." Ph.D thesis, 2003, Institut national des sciences appliquées de Toulouse.

- [7] S. Ben Dhia, A; Boyer, "On-Chip Noise Sensor for Integrated Circuit Susceptibility Investigations" IEEE transactions on instrumentation and measurement, vol. 61, no. 3, march 2012.

- [8] AMS web site: http://www.ams.com/eng/Products/Full-Service-Foundry/Process-Technology/High-Voltage/HV-Selection-Guide