# Conception de thyristors SiC permettant l'étude de l'amplification interne de l'allumage

Sigo Scharnholz, Luong Viêt Phung, Dominique Tournier, Bertrand Vergne, Ralf Hassdorf, Pierre Brosselard, Dominique Planson

# ▶ To cite this version:

Sigo Scharnholz, Luong Viêt Phung, Dominique Tournier, Bertrand Vergne, Ralf Hassdorf, et al.. Conception de thyristors SiC permettant l'étude de l'amplification interne de l'allumage. Symposium de Génie Electrique (SGE'14), Jul 2014, Cachan, France. hal-01065352

HAL Id: hal-01065352

https://hal.science/hal-01065352

Submitted on 18 Sep 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Conception de thyristors SiC permettant l'étude de l'amplification interne de l'allumage

Sigo SCHARNHOLZ <sup>a</sup>, Luong Viêt PHUNG <sup>b</sup>, Dominique TOURNIER <sup>b</sup>, Bertrand VERGNE <sup>a</sup>, Ralf HASSDORF <sup>a</sup>, Pierre BROSSELARD <sup>b</sup> et Dominique PLANSON <sup>b</sup>

a: ISL, Saint Louis, France; b: Laboratoire Ampère, INSA de Lyon, Villeurbanne, France

RESUME - Cetarticle présente la conception d'un thyristor SiC et les résultats de simulation par éléments finis. Ce travail vise àétudier expérimentalement le comportement dynamique d'un thyristor SiC avec gâchette amplificatrice. Ce type de thyristor n'a pas été étudié pour l'instant en détail pour le SiC. Pourtant, avec l'amélioration constante de la qualité des wafers de SiC et des diamètres de substrat accessibles, l'intégration d'un système de commande avec une amplification interne de l'allumage devient un concept essentiel pour les thyristors de puissance à base de SiC.

Mots-clés—Carbure de silicium, SiC, thyristor, GTO, LTT, AGT, gâchette amplificatrice.

#### 1. Introduction

L'électronique de puissance est une technologie clé permettant l'utilisation efficace des ressources électriques aussi bien pour les réseaux de distribution que pour les plateformes mobiles autonomes. Grâce à ses propriétés physiques exceptionnelles, le carbure de silicium (SiC) est le matériau semi-conducteur de choix pour la réalisation de diodes et thyristors qui seront intégrés dans les futures applications de fortes puissances comme les convertisseurs et les applications pulsées. La gâchette amplificatrice représente la meilleure structure de commande pour les composants silicium de grandes dimensions comme les thyristors à contrôle de phase PCT (phase control thyristor) et les thyristors à commande optiques LTT (light triggered thyristor) [1]. Avec l'amélioration constante de la qualité des wafers de SiC et des diamètres accessibles, l'intégration d'un système de commande avec une amplification interne de l'allumage devient un concept intéressant pour les thyristors à base de SiC.

L'objectif global des travaux décrits dans cette contribution est l'application du concept d'une gâchette amplificatrice dans un thyristor SiC. Le concept, bien connu dans la technologie silicium (PCT et LTT) est appliqué pour réduire la puissance nécessaire au déclenchement du thyristor. Une surface plus grande entre l'électrode de contrôle (gâchette) et l'anode (cathode dans le cas d'un thyristor silicium) permet d'augmenter la capacité en terme de variation de courant lors de la fermeture du thyristor. Pour ces thyristors de grande taille, l'intégration d'une gâchette amplificatrice est incontournable. Cela permettra de répondre aux futurs besoins civils (ferroviaire) et militaires (puissance pulsée). A cause de la taille des puces SiC actuellement accessibles, le concept d'une

gâchette amplificatrice n'a jamais été pour l'instant étudié en détail. Ce concept a été appliqué d'une manière simple uniquement dans le cas de thyristors à commande optique (LTT), qui commence à être développés enSiC depuis peu de temps [2, 3]. C'est pourquoi, nous avons lancé cette étude approfondie sur une ou plusieurs variantes du système de commande avec une amplification interne de l'allumage, telle que la gâchette amplificatrice [4].

### 2. CONCEPTION DU COMPOSANT

Cette étude vise à réaliser un grand nombre de thyristors SiC avec des paramètres géométriques et technologiques différents. Puisqu'il s'agit d'une étude fondamentale, les composants n'ont pas besoin d'avoir des performances élevées. En conséquence, il apparaît suffisant de réaliser des thyristors de 1,2 kV ayant une taille moyenne de 10 mm<sup>2</sup> au maximum. Cela permet d'économiser sur les coûts du matériau SiC (wafer) et de maximiser les chances d'obtenir des composants fonctionnels (densité de défauts). L'accent du travail est clairement mis sur le design de la structure anode-gâchette qui a été variée de manière appropriée pour pouvoir déduire les effets spécifiques mis en jeu dans le SiC. Ceci est fait à l'aide de simulations par éléments finis, qui servent non seulement à trouver un bon point de départ au niveau de l'architecture, mais aussi à analyser en détail les résultats issus de la caractérisation électrique. Cette dernière permettra d'optimiser et de valider les paramètres de simulation.

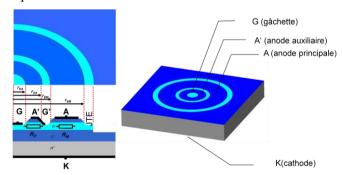

Fig.1 Structure du thyristor SiC conçu, contenant un thyristor dit pilote ou auxiliaire (G et A') et un thyristor principal (G' et A).

# 2.1. Structure du composant de base

Pour étudier le comportement d'une structure de gâchette amplificatrice, il parait concevable de réaliser une structure qui,

dans un premier temps, correspond à un modèle théorique simple. Notre thyristor SiCde base représente donc une structure annulaire avec la gâchette G ronde au milieu entourée d'une anode A' annulaire. Cette structure est représentée sur la la figure 1 de droite. Entre la gâchette G et l'anode A se situe l'anode A' du thyristor dit pilote ou auxiliaire et la gâchette amplificatrice G' qui contrôle le thyristor principal.

Sur la représentation en coupe de la figure 1 (à gauche) on peut bien percevoir que cette structure est caractérisée par quatre rayons,  $r_{\rm EA}$  ...  $r_{\rm SM}$ , limitant les zones d'émetteur p<sup>+</sup> en dessous de A' et A. Il est à noter, que pour un thyristor SiC la gâchette est toujours située du côté de l'anode et l'émetteur p<sup>+</sup> ainsi que les deux bases n et p<sup>-</sup> sont des couches épitaxiées, isolées par une gravure plasma. En utilisantdes coordonnées radiales, la résistance  $R_{\rm P/M}$  (index P pour pilote et M pour main/principal) de la couche de la base n en dessous des deux zones d'émetteurs mentionnées ci-dessus est donnéepar l'équation 1:

$$R_{P/M} = \int_{r_{Ei}}^{r_{Si}} \rho \cdot \frac{dr}{d \cdot 2\pi \cdot r} = \frac{\rho}{2\pi \cdot d} \ln \frac{r_{Si}}{r_{Ei}}$$

(1)

où d est l'épaisseur et  $\rho$  la résistivité de la couche de base n. Les indices « Ei » et « Si » (i = A pour thyristor auxiliaire/pilote et M pour main/principal) du rayon r sont données sur la figure 1.

Si ce thyristor avec gâchetteamplificatrice est bien dimensionné, le thyristor auxiliairese déclenche en premier et entraîne ensuite la commutation du thyristor principal. Pour notre structure annulaire simple cette règle se traduit par l'équation 2 [4]:

$$\frac{r_{SA}}{r_{EA}} > \frac{r_{SM}}{r_{EM}} \tag{2}$$

# 2.2. Dimensionnement du composant de base

En se basant sur les résultats de projets précédents [5], une structure de thyristor SiC (plaque avec couches épitaxiées) a été conçue et les paramètres, pour une première série de dimensionnements, ont été définis. Ceci a permis de mettre en valeur les paramètres géométriques importants liés à une structure de gâchette amplificatrice avec et sans émetteur court-circuité et de définir les premières variations géométriques à explorer.

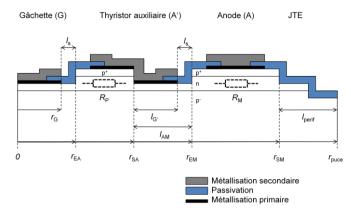

La structure principale est représentée avec ses dimensions caractéristiques sur la figure 2. Il s'agit de la même structure que sur la figure 1 (à gauche) mais avec des flancs de mesa idéalisé (verticaux), permettant de définir clairement les dimensions du masque de photolithographie. Le paramètre  $l_{\rm s}$  représente une distance de sécurité pour tenir compte de la tolérance de la technologie, notamment la résolution de la lithographie. Elle est fixée à  $10~\mu m$ .

Fig. 2Vue en coupe radiale de la structure supérieure du thyristor SiC conçu. $R_P$  et  $R_M$  indiquent les résistances de la couche de base n, important pour l'amorçage séquenciel du thyrsitor auxilaire (<u>P</u>ilote) et principal (<u>M</u>ain).

Le point de départ de nos réflexions sur ledimensionnement du thyristor est la taille du composant, c'est à dire de la puce, diamètre l'électrode de gâchette,<br/>définisrespectivement par les rayons $r_{\rm puce}$  et  $r_{\rm G}$ .<br/>En ce qui concerne la taille de la puce, une forme carrée de 3 mm× 3 mm ( $r_{puce} = 1500 \mu m$ ) nous parait un bon compromis entre un rendement suffisamment élevé pour disposer d'un grand nombrede composants fonctionnels par wafer et une taille minimale pour l'interaction d'une structure de gâchette amplificatrice.Le diamètreminimal de la gâchette est donné par le fait que cette électrode doit êtreconnectée par l'intermédiaire de fils de bonding. Ainsi, un diamètre de 300  $\mu$ m ( $r_G$  = 150 µm) nous paraît raisonnable pour pouvoir connecter quelques fils d'un diamètre de 50 µm.

Tableau 1. Détermination des rayons caractéristiques du thyristor auxiliaire  $(r_{\rm EA}, r_{\rm SA})$  et du thyristor principal  $(r_{\rm EM}, r_{\rm SM}).l_{\rm s}$  est la distance de sécurité, fixée à 50  $\mu$ m,  $l_{\rm perif}$ s'élève à 300  $\mu$ m et elle comporte la terminaison et la bordure de coupe.

| Rayon             | Détermination                       | Valeurs cas 1 ( $r_{EM}$<br>= $f(r_{SA})$ ) | Valeurs cas 2<br>(r <sub>EM</sub> = fixe, r <sub>SA</sub> et<br>l <sub>AM</sub> variable) |

|-------------------|-------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------|

| $r_{\mathrm{EA}}$ | $r_{\rm G}+l_{\rm s}$               | 160 μm                                      | 160                                                                                       |

| $r_{\mathrm{SA}}$ | variable                            | > 419 µm                                    | > 384 µm                                                                                  |

| $r_{ m EM}$       | $r_{\mathrm{SA}} + l_{\mathrm{AM}}$ | $r_{SA} + 40 \mu m$                         | 500 μm                                                                                    |

| $r_{ m SM}$       | $R_{ m puce} - l_{ m perif}$        | 1200 μm                                     | 1200 μm                                                                                   |

En fixant les dimensionsintérieures et extérieures du thyristor, deux des quatre paramètres de l'équation 2 sont donnés (voir tableau 1,  $r_{\rm EA}$  et  $r_{\rm SM}$ ). Il ne reste qu'à déterminerles deux rayons du milieu,  $r_{\rm SA}$  et  $r_{\rm EM}$ , qui sont directement relié par la distance  $l_{\rm AM}$ . La valeur minimale de cette distance est déterminé par la distance de sécurité plus une largeur minimale de contact  $l_{\rm G}$  de la gâchette amplificatrice. Pour ladernière une largeur trois fois supérieure de la distance de sécurité nous parait raisonnable. Le rayon  $r_{\rm SA}$ ne dépend que des paramètres connus(tableau 2, colonne 2) et l'équation 2 peut être transformée comme ce qui suit :

$$r_{SA} > -\frac{1}{2}l_{AM} + \sqrt{\frac{1}{4}l_{AM}^2 + r_{EA} \cdot r_{SM}}$$

(3)

où les valeurs des paramètres et le résultat de l'intégralité sont exposés dans la colonne 3 du tableau 1 (Valeurs cas 1).

La valeur  $r_{\rm SA}$ > 419 µm n'indique qu'un point de départ pour concevoir des thyristors tenant compte plus ou moins bien de la règle de l'équation 2. Pour des raisons de comparabilité de ces thyristors au niveau du calibre de courant, on a décidé que la taille de l'anode principale doit rester constante et donc le rayon  $r_{\rm EM}$ . Comme résumé dans la colonne 4 du tableau l (Valeurs cas 2), cela implique que la distance  $l_{\rm AM}$  varie enmême temps que $r_{\rm SA}$ . Une valeur  $r_{\rm EM}$  fixée à 500 µm permet donc de faire varier  $r_{\rm SA}$ d'une valeur bien inférieureà la valeur nécessaire pour déclencher le thyristor pilote en premier ( $r_{\rm SA}$ < 384 µm) jusqu'à une valeur de  $r_{\rm SA}$  =  $r_{\rm EM}$  –  $l_{\rm AM}$  = 460 µm, bien au-dessus du seuil pour respecter la règle de l'équation 2.

## 2.3. Processus technologique

Comme le montre la figure 1, la structure de base du empilement thvristor un  $n^+$ (substrat)/p/p $^-$ /n/p $^+$ . complémentaire à celui d'un thyristor classique en silicium. L'émetteur p (anode) aura une épaisseur de 1 µm et il serafortement dopé à 1.10<sup>19</sup> cm<sup>-3</sup>. Pour la base n (gâchette) une épaisseur de 2 µm est prévue avec une concentration de 1.10<sup>17</sup> cm<sup>-3</sup>. La base p (couche de drift) d'une épaisseur de 10 μm, dopée à 5.10<sup>15</sup> cm<sup>-3</sup> sera déposée sur une couche de buffer de 4 µm, dopéep avec une concentration de 5.10<sup>17</sup> cm<sup>-3</sup>. Il s'agit donc d'une structure asymétrique avant une tension de claquage idéale en direct bloqué de 1,9 kV, déterminée par des simulations à éléments finis unidimensionnelles (1D). Pour se rapprocher au maximum de cette valeur idéale, le composant est protégé par une terminaison JTE gravée.

#### 2.3.1. Etapes de fabrication

Le matériau de départ est un wafer SiC 4H de 100 mm de diamètre de la société SiCrystal AG. Ces wafers ont été commandés avec l'empilement des couches épitaxiées mentionnées ci-dessus. L'épitaxie a été réalisée par le soustraitant suédois Acreo AB.

Le processus de fabrication est basé sur un jeu de sept masques. Les deux premières étapes servent à graver la structure anode/gâchette et la terminaison avec un réacteur RIE (reactive ion etching). Pour la gravure de l'anode, un masque en résine sera utilisé dans le but de réaliser des parois inclinées, permettant de déposer une couche de métallisation secondaire sans ruptureau niveau de la marche entre A' et G'. Pour la gravure de la terminaison, un masque en résine seraégalement utilisé. Une étape optionnelle est prévue pour réaliser par implantation ionique des zonesfortement dopées n<sup>+</sup>au niveau des contacts de la gâchette.

Après une étape de nettoyage intensive, on procèdera à la métallisation primaire directement sur la structure de l'anode et de la gâchette. Pour la métallisation primaire, du nickel sera utilisé au niveau de la gâchette et un alliage Ti/Ni/Al au niveau de l'anode. Après une étape de recuit après chaque métallisation, une couche de passivation (SiO<sub>2</sub>) sera déposée et des ouvertures y seront gravées pour définir les zones de contacts de l'anode et de la gâchette.Enfin, un deuxième niveau de métallisation sera déposé pour former les plots d'anode et de gâchette ainsi que la bande métalliqueliant les

deux thyristors entre A' et G'. Il s'agit d'une couche d'aluminium d'une épaisseur de quelque micromètre.

#### 2.3.2. Influence des toléreances technologiques

Pour pouvoir estimerà quel niveau la règle de l'équation 2 est respectée tout en considérant les tolérances technologiques, les valeurs de la résistance  $R_{\rm P}$  et  $R_{\rm M}$  en dessous des anodes des deux thyristors sont calculées en utilisant l'équation 1. Le tableau 2 montre ces valeurs en fonction de l'écart de l'épaisseur d et de la résistivité  $\rho$  de la couche de base n ainsi que du rayon  $r_{\rm SE}$ .

Tableau 2. Calcul des résistances  $R_{PM}$ en dessous du thyristor auxiliaire(indice P) et du thyristor principal (indice M) en fonction de l'écart de l'épaisseur d et de la résistivité  $\rho$ de la couche de base n (tolérance des couches d'épitaxiées :  $\pm 10$  % et  $\pm 25$ % respectivement), ainsi que du rayon  $r_{\rm SE}$  (résolution de la lithographie :  $\pm 2 \mu$ m).

| ∆d     | Δρ        | ∆r<br>S/E | $R_{\rm P}$ | $R_{\mathrm{M}}$ |

|--------|-----------|-----------|-------------|------------------|

| 0      | 0         | 0         | 84.04 Ω     | 69.67 Ω          |

| 0      | 0         | + 2 μm    | 85.38 Ω     | 70.12 Ω          |

| 0      | +0.025Ωcm | + 2 µm    | 106.73 Ω    | 87.65 Ω          |

| -0.2µm | +0.025Ωcm | + 2 μm    | 118.60 Ω    | 97.39 Ω          |

| 0      | 0         | - 2 μm    | 82.70 Ω     | 69.22 Ω          |

| 0      | -0.025Ωcm | - 2 μm    | 62.03 Ω     | 51.91 Ω          |

| +0.2µm | -0.025Ωcm | - 2 μm    | 56.39 Ω     | 47.19 Ω          |

Pour les valeurs prévues (sans écart), notamment  $r_{\rm SA} = 460~\mu{\rm met}~r_{\rm EM} = 500~\mu{\rm m}$ , les résistances $R_{\rm P}$  et  $R_{\rm M}$  ont une différence de 14  $\Omega$ . Cette différence varie mais dans aucun cas  $R_{\rm P}$  s'approche d'une manière trop significative de la valeur de  $R_{\rm M}$ , ce qui pourrait mettre en cause l'allumage séquentiel souhaité des deux thyristors.

#### 3. RÉSULTATS DE SIMULATION

Pour étudier le fonctionnement du composant, des simulations 2D ont été effectuées en utilisant le logiciel Sentaurus<sup>TM</sup>. Dans un premier temps, des simulations statiques ont servi à définir le véhicule de test, un thyristor 1200V. Cela a permis de choisir les paramètres technologiques tels que les résistances de contact, le profil de gravure et la nature/épaisseur de la couche de passivation.

Puis, l'influence de différentes géométries de la structure gâchette-anode a été étudiée en simulation d'un point de vue dynamique. La structure 2D simulée est représentée sur la figure 2. Pour vérifier l'allumage séquentiel des deux thyristors, le rapport entre les résistances  $R_{\rm P}$  et  $R_{\rm M}$  a été varié de part et d'autre du critère de conception d'une gâchette amplificatrice. Cela a été réalisé en faisant varier les distances latérales de l'anode auxiliaire (A'). Lorsque la valeur de la résistance  $R_{\rm P}$  est inférieure à celle de  $R_{\rm M}$ , seul le thyristor principal devrait s'amorcer. A contrario, lorsque la valeur de la résistance  $R_{\rm M}$  est inférieure à celle de  $R_{\rm P}$ , le thyristor pilote s'amorcerait en premier suivi de l'amorçage du thyristor principal.

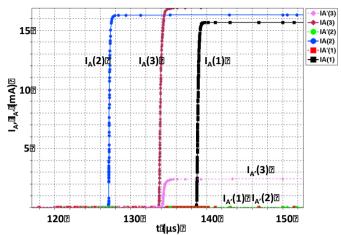

Trois configurations ont été retenues pour les simulations. La première configuration, notée (1) et dimensionnée telle que  $R_{\rm M}$  soit supérieure à  $R_{\rm P}$ , représente le cas pessimiste où seul le thyristor principal s'amorce.Les deux configurations

restantes(2 et 3) permettent l'amorçage dans le bon ordre des deux thyristors pilote et principal. Notons que la configuration (3) présente un ratio  $R_{\rm P}/R_{\rm M}$  nettement plus en faveur de  $R_{\rm P}$  que dans la configuration (2) en guise de marge de sécurité. Les simulations des comportements à l'amorçage de ces trois structures sont données par la figure 3. Les courants  $I_{\rm A}$  et  $I_{\rm A}$ -ont été calculés en prenant une profondeur de la structure 2D de 1  $\mu$ m. Elle sont respectivement les courants véhiculés par le thyristor principal et le thyristor pilote. Les conditions d'amorçage de ces trois structures sont les mêmes.

Fig.3Simulation de l'amorçage de la structure AGT pour trois configurations. (1) :  $R_M > R_P$ , (2) :  $R_M < R_P$ , (3) :  $R_M < R_P$ .

Cette figure montre que la structure pourrait ne pas se comporter comme prévu. En effet, bien que le résultat de la configuration (1) était prévisible, les configurations (2) et (3) ne reflètent pas l'ordre d'amorçage attendu : la configuration (2) se comporte comme la configuration (1) tandis que la configuration (3) montre que le thyristor principal s'amorce avant le thyristor pilote. Tout se passe comme si un décalage vers le cas pessimiste s'était produit, décalage qui pourrait traduire un couplage entre les bases dopées n des thyristors pilote et principal. Cela aurait donc pour conséquence de biaiser le ratio $R_{\rm P}/R_{\rm M}$ .

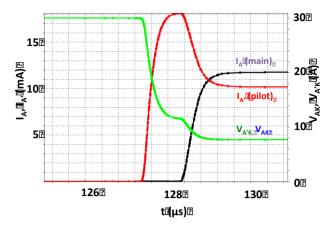

Ce biais peut être mis en évidence en ajoutant par simulation une résistance de très faible valeur (quelques ohms) entre les électrodes A' et A. Cela revient à placer cette résistance, discrète et notée  $R_{\rm M}$ ', en parallèle à la résistance interne  $R_{\rm M}$ .Le résultat à l'amorçage qui en découle pour la configuration (3) de l'AGT est présenté par la figure 4.

L'ajout de cette résistance  $R_{\rm M}$ ' permet de diminuer de façon significative la résistivité équivalente de la base n sous l'émetteur A du thyristor principal. Par conséquent, l'ordre d'amorçage est respecté. Le courant véhiculé par le thyristor prilote pourra être diminué vis-à-vis du celui du thyristor principal en diminuant  $R_{\rm P}$ . En effet, cette simulation reflète le cas où les anodes A' et A sont presque littéralement court-circuitées. En pratique, il pourrait convenir de dimensionner les masques du deuxième niveau de métallisation (voir paragraphe 2.3.1) par l'insertion de court-circuits localisés afin d'optimiser le ratio  $R_{\rm P}/R_{\rm M}$ . Cela permettrait de conserver les bénéfices apportés par la gâchette amplificatrice.

Fig. 4Simulation de l'amorçage de la structure AGT avec une résistance  $R_{\rm M}$ ' connectée entre A et A'.

#### 4. CONCLUSION

La conception du composant et les résultats de simulation par éléments finis, présentés dans cet article, ont pour but la réalisation et l'étude expérimentale du comportement dynamique d'un thyristor SiC avec gâchette amplificatrice. Les simulations montrent le bon fonctionnement du composant conçu et des calculs estimatifs donnent des indications sur la tolérance des paramètres technologiques tels que la résolution lithographique ou le dopage de la base n.

Un thyristor de base de 3 mm  $\times$  3 mm avec une structure de gâchette amplificatrice circulaire a été conçu. Pour faire varier le rapport  $R_{\rm P}/R_{\rm M}$  des résistances de la couche de base n, et donc l'effet de la gâchetteamplificatrice, le rayon  $r_{\rm SA}$  a été choisi comme seul paramètre et sa valeur minimale a été calculée. Le jeu de masque comportera donc différentsthyristors pour lequel $r_{\rm SA}$  varie autour de 384 µm.En plus, il y aura des thyristors avec les mêmes dimensions mais avec des court-circuits de l'anode au niveau du rayon  $r_{\rm SM}$  (voir figure 2). Dans un type de composant ce court-circuit aura une forme annulaire, permettant la comparaison directe avec le composant de base. Un autre type aura des court circuit en forme de petits points, connu de la technologie silicium, permettant d'élargir la surface d'anode au delà du rayon  $r_{\rm SM}$ .

Les simulations 2D à éléments finis suggèrent que l'hypothèse de dimensionnement sur le ratio  $R_{\rm P}/R_{\rm M}$  n'est pas suffisamment pertinente. Ce ratio ne permet pas de prendre en compte la variation dynamique des résistances (due à la modulation des porteurs lors de la mise en conduction des diodes bipolaires internes). Il a été démontré qu'il est néanmoins possible de simuler l'amorçage séquentiel des thyristors pilote et principal. Pour tirer plus de conclusions sur l'optimisation de la géométrie, il est nécessaire de ces travaux de simulation en passant à des coordonnées cylindriques ou même à une structure 3D et en prenant en compte l'impact de la durée de vie des porteurs sur le comportement dynamique. Des premiers travaux dans cette optique ont été faits [6].

L'objectif final sera de déterminer la dynamique de l'allumage de thyristors de type PCT et LTT en SiC et de la comparer à celle des thyristors en silicium. Ainsi le modèle de simulation qui sert à dimensionner des thyristors très haute tension ( $\geq 10~\rm kV$ ) pourra être finalement validé.

# 5. REMERCIEMENTS

Les auteurs remercient la DGA pour le soutien financier dans le cadre du projet AGaThE (ANR-11-ASTR-01101).

#### 6. References

- Niedernostheide F.J., Schulze H.J., Felsl H.P., Laska T., Kellner-Werdehausen U., and Lutz J., « Thyristors and IGBTs with Integrated Self-protection Functions », IET J. Circuits Devices Syst., vol.1, pp.315, 2007.

- [2] N. Dheilly, D. Planson, G. Pâques, and S. Scharnholz, « Light triggered 4H–SiC thyristors with an etched guard ring assisted JTE», Solid-State Electronics, vol. 73, pp. 32-36, 2012.

- [3] S. L. Rumyantsev, M. E. Levinshtein, S.M. Shur, L. Cheng, A.K. Agarwal, and J.W. Palmour, « High current (1300 A) optical triggering of 12 kV 4H-SiC thyristor », Semicond. Sci. Technol. 28 (045016), 2013.

- [4] Gentry F.E. and Moyson J., « The Amplifying Gate Thyristor », IEEE Int. Electron Devices Meet., vol.14, p.110, 1968

- [5] S. Scharnholz, G. Pâques, B. Vergne, C. Maurer, N. Dheilly, D. Planson, and R. D. Doncker, « Thyristors GTO haute tension en carbure de silicium avec terminaison JTE gravée », EPF 2012, Bordeaux (France).

- [6] L. V. Phung, D. Planson, P. Brosselard, D. Tournier, and C. Brylinski, "3D TCAD Simulations for More Efficient SiC Power Devices Design," ECS Transactions, vol. 58, pp. 331-339, 2013.