## Anisotropic Deep Reactive Ion Etching without Aspect Ratio Dependence Etching for silicon power devices

Aurélie Lecestre, Pascal Dubreuil, Sylvain Noblecourt, Josiane Tasselli, Éric Imbernon, Frédéric Morancho

## ▶ To cite this version:

Aurélie Lecestre, Pascal Dubreuil, Sylvain Noblecourt, Josiane Tasselli, Éric Imbernon, et al.. Anisotropic Deep Reactive Ion Etching without Aspect Ratio Dependence Etching for silicon power devices. PESM 2014 (Plasma Etch and Strip in Microtechnology), May 2014, Grenoble, France. 2p. hal-01054251

HAL Id: hal-01054251

https://hal.science/hal-01054251

Submitted on 6 Aug 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Anisotropic Deep Reactive Ion Etching without Aspect Ratio Dependence Etching for silicon power devices

<u>Aurélie LECESTRE</u><sup>1,3</sup>, Pascal DUBREUIL<sup>1,3</sup>, Sylvain NOBLECOURT<sup>1,2</sup>, Josiane TASSELLI<sup>1,3</sup>, Eric IMBERNON<sup>1,3</sup>. Frédéric MORANCHO<sup>1,2</sup>

<sup>1</sup>CNRS, LAAS, 7 avenue du colonel Roche, BP 54200 F-31031 Toulouse Cedex4, France

<sup>2</sup>Univ de Toulouse, UPS, LAAS, F-31031 Toulouse, France

<sup>3</sup>Univ de Toulouse, LAAS, F-31031 Toulouse, France

We present the optimization of the critical etching step for the fabrication of silicon Deep Trench-SuperJunction (DT-SJ) Diodes in order to obtain breakdown voltages of 1200V. The influence of the technological parameters on electrical performances has been studied by simulations, showing the importance of trenches verticality and width [1-2]. The aim is to fabricate an array of trenches of 6  $\mu$ m-width and 110 $\mu$ m-depth near to junction termination trenches of 80um width. The main challenge for etching deep trenches in silicon is high anisotropy with high aspect ratio: we studied the influence of DRIE passivation time on Critical Dimension loss [3]. ARDE effect (Aspect Ratio Dependent Etching) has been reduced by using a thermal silicon oxide mask: SiO<sub>2</sub> thicknesses have been determined in order to obtain the same depth whatever the trench aperture.

Critical points for deep trenches etching are: High Aspect Ratio (HAR), CD losses, low roughness surface of sidewalls (scalloping), narrowing on the trench top, Aspect Ratio Dependent Etching (ARDE).

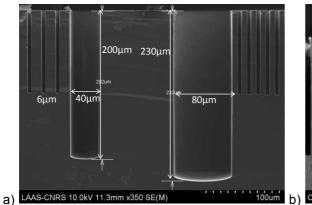

First of all, an HAR around 20 has been obtained thanks to Bosch process including two cycles: an etching step with  $SF_6$  followed by a passivation one with  $C_4F_8/O_2$ . This work is carried out with Alcatel - AMS4200 ICP (Inductively Coupled Plasma) DRIE equipment. In order to reduce CD loss, we have varied the passivation time/etching time ratio from 1.3 to 3. High anisotropy and low roughness surface have been achieved for a ratio of 1.75 (3.5s/2s). In these conditions, for trenches of 6 $\mu$ m-wide and 110 $\mu$ m-depth, the width difference between the top and the bottom of trenches is around 100nm and the scalloping is around 60nm (Fig. 1-a).

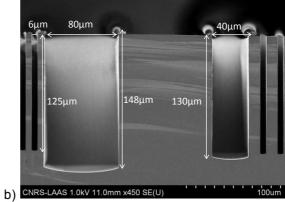

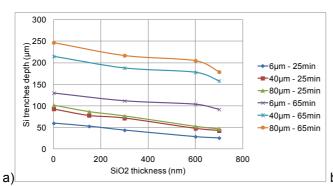

The second study has been carried on the ARDE effect. The aim is to obtain the same depth for two different widths. Indeed, for  $80\mu m$ -trench the etch rate is two times faster than for a  $6\mu m$  one. In order to reduce this etching rate difference, an oxide mask has been added only on the biggest aperture [4]. The influence of the oxide thickness on etching depth for various trench widths is reported on Fig. 2-a, for 25min and 65min etching times. Using a  $1.6\mu m$  oxide, the depth gap between  $6\mu m$  and  $40\mu m$  apertures is  $5\mu m$ , and the depth gap between  $6\mu m$  and  $80\mu m$  apertures is  $20\mu m$  as illustrated on Fig.1-b for a 65min etching time.

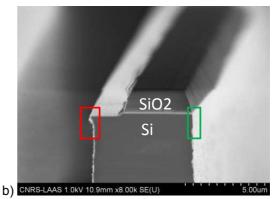

Moreover, the oxide layer on top of trenches allows the reduction of some negative effects related to Bosch process such as roughness surface (scalloping) and narrowing of the trench top (Fig. 2-b). So, the scalloping depth is decreased until 40nm.

Fig.1: SEM images of trenches with high aspect ratio (HAR>28) for an etching time of 65min: a) with  $SiO_2$  mask (300nm). b) with a selective  $SiO_2$  mask (1.6 $\mu$ m) to reduce the ARDE.

Fig.2: a) Si trenches depth variation versus SiO<sub>2</sub> mask thickness for two Si etching times (25min and 65min) and several trench widths (6μm, 40μm, 80μm).

b) Oxide effect on narrowing after photoresist elimination.

## References

- 1. L.Théolier, K. Isoird, F. Morancho, J. Roig, H. Mahfoz-Kotb, M. Brunet, P. Dubreuil, EPE 2007.

- 2. L. Théolier, H. Mahfoz-Kotb, K. Isoird, F. Morancho, S. Assié-Souleille, and N. Mauran, IEEE Electron Device Letters, vol. 30, no. 6, June 2009, p687-689.

- 3. Y. Zhu, G. Yan, J. Fan, J. Zhou, X. Liu, Z. Li and Y. Wang, J. Micromech. Microeng. 15 (2005) 636–642.

- 4. D. Belharet, P.F. Calmon, P. Dubreuil, J. Tasselli, H. Granier, PESM2012, Plasma Etch and Strip in Microelectronics, 15-16 mars 2012, Grenoble.

This work is supported by the ANR research project "SUPERSWITCH" and the French RENATECH network.

<sup>\*</sup> corresponding author e-mail: alecestr@laas.fr