## AlGaN/GaN MIS-HEMT gate structure improvement using Al2O3 deposited by PEALD

Richard Meunier, Alphonse Torres, Matthew Charles, Erwan Morvan, Marc Plissonnier, Frédéric Morancho

## ▶ To cite this version:

Richard Meunier, Alphonse Torres, Matthew Charles, Erwan Morvan, Marc Plissonnier, et al.. Al-GaN/GaN MIS-HEMT gate structure improvement using Al2O3 deposited by PEALD. 224th ECS Meeting, Oct 2013, San Francisco, United States. pp.269-277, 10.1149/05804.0269ecst. hal-01054216

HAL Id: hal-01054216

https://hal.science/hal-01054216

Submitted on 5 Aug 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## $\label{eq:algan} AlGaN/GaN\ MIS-HEMT\ Gate\ Structure \\ Improvement\ Using\ Al_2O_3\ Deposited\ by\ PEALD$

R. Meunier<sup>1</sup>, A. Torres<sup>1</sup>, M. Charles<sup>1</sup>, E. Morvan<sup>1</sup>, M.

Plissonier<sup>1</sup>, F. Morancho<sup>2</sup>

CEA-Leti, LC2E, 17 Rue des Martyrs, 38054 Grenoble

Cedex 9, France

<sup>2</sup>LAAS-CNRS, 7 Avenue du Colonel Roche, 31400 Toulouse, France

AlGaN /GaN heterostructures are very promising for the elaboration of high-power and high frequency devices because of their excellent electrical properties such as a high breakdown voltage, a high electron saturation velocity and a high mobility of the 2D electron gas. The Metal Insulator Semiconductor (MIS) gate structure with the introduction of high dielectric constant (high-k) materials as a gate dielectric represents one of the most promising ways to achieve viable power electronic devices [1,2]. Among various insulators commonly used in the world of microelectronics, Al<sub>2</sub>O<sub>3</sub> is mostly used for its deposition simplicity and has already lead to obtaining very good results, though it often needs post deposition treatments and surface pre-conditioning [3].

This work is focused on the capacitance/voltage C(V) and drain-current/gate-voltage  $I_d(V_g)$  measurements analysis for two different atomic layer deposition (ALD) techniques. In both cases, tri-methyl aluminum (TMA) was used as a precursor, but in one case water is used as oxidizer while oxygen plasma is used in the other. MESA etching isolation and ohmic contacts using Ti/Al annealed at 900°C were realized before a 10nm  $Al_2O_3$  deposition, and a Cr/Au gate was used. The C(V) measurement were carried out on  $400\mu m$  diameter diodes and Id(Vg) measurements were performed on 1mm width circular transistors with a  $100\mu m$  gate length.

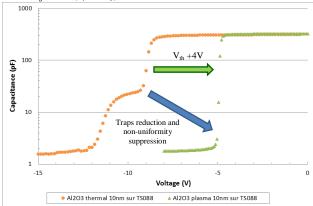

As we can see in Fig.1, two distinct behaviors appeared depending on the oxidation process used during the ALD. The one using  $H_2O$  showed a stepped C(V) curve while the one using oxygen plasma led to a smooth and steep non-stepped on/off transition. The threshold voltage (V $_{th}$ ) was also increased from ~9V to ~5V. In the latter case, the same sharp behavior and steady capacitance below  $V_{th}$  was also obtained for frequencies as low as 1kHz, while the  $H_2O$  samples led to negative capacitance below 50kHz.

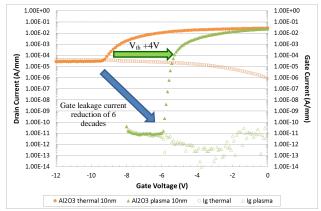

Regarding  $I_d(V_g)$  measurements, we see in Fig.2 the same increase in  $V_{th}$  as before, as well as a drastic gate leakage current  $(I_{leak})$  reduction for the plasma oxidized sample. We were thus able to obtain a threshold slope of 80mA/decades between the on and off state.

Regarding C(V) and  $I_d(V_g)$  results, the  $V_{th}$  improvement can be linked to a reduction of trapped charges through the  $O_2$ -plasma ALD deposition technique compared to  $H_2O$  ALD. Furthermore, the better quality of the  $O_2$ -plasma oxide is confirmed by stable low frequency measurements, while the negative capacitance with  $H_2O$  deposition is characteristic of a leaky behavior.

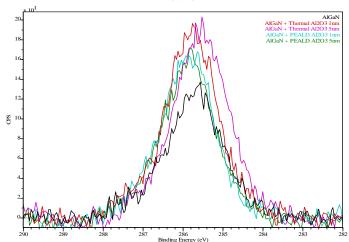

Those trapped charges can be associated to the carbon contamination of the AlGaN surface. The improvement of the results between the two deposition techniques may come from a better carbon removal at the surface during the first cycles of plasma assisted ALD. This was confirmed through XPS analysis. If we look at Fig.3, we can see the carbon level using PEALD is lower than the one for thermal ALD for samples with the same thickness of high-k deposited. Comparing to the AlGaN reference, the carbon level is slightly higher after high-k deposition due to a residue of CH3 inside the Al2O3 coming from the TMA precursor. As for the stepped behavior in the C(V) curves, it can be associated to a detachment at the gate periphery as shown on fig4. XPS analysis of thick Al<sub>2</sub>O<sub>3</sub> layers has also shown that CH3 removal is more efficient using PEALD.

In this study, we have shown that using  $O_2$ -plasma instead of water during the oxidation steps of the  $Al_2O_3$  ALD deposition drastically improves our device performances (threshold voltage and gate leakage current). Furthermore, these good results can be easily achieved without any specific surface preparation or post-deposition treatments.

## References

- [1] Hashizume T. and al., Japanese Journal of Applied Physics, The Japan Society of Applied Physics, 43 (2004) L777-L779.

- [2] N. Maeda et al, Microelec. Proceedings of SPIE, (2009) vol. 7216.

- [3] O. Saadat and T. Palacios, Solid-State Device Research Conference, (2011), 287-290.

**Fig. 1**: C(V) measurements for MIS diodes with 10nm  $Al_2O_3$  deposited by thermal and plasma enhanced ALD.

**Fig. 2**:  $I_d(V_g)$  measurements for circular transistors with 10nm  $Al_2O_3$  deposited by thermal and plasma enhanced ALD.

Fig. 3: C1s XPS spectra for different thicknesses of Al2O3 deposited by thermal and Plasma Enhanced ALD on AlGaN

Fig. 4: TEM image of the gate detachment at the gate periphery for thermal ALD