On-chip clock error characterization for clock distribution system

Résumé

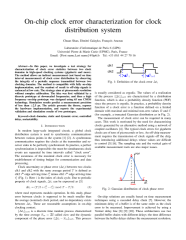

In this paper, we investigate a test strategy for characterization of clock error statistics between two clock domains in high-speed clocking systems (gigahertz and more). The method allows an indirect measurement (not based on time interval measurement) of clock error distribution by observing the integrity of a periodic sequence transmitted between two clocking domains. The method is compatible with fully on-chip implementation, and the readout of result to off-chip signals is cadenced at low rate. The strategy aims at picoseconds resolution without complex calibration. The idea was first validated by a discrete prototype at downscaled frequencies, and then a high frequency on-chip prototype was designed using 65 nm CMOS technology. Simulation results predict a measurement precision of less than ±2.5 ps. The article presents the theory, exposes the hardware implementation, and reports the experimental validation and simulation results of two prototypes.

Domaines

Electronique

Fichier principal

On-chip_clock_error_characterization_for_clock_distribution_system.pdf (332.38 Ko)

Télécharger le fichier

On-chip_clock_error_characterization_for_clock_distribution_system.pdf (332.38 Ko)

Télécharger le fichier

| Origine | Fichiers produits par l'(les) auteur(s) |

|---|

Loading...