# Conception de transistors MOS haute tension (1 200 volts) pour l'électronique de puissance

Loïc Théolier, Hicham Mahfoz-Kotb, Karine Isoird, Frédéric Morancho

# ▶ To cite this version:

Loïc Théolier, Hicham Mahfoz-Kotb, Karine Isoird, Frédéric Morancho. Conception de transistors MOS haute tension (1 200 volts) pour l'électronique de puissance. European Journal of Electrical Engineering, 2010, 13 (2), pp.227-252. 10.3166/ejee.13.227-252. hal-00991584

# HAL Id: hal-00991584 https://hal.science/hal-00991584v1

Submitted on 16 May 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Conception de transistors MOS haute tension (1200 Volts) pour l'électronique de puissance

Loïc Théolier\*'\*\* — Hicham Mahfoz Kotb\*\*\* — Karine Isoird\*'\*\* — Frédéric Morancho\*'\*\*

\* CNRS; LAAS

7 avenue du colonel Roche, F-31077 Toulouse, France {ltheolie, kisoird, morancho}@laas.fr

\*\* Université de Toulouse ; UPS, INSA, INP, ISAE ; LAAS F-31077 Toulouse, France

\*\*\* Department of Physics, Faculty of Science, Assiut University, 71516, Assiut, Egypt hesham74@yahoo.com

RÉSUMÉ. Dans le cadre de ces travaux, nous avons étudié différents principes pour concevoir une nouvelle structure MOS performante. Nous avons arrêté notre choix sur une structure se basant sur le concept de la Superjonction, réalisée par gravure profonde et diffusion de bore. Une grande partie des travaux de recherche a consisté à optimiser cette structure. Pour cela, nous avons étudié l'influence des paramètres technologiques et géométriques sur le compromis « tenue en tension / résistance passante spécifique ». Nous avons également développé une terminaison innovante afin d'assurer la tenue en tension du composant. Il a ensuite fallu identifier les étapes critiques du procédé de fabrication. À partir de ces résultats, nous avons réalisé une diode 1200 V qui nous a permis de valider certaines briques technologiques mais également la terminaison originale.

ABSTRACT. In this work, we have studied many concepts to design a new MOSFET structure. We have chosen a Superjunction based structure made by deep etching and boron diffusion. The main part of the work was to optimize this structure. For this, we have studied many technological parameter's influence on the "Breakdown voltage / On-state resistance" tradeoff. We have developed a new innovated junction termination in order to sustain the desired breakdown voltage. It was necessary to identify the process critical steps. From this point, we have fabricated a 1200 V diode which enabled to validate some of these steps but also the original termination.

MOTS-CLÉS: transistor MOS de puissance, tranchées profondes, Superjonction, simulation TCAD, terminaisons de jonction.

KEYWORDS: power MOSFET, deep trench, Superjunction, TCAD simulation, Junction termination.

DOI:10.3166/RIGE. volume. page1-26 © 2009 Lavoisier, Paris

#### 1. Introduction

L'amélioration de la chaîne de conversion de puissance dans la traction ferroviaire est indispensable pour diminuer son coût et son encombrement tout en augmentant sa fiabilité. Ces travaux de recherche s'inscrivent dans cette démarche en proposant l'utilisation d'une nouvelle structure MOS comme remplaçante des IGBTs constituant les modules de puissance 1200 Volts. Dans la gamme de tension visée, les structures MOS conventionnelles sont handicapées par leur résistance à l'état passant (R<sub>ON</sub>.S), et donc une chute de tension, importante par rapport aux composants bipolaires comme l'IGBT. Cette résistance à l'état passant est inversement proportionnelle au dopage de la zone volumique qui doit être suffisamment faible pour supporter la tension à l'état bloqué (BV<sub>DSS</sub>) : trouver le meilleur compromis entre ces deux paramètres (R<sub>ON</sub>.S / BV<sub>DSS</sub>) est un des défis majeurs, en particulier dans cette gamme de tension. Ainsi, l'objectif de notre étude est de s'inspirer des différents principes proposés dans la littérature pour concevoir une nouvelle structure MOS supportant une tension de 1200 Volts et présentant un compromis R<sub>ON</sub>.S / BV<sub>DSS</sub> considérablement amélioré par rapport aux structures physique simulation bidimensionnelle mais tridimensionnelle ainsi que la réalisation d'étapes technologiques ont été la base des résultats obtenus.

#### 2. Concept de la Superjonction

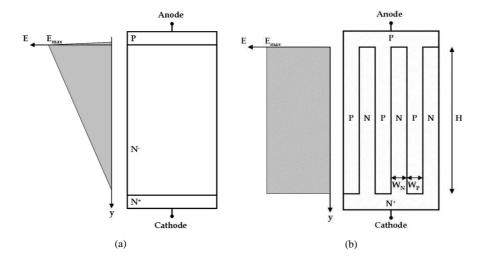

La Superjonction, présentée Figure 1, est composée d'une succession de bandes N et P remplaçant la zone N<sup>-</sup> de la diode PN<sup>-</sup>N<sup>+</sup> conventionnelle (Fujihira, 1997). À surfaces de silicium identiques, la surface de la jonction PN ainsi obtenue est alors beaucoup plus importante dans la Superjonction que dans la diode conventionnelle.

Le principe de la Superjonction nécessite un dopage et une largeur des bandes judicieusement choisis (par exemple :  $N_A = N_D$  et  $W_N = W_P = W << H$ ). L'application d'une tension positive sur la cathode induit alors un phénomène en deux étapes :

- dans un premier temps, puisque W << H, les couches N et P se dépeuplent plus vite latéralement que verticalement : ainsi, seule la composante  $E_x$  du champ électrique augmente mais reste inférieure à la valeur du champ critique  $E_c$ .

- dans un deuxième temps, puisque le dépeuplement des bandes N et P est total, la distribution du champ électrique dans le volume est uniforme : en effet, on peut admettre que les régions P et N entièrement dépeuplées sont équivalentes à un diélectrique. La tension appliquée entre la cathode (c'est-à-dire le drain pour le transistor MOS) et l'anode (source) est alors proportionnelle à la profondeur H et devient indépendante du dopage. Elle obéit à la relation suivante :

$$V_{DSS} = E_{y} \cdot H \tag{1}$$

Conception de transistors MOS haute tension pour l'électronique de puissance 3

**Figure 1.** (a) Coupe schématique et répartition du champ électrique d'une diode  $PNN^+$ , (b) Coupe schématique et répartition du champ électrique d'une Superjonction.

Comme pour une diode conventionnelle, la tension de claquage  $BV_{DSS}$  est atteinte lorsque le champ électrique atteint sa valeur critique ; cette tension vaut donc ici :

$$BV_{DSS} = E_c \cdot H \tag{2}$$

La tenue en tension de la Superjonction est donc proportionnelle au champ électrique critique alors que, dans la diode PN N $^+$  conventionnelle, elle est proportionnelle à  $E_c^{-5}$  selon la relation (Sze et al., 1966) :

$$BV_{DSS} = 4,49 \cdot 10^{29} \cdot E_c^{-5}$$

[3]

Notons que, de manière générale, les conditions :  $N_A = N_D$  et  $W_N = W_P$  ne sont pas obligatoires ; le bon fonctionnement de la Superjonction est assuré si :

- les bandes N et P sont complètement dépeuplées avant que le champ électrique critique ne soit atteint,

- la balance des charges entre les régions N et P est quasi-parfaite.

Quantitativement, ces deux conditions peuvent être traduites par :

$$\frac{q \cdot N_D \cdot W_N}{2 \cdot \varepsilon_0 \cdot \varepsilon_{Si}} = \frac{q \cdot N_A \cdot W_P}{2 \cdot \varepsilon_0 \cdot \varepsilon_{Si}} < E_c, \tag{4}$$

Soit:

$$N_D \cdot W_N = N_A \cdot W_P$$

[5]

Le principal avantage de la Superjonction est que le dopage des régions N et P peut être choisi supérieur au dopage de la région  $N^-$  d'une diode  $PN^-N^+$  conventionnelle : ici, ce n'est plus la concentration  $N_D$  qui est primordiale mais la balance des charges entre les régions N et P. Appliqué aux composants de puissance unipolaires comme les transistors MOS, ce nouveau concept doit donc permettre de diminuer fortement leur résistance passante spécifique.

Les limites de performances de ces nouveaux composants en terme de compromis «  $R_{ON}$ .S /  $BV_{DSS}$  » ont d'ailleurs été calculées (Fujihira, 1997).

Dans le cas des structures MOS verticales, Fujihira a proposé la relation suivante :

$$R_{ON}.S(\Omega.cm^2) = 1.98 \cdot 10^{-1} \cdot W^{\frac{5}{4}} \cdot BV_{DSS}$$

[6]

Ainsi, la limite théorique du compromis  $R_{ON}$ . S /  $BV_{DSS}$  des structures à Superjonction (Fujihira, 1997) dépasse largement la limite théorique des structures conventionnelles (Morancho, 2004) :

$$R_{ON}.S(\Omega.cm^2) = 8.9.10^{-9}.BV_{DSS}^{2.4}$$

[7]

La simple comparaison de cette relation avec la limite théorique des composants unipolaires conventionnels montre que, dans le cas des composants MOS à Superjonction, la résistance passante spécifique minimale est directement proportionnelle à  $BV_{DSS}$  pour les structures verticales — contre  $BV_{DSS}^{2,4}$  —. La Figure 2 compare les limites des composants MOS conventionnels et des composants MOS à Superjonction. Il apparaît clairement que, pour des tenues en tension élevées, les MOS à Superjonction sont supérieurs aux MOS conventionnels.

**Figure 2.** Comparaison des limites théoriques — compromis «  $R_{ON}$ . $S / BV_{DSS}$  » — des composants verticaux conventionnels et à Superjonction.

# 3. Présentation des différentes structures MOS envisagées pour concurrencer l'IGBT 1200V

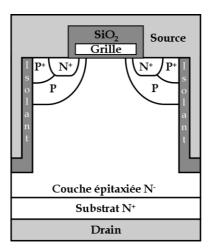

#### 3.1. Le transistor OBVDMOS

L'OBVDMOSFET (Oxyde-Bypassed VDMOSFET), présenté Figure 3, est composé de tranchées profondes remplies d'un oxyde épais et de polysilicium connecté à la source (Liang, 2001). Lorsque l'on applique une tension sur le drain, on déserte verticalement, mais également latéralement la zone N<sup>-</sup>. La largeur entre deux tranchées d'oxyde étant inférieure à l'épaisseur de l'épitaxie, la zone de drift est totalement désertée ce qui entraîne un accroissement de la composante latérale du champ électrique, sans que sa valeur critique ne soit atteinte : il en résulte donc une augmentation de la tenue en tension. Donc, pour une même tenue en tension visée, le dopage de la zone N<sup>-</sup> sera plus important et la résistance passante spécifique réduite, bien que la zone de conduction soit elle aussi réduite en raison de l'encombrement dû aux tranchées. La limitation de cette structure provient donc du compromis « augmentation du dopage / diminution de la surface de conduction ».

Figure 3. Coupe schématique du transistor OBVDMOS.

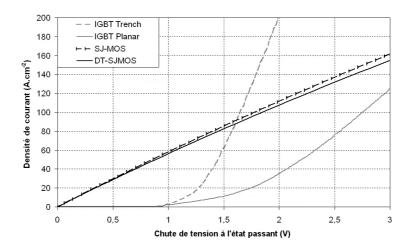

## 3.2. Le transistor SJMOS

Le transistor SJMOS (SuperJunction MOSFET) est composé de colonnes P sous les caissons P de source de façon à ne pas nuire à la conduction du courant sous la grille (Figure 4). Infineon a commercialisé des transistors à Superjonction (COOLMOS<sup>TM</sup>) sur ce principe dès 1999 (Lorenz, 1999) et ST Microelectronics au début des années 2000 (MDMESH<sup>TM</sup>). Le transistor SJMOS serait un bon candidat d'après les limites théoriques de la structure. Néanmoins, il n'y a pas de structure

1200 Volts commercialisée à ce jour car la réalisation de telles structures nécessiterait un nombre rédhibitoire de masques en utilisant la technologie classique de multi-épitaxie. L'étude du transistor SJMOS se base sur une structure dont la colonne P n'atteint pas le substrat (Sagio, 2000).

Figure 4. Coupe schématique du transistor SJMOS.

#### 3.3. La structure DT-SJMOS

Les techniques utilisées actuellement pour fabriquer des composants à Superjonction se basent sur une implantation forte énergie ou une succession d'épitaxies et d'implantations pour créer les bandeaux N et P (Saito, 2006). La technologie envisagée ici pour réaliser les bandes P est basée sur une gravure profonde. Cette étape est suivie d'un dépôt d'oxyde fin puis d'un dépôt de polysilicium dopé bore. Les bandeaux P sont réalisés par diffusion à travers cet oxyde mince afin de mieux contrôler la dose. Les tranchées sont ensuite nettoyées et remplies d'un diélectrique. La cellule élémentaire est présentée Figure 5. L'avantage de la technologie du DT-SJMOS est de pouvoir réaliser des bandes P d'environ 100 µm de profondeur sans utiliser les techniques de multi-épitaxie ou d'implantation forte énergie qui sont coûteuses en fabrication et difficiles à mettre en œuvre.

Conception de transistors MOS haute tension pour l'électronique de puissance 7

**Figure 5.** Coupe schématique de la cellule élémentaire du transistor DT-SJMOS.

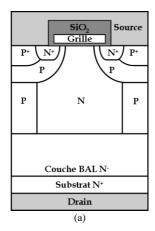

#### 3.4. Les transistor semi-SJMOS

Le transistor semi-SJMOS (association du concept de Superjonction et de jonction conventionnelle), basé sur les travaux de Saito (Saito et al., 2003), est présenté Figure 6. En effet, il est possible d'augmenter la tenue en tension d'un composant en plaçant une zone  $N^-$  faiblement dopée, dite « couche BAL » (Bottom Assist Layer), sous les colonnes P et N. Une amélioration de ce concept peut également être obtenue en insérant un îlot flottant dans la couche BAL afin d'augmenter la concentration de celle-ci.

**Figure 6.** Coupe schématique du transistor semi-SJMOS (a) sans ilots, (b) avec un ilot flottant dans la couche BAL.

# 4. Simulation électrique

#### 4.1. Choix de la structure

Les simulations électriques sont faites avec le logiciel SENTAURUS-TCAD. Nous avons simulé l'état bloqué de différentes structures habituellement utilisées à plus faible tension dans le but de déterminer leurs performances à 1200 Volts. Ainsi les transistors UMOS, OBVDMOS (Liang, 2001), SJMOS (Fujihira, 1997), DT-SJMOS et semi-SJMOS (Saito et al., 2003) avec ou sans îlots sont simulés à l'état passant afin de comparer la résistance passante spécifique de chaque structure. Le tableau 1 résume les différentes valeurs obtenues avec une largeur de cellule de 10 µm.

|                               | UMOS  | OBVDMOS | SJMOS | Semi-SJMOS | Semi-SJMOS   | DT-SJMOS |

|-------------------------------|-------|---------|-------|------------|--------------|----------|

|                               |       |         |       | sans îlot  | avec un îlot |          |

|                               |       |         |       |            |              |          |

| $R_{ON}.S$ (m $\Omega.cm^2$ ) | 507,6 | 435,44  | 16,44 | 232,39     | 138,17       | 16,84    |

|                               |       |         |       |            |              |          |

**Tableau 1.** Résistances passantes spécifiques des différentes structures MOS étudiées pour une tenue en tenson de 1200 V.

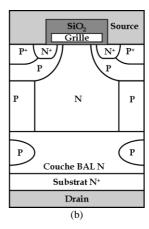

Les deux meilleures structures sont les transistors SJMOS et DT-SJMOS. En effet, leurs résistances sont dix fois inférieures à celle du transistor Semi-SJMOS avec un îlot flottant et trente fois inférieures à celle d'un transistor MOS conventionnel (ici l'UMOS). Ces résultats ne permettent pas d'affirmer pour autant que ces deux structures soient potentiellement capables de remplacer l'IGBT 1200 V. Nous avons, pour cela, comparé la densité de courant admissible en fonction de la chute de tension pour chaque structure simulée (Figure 7) à deux technologies récentes d'IGBT, en l'occurrence la troisième génération des IGBTs à grille planar et les IGBTs à grille en tranchée (Motto, 1998).

Figure 7. Caractéristiques de transfert des différents composants étudiés.

Les transistors SJMOS et DT-SJMOS sont des candidats potentiels pour concurrencer l'IGBT 1200 V (Figure 7). Ces transistors affichent une densité de courant bien plus importante que la troisième génération d'IGBT et restent intéressants face à l'IGBT à grille en tranchée pour de faibles valeurs de chute de tension à l'état passant (densité de courant inférieure à 90 A.cm<sup>-2</sup>). Pour des raisons technologiques liées aux contraintes de la plateforme du LAAS-CNRS, la structure DT-SJMOS a été préférée à la structure SJMOS (Théolier, 2008) : nous avons souhaité étudier l'influence des différents paramètres technologiques et géométriques sur la tenue en tension du DT-SJMOS notamment.

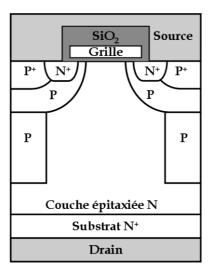

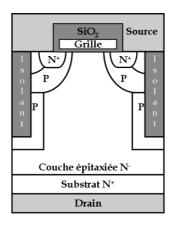

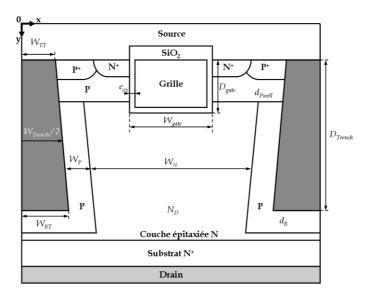

# 4.2. Étude du composant DT-SJMOS

L'ensemble des paramètres géométriques et technologiques de la structure (Figure 8) est susceptible de varier du fait de la maîtrise imparfaite du procédé de fabrication. Une attention particulière fut portée à certains éléments pour l'importance de leur effet sur BV<sub>DSS</sub>. Nous nous proposons maintenant de les étudier avec une structure à grille en tranchée, ce qui permet, notamment, de diminuer la taille de la cellule élémentaire.

**Figure 8.** Coupe schématique du transistor DT-SJMOS avec les paramètres influençant  $BV_{DSS}$  et  $R_{ON}$ .S.

#### 4.2.1 Influence de la quantité de charges diffusée

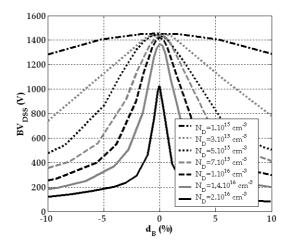

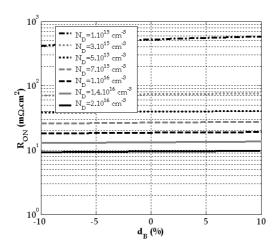

La Figure 9 présente les variations de la tenue en tension en fonction de l'erreur (en pourcentage) par rapport à la dose de bore optimale diffusée. Nous constatons que la sensibilité est dépendante de la concentration de la couche épitaxiée. En effet, dans le cas des fortes concentrations  $N_D$ , cas qui est le plus intéressant en terme de résistance passante spécifique (Figure 10), nous observons qu'un faible déséquilibre de charge entraı̂ne une spectaculaire diminution de la tenue en tension. Une faible concentration ( $10^{15}~\rm cm^{-3}$ ) permettrait ainsi d'avoir plus de latitude dans la réalisation. Toutefois, les bénéfices des Superjonctions seraient alors considérablement diminués. En effet, à ce niveau de concentration, les résistances passantes spécifiques des transistors UMOS et DT-SJMOS seraient alors du même ordre de grandeur car l'augmentation de  $N_D$  serait compensée par la diminution de la surface de conduction.

Dans le cas de l'optimisation de la structure, nous remarquons qu'il existe une concentration de dopage de la zone épitaxiée (1,4.10 $^{16}$  cm $^{-3}$ ) au-delà de laquelle la tenue en tension chute brusquement, même à l'équilibre des charges. Ceci est dû au fait que le champ électrique atteint pratiquement sa valeur critique au moment du phénomène d'autoblindage (désertion latérale complète protégeant la jonction principale en surface). Il existe donc un compromis entre la concentration du dopage de la couche épitaxiée  $N_{\rm D}$  et la largeur de la cellule, même pour des profils

gaussiens. La concentration de la couche épitaxiée ( $N_D$ ) retenue pour l'optimisation de la structure est égale à 1,4.10<sup>16</sup> cm<sup>-3</sup> avec une dose de bore diffusée ( $d_B$ ) de 2,8.10<sup>12</sup> cm<sup>-2</sup> car ces valeurs offrent la meilleure résistance passante spécifique ( $R_{ON}$ .S = 13 m $\Omega$ .cm<sup>2</sup>) tout en gardant une tenue en tension bien au-delà de 1200 Volts.

**Figure 9.** Variations de la tenue en tension en fonction de l'écart par rapport à la dose de bore optimale pour différentes concentrations de l'épitaxie  $(N_D)$ .

**Figure 10.** Variations de la résistance passante spécifique en fonction de l'écart par rapport à la dose de bore optimale pour différentes concentrations de l'épitaxie  $(N_D)$ .

## 4.2.2. Compensation de la gravure par la dose diffusée

L'équation [8] rappelle la condition d'équilibre des charges dans le cas d'un profil gaussien.

$$\int_{W_{Trench}/2}^{W_{Trench}/2+W_P} N_A(x) dx = N_D \times \frac{W_N}{2}$$

[8]

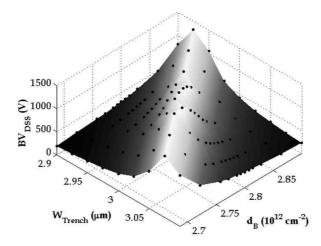

La largeur de la gravure ayant un impact sur l'équilibre des charges, nous nous intéressons à la compensation de l'erreur d'ouverture des tranchées par la dose de bore diffusée. La Figure 11 présente les variations de la tenue en tension par rapport à la largeur de la tranchée ( $W_{Trench}$ ) et la dose de bore diffusée ( $d_B$ ). Nous constatons qu'il est possible de compenser un paramètre par l'autre. En effet, les deux paramètres interviennent dans la balance des charges. Une augmentation de la largeur de la tranchée, par rapport à l'ouverture de masque initiale, entraîne une diminution de la largeur entre deux tranchées, c'est-à-dire une diminution de  $W_N$ . Il est alors possible de corriger le profil de bore diffusé, notamment par la dose, afin de retrouver l'équilibre des charges. Le haut de la crête, en blanc, correspond à une tenue en tension de 1400 V. Plusieurs couples de valeurs permettent d'obtenir cette tenue en tension, notamment  $W_{Trench} = 3~\mu m$  et  $d_B = 2,8.10^{12}~cm^{-2}$ . Cette valeur de largeur de tranchée correspond à l'ouverture de masquage retenue.

**Figure 11.** Variations de la tenue en tension en fonction de la largeur de la tranchée profonde et de la dose de bore diffusée.

#### 4.2.3. Variations de la verticalité de la tranchée

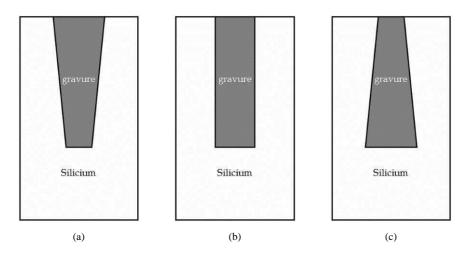

La verticalité de la tranchée (Slope) est définie par la différence de largeur entre le haut  $(W_{TT})$  et le bas  $(W_{BT})$  de la tranchée. Une valeur positive de Slope (Figure 12 (a)) correspond à une gravure en forme de cône dont la pointe est dans le fond de la tranchée ; inversement, une valeur négative de Slope correspond à une gravure en forme de trapèze dont la partie large est dans le fond de la tranchée (Figure 12 (c)).

**Figure 12**. (a) Tranchée à pente positive, (b) tranchée à pente verticale, (c) tranchée à pente négative.

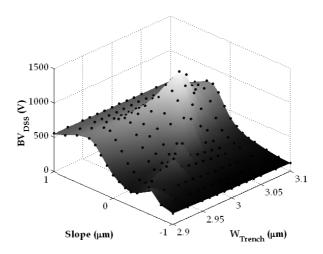

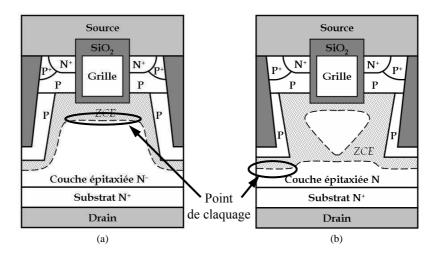

La Figure 13 présente les variations de la tenue en tension en fonction de la verticalité de la tranchée (Slope) et de la largeur de la gravure (W<sub>Trench</sub>). Nous pouvons remarquer que la tenue en tension est très sensible à la verticalité de la tranchée. En effet, l'excès de charges à une extrémité de la tranchée n'est pas compensé par le manque de charges à l'autre extrémité comme le rappelle l'équation [8] qui présente l'équation de l'équilibre des charges : celle-ci est unidimensionnelle (dépendante seulement de x, soit de la largeur dans notre cas). Il faut donc que la condition énoncée soit respectée sur toute la profondeur de la structure. Sinon, il y a une très forte probabilité de dégradation de la tenue en tension. De plus, la courbe des variations de la tenue en tension en fonction de la verticalité de la tranchée est asymétrique. En effet, une tranchée plus large en surface permet de protéger la jonction plane en surface et augmente donc légèrement sa tenue en tension (Figure 14 (a)). Par contre, une tranchée plus large en profondeur implique un autoblindage en son fond, et c'est donc la jonction PN sous la tranchée qui doit supporter la tension (Figure 14 (b)). La dose de bore diffusée n'étant pas calibrée pour cette situation, la tenue en tension de cette jonction se trouve inférieure

à la tenue en tension de la jonction de surface. De plus, sous la condition de dose optimale de bore, nous devons garantir une verticalité de  $\pm$  0,1  $\mu$ m pour avoir une tenue en tension supérieure à 1200 Volts.

**Figure 13.** Variations de la tenue en tension en fonction de la pente (Slope) et de la largeur ( $W_{Trench}$ ) de la tranchée profonde.

**Figure 14.** (a) Représentation schématique de la ZCE au claquage de la structure pour Slope > 0, (b) Représentation schématique de la ZCE au claquage de la structure pour Slope < 0.

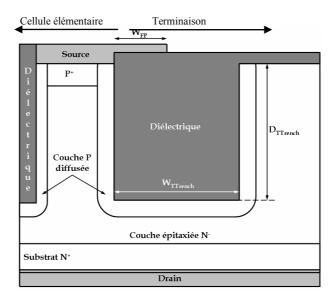

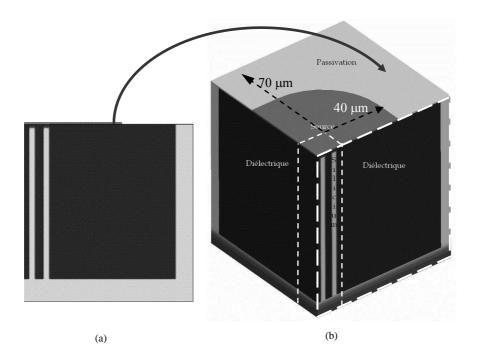

# 4.3. Présentation de la DT<sup>2</sup>

Les techniques de terminaison de jonction sont basées sur la nécessité d'étaler au mieux la zone de charge d'espace déployée par la jonction polarisée en inverse. Il est en effet nécessaire de distribuer le potentiel sur la plus grande surface de silicium possible. Cela permet de diminuer son gradient, c'est-à-dire le champ électrique. Avec les nouveaux concepts, dans lesquels le champ électrique est réparti dans le volume du composant, nous avons donc besoin de terminaisons « volumiques ». La terminaison développée pour notre composant est présentée Figure 15. La terminaison est réalisée par une tranchée large et profonde remplie de diélectrique assistée par une plaque de champ en surface (Deep Trench Termination – DT²). Nous devons aussi réaliser la diffusion du bore autour de cette tranchée pour garantir l'équilibre des charges dans la dernière cellule élémentaire.

Figure 15. Coupe schématique de la terminaison pour le transistor DT-SJMOS.

# 4.3.1. Sensibilité de BV<sub>DSS</sub> à la géométrie de la tranchée de terminaison

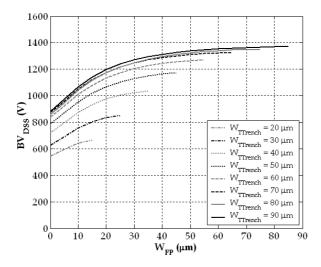

Nous nous intéressons à la sensibilité de la tenue en tension en fonction de la géométrie de la tranchée de terminaison. La Figure 16 présente les variations de la tenue en tension en fonction de la largeur de la plaque de champ  $(W_{\text{FP}})$  pour différentes largeurs de tranchée de terminaison  $(W_{\text{TTrench}})$ .

**Figure 16.** Variations de la tenue en tension de la terminaison en fonction de la largeur de la plaque de champ  $(W_{FP})$  pour différentes largeurs de tranchée de terminaison  $(W_{Trench})$ .

La tenue en tension dépend de la largeur de la tranchée et de la plaque de champ. Sans plaque de champ ( $W_{FP}=0~\mu m$ ), la tenue en tension est limitée à 900 V (soit 65 % de la tenue en tension de la cellule élémentaire) pour une tranchée de 90  $\mu m$  de large. De plus, toujours sans plaque de champ, il semble impossible de s'approcher de la tenue en tension de la cellule élémentaire, par extrapolation du réseau de caractéristiques. À l'inverse, la structure tient 99 % de la tenue en tension de la cellule élémentaire pour les dimensions suivantes :  $W_{FP}=85~\mu m$  et  $W_{TTrench}=90~\mu m$ .

Le meilleur compromis entre la tenue en tension et la dimension de la terminaison semble être  $W_{FP}=40~\mu m$  et  $W_{TTrench}=70~\mu m$ , pour une tenue en tension de 1325 V. Augmenter la largeur de la tranchée au-delà de 70  $\mu m$  n'apporte que très peu d'amélioration. Quant à la plaque de champ, nous préférons garder une largeur importante entre l'extrémité de la plaque de champ et la tranchée, pour s'assurer de ne pas avoir de rupture électrique dans les passivations de surface.

# 4.3.2. Sensibilité de $BV_{DSS}$ au choix du diélectrique de la tranchée de terminaison

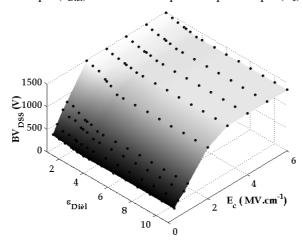

Les simulations précédentes ont été effectuées avec une tranchée remplie par de l'oxyde de silicium (SiO<sub>2</sub>); or il est inenvisageable d'utiliser ce matériau pour remplir une tranchée avec ces dimensions (temps de dépôt trop long). Il est donc indispensable de connaître les caractéristiques que doit posséder le diélectrique de remplissage pour assurer l'efficacité de la terminaison. La Figure 17 présente les

variations de la tenue en tension de la terminaison en fonction de la permittivité relative du diélectrique ( $\epsilon_{Diél}$ ) et de son champ électrique critique ( $E_c$ ).

**Figure 17.** Variations de la tenue en tension de la terminaison en fonction de la permittivité relative ( $\varepsilon_{Di\acute{e}l}$ ) et du champ électrique critique du diélectrique ( $E_c$ ).

Nous observons que la tenue en tension est dépendante du champ électrique critique du diélectrique. En effet, le resserrement des lignes de potentiel autour de l'extrémité de la plaque de champ crée une augmentation locale du champ électrique que le diélectrique doit contenir. Pour les dimensions retenues ( $W_{FP} = 40~\mu m$  et  $W_{TTrench} = 70~\mu m$ ), le champ électrique minimum du diélectrique doit être de 3 MV.cm<sup>-1</sup>. En dessous de cette valeur, la structure claque en terminaison; et, au-delà, dans les cellules élémentaires.

La permittivité du diélectrique  $\epsilon_{Diél}$ , quant à elle, a peu d'influence sur la tenue en tension. Nous pouvons néanmoins noter une amélioration de la tenue en tension pour de faibles valeurs de permittivité. Ce résultat est dû à l'étirement des lignes de potentiel dans le silicium en raison de la grande différence de permittivité. Ce gain est néanmoins faible (10%) et n'est pas déterminant dans le choix du diélectrique. Le diélectrique retenu devra avoir un champ électrique critique supérieur à 3 MV.cm<sup>-1</sup> et une permittivité relative la plus faible possible bien que ce critère ne soit pas décisif.

#### 4.3.3. Étude du comportement de la terminaison en trois dimensions

Nous avons souhaité connaître les performances de cette terminaison dans les coins de la puce. En effet, les simulations bidimensionnelles (2D), réalisées jusqu'alors, présentent le comportement de la structure dans les zones à faible variation de géométrie dans la profondeur. Le coin d'une structure présente

généralement une jonction cylindrique, voire sphérique, où le champ électrique augmente localement jusqu'à induire un claquage prématuré.

#### 4.3.1.1. Présentation de la terminaison en 3D

La structure simulée en 2D est présentée Figure 18 (a) et la structure tridimensionnelle Figure 18 (b). Nous prenons comme hypothèse que les cellules élémentaires sont des bandes ; la surface occupée par ces cellules est encadrée en pointillés serrés blancs sur la Figure 18 (b). La plaque de champ ainsi que la tranchée sont arrondies dans l'angle pour avoir une largeur constante autour de la dernière bande de silicium. Les dopages et les profondeurs de tranchées restent identiques aux valeurs utilisées dans les simulations 2D.

Il est à noter que les simulations 2D sont faites avec des structures décrites par 10 000 nœuds de calcul. Cette structure 3D est décrite par 170 000 nœuds de calcul.

**Figure 18.** (a) Représentation de la terminaison simulée en 2D, (b) représentation de la terminaison simulée en 3D.

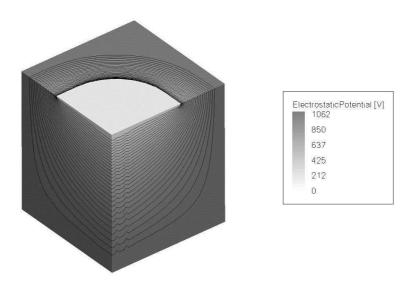

# 4.3.1.2. Répartition des lignes de potentiel dans la terminaison

La Figure 19 présente la répartition des lignes de potentiel dans la terminaison en coin du composant. La répartition de celles-ci se fait de façon homogène dans le volume. Les lignes de potentiel sont confinées dans la tranchée et remontent en surface entre l'extrémité de la plaque de champ et l'extrémité de la tranchée comme pour la structure 2D. Néanmoins, la terminaison ne tient que 80% de la structure décrite en 2D (1060 V par rapport à 1325 V). La répartition des lignes de potentiel selon les trois axes autour des cellules élémentaires implique une augmentation du champ électrique dans le silicium.

Il est commun d'entendre que les simulations surestiment la tenue en tension des structures. En effet, la représentation bidimensionnelle ne prend pas en compte les variations de potentiel dans le troisième axe. Nous venons néanmoins, avec des moyens techniques importants, de prendre en compte cette variation. Maintenant que nous savons que la structure ne tient que 1060 V dans le coin du composant, nous devrons réajuster la géométrie de la terminaison ou augmenter la profondeur des tranchées et celle de l'épitaxie afin d'augmenter la tenue en tension du composant.

**Figure 19.** Répartition des lignes de potentiel dans la terminaison en coin du composant.

## 5. Résultats expérimentaux

Au vu des différentes simulations, nous avons identifié quatre étapes critiques pour la réalisation du composant. La première est la gravure profonde avec la maîtrise de largeur et de la verticalité des tranchées, la seconde est le remplissage de ces tranchées par un diélectrique adapté, la troisième est le polissage de la surface de la plaquette et, enfin, la dernière, et certainement la plus critique, est le contrôle de la diffusion du bore à travers les parois des tranchées.

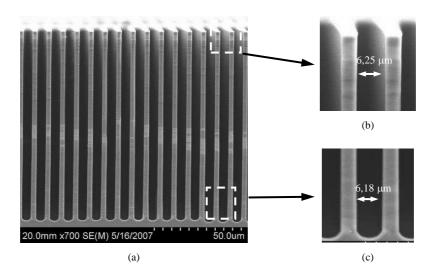

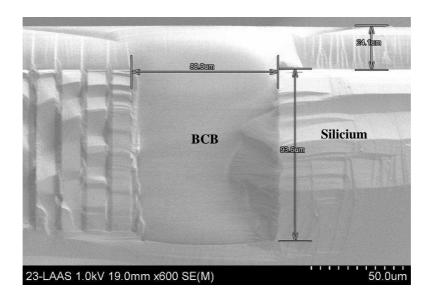

## 5.1. La gravure

La Figure 20 (a) présente une image, par Microscope Électronique à Balayage (MEB), des tranchées réalisées par la méthode BOSCH (Lärmer, 1996). Nous pouvons observer une bonne verticalité des gravures avec un facteur de forme (ratio entre profondeur et largeur) proche de 20. Des agrandissements sur le haut et sur le bas de la tranchée (Figure 20 (b) et Figure 20 (c)) montrent des largeurs de tranchée respectives de 6,25  $\mu m$  et de 6,18  $\mu m$ . La pente (Slope =  $W_{TT}$  -  $W_{BT}$ ) est de 70 nm. Nous pouvons considérer ce résultat comme suffisant car la concentration la plus élevée, et donc la plus critique, demande un écart de largeur inférieur à 200 nm. Il est à noter que ces tranchées sont obtenues pour une ouverture masque de 4  $\mu m$ . Nous obtenons donc une surgravure de 2  $\mu m$  qu'il faudra prendre en compte dans le choix de la dose de bore à diffuser.

**Figure 20.** (a) Photographies MEB des gravures après optimisation du procédé, (b) agrandissement sur le haut de la tranchée, (c) agrandissement sur le fond de la tranchée.

## 5.2. Remplissage des tranchées

Du fait des dimensions des tranchées, il est impossible de les remplir par dépôt classique (LPCVD, PECVD...) de diélectrique. Nous avons donc opté pour un dépôt de diélectrique à la tournette (S.O.D.). Les S.O.D., de manière générale, ont une température de transition vitreuse assez basse (inférieure à 900 °C). Au-delà de cette température, ces matériaux passent d'un comportement solide à un comportement solide plastique, suite à l'affaiblissement de liaisons intermoléculaires; or les températures de recuit nécessaires pour activer les dopants après les implantations sont généralement autour de 1000 °C. Le dépôt de ces diélectriques doit donc se faire après toutes les étapes d'activation des porteurs. Ceci implique que nous devons réaliser les étapes conventionnelles de fabrication d'un transistor MOS de puissance dans un premier temps puis finir par le remplissage des tranchées.

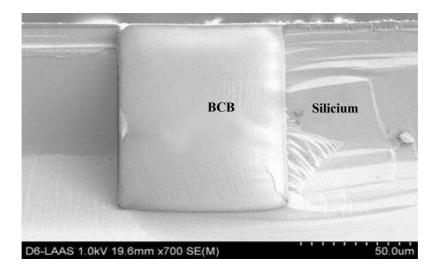

Le champ critique du BCB étant de 5,3 MV.cm<sup>-1</sup> et sa constante diélectrique de 2,65, ce matériau remplit les critères nécessaires pour assurer l'efficacité de la DT<sup>2</sup>. Nous avons donc choisi de tester ce matériau pour remplir les tranchées centrales et celle de terminaison. Nous avons rempli la tranchée de terminaison par deux dépôts successifs de BenzoCycloButene (BCB). La méthode retenue est la suivante : nous déposons le BCB puis nous patientons 5 minutes. Nous étalons le BCB par tournette à vitesse croissante, puis nous durcissons la résine par un recuit de 250 °C sous flux d'azote pour éviter l'oxydation du BCB. Une fois la résine durcie, nous recommençons une deuxième fois les mêmes étapes (Mahfoz-Kotb et al., 2008).

La Figure 21 présente le remplissage réussi des tranchées des cellules élémentaires et de la tranchée de terminaison. Nous ne constatons aucune cassure des colonnes de silicium ou du BCB. Ce matériau convient donc parfaitement au remplissage des tranchées fines ou larges et offre donc de nombreuses applications en microélectronique. Le remplissage des tranchées par deux couches successives de BCB implique la création une couche épaisse d'environ 40 µm en surface. Nous avons proposé de retirer cette couche par polissage mécanico-chimique (CMP) qui est une méthode rapide et moins coûteuse que la gravure sèche.

**Figure 21.** Remplissage réussi pour les tranchées de terminaison et des cellules élémentaires avec deux dépôts de BCB.

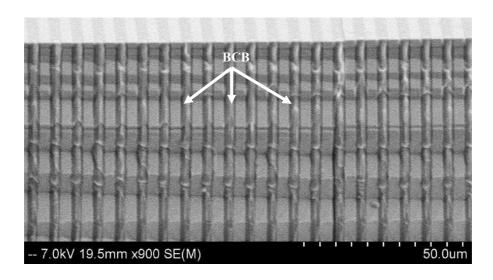

## 5.3. Polissage

Une des contraintes du polissage est celle du temps et donc du coût. La vitesse de gravure dépend de la composition du bain chimique, de la taille des abrasifs et de la vitesse de rotation des plateaux notamment. Il y a donc un compromis à trouver. Pour répondre à cette contrainte, nous avons développé une méthode de polissage mixte (Mahfoz-Kotb et al., 2008).

La Figure 22 présente le polissage du BCB en terminaison sur un substrat n'ayant pas subi d'étape d'implantation ou de réalisation de grille. Les conditions de polissage ont été présentées. Nous constatons visuellement que le polissage offre une bonne planéité de surface : il devrait donc être aisé de réaliser la plaque de champ sur cette surface. Concernant le polissage des tranchées en cellules élémentaires (Figure 23), nous pouvons constater que l'ensemble « colonne de silicium et résine » a supporté les contraintes mécaniques du polissage. Nous n'observons aucune fissure des colonnes de silicium.

**Figure 22.** *Photographie MEB de la tranchée de terminaison après polissage CMP.*

**Figure 23.** Photographie MEB des tranchées des cellules élémentaires après polissage CMP.

Nous avons mesuré, à l'aide d'un microscope à force atomique (AFM), la rugosité de la surface après le dépôt de BCB et le polissage. Nous avons observé une rugosité de l'ordre de 0,3 nm qui reste un bon état de surface pour permettre la

reprise d'étapes de fabrication telles que la croissance d'oxyde ou l'implantation ionique. Notons que la rugosité d'un substrat commercialisé est autour de 0,1 nm.

#### 5.4. Étude du contrôle de la dose de bore diffusée

Le contrôle de la dose de bore diffusée est essentiel pour la réalisation des à Superjonction, comme nous l'avons vu précédemment. composants Malheureusement, les profils simulés de diffusion de bore à travers un oxyde mince ne correspondent pas à la réalité. Nous avons donc réalisé un plan d'expériences pour déterminer l'influence des paramètres technologiques sur la variation de la dose de bore. Ces paramètres technologiques sont au nombre de quatre : l'épaisseur d'oxyde, l'épaisseur de polysilicium, la température de diffusion et le temps de diffusion. Les premières mesures nous ont permis de constater que nous obtenions une meilleure reproductibilité pour de fortes épaisseurs d'oxyde de contrôle et de polysilicium. Nous avons donc fixé l'épaisseur de l'oxyde de contrôle à 20 nm et l'épaisseur du polysilicium à 200 nm. Les premiers résultats sont encourageants mais il reste à vérifier qu'il est possible d'obtenir la dose souhaitée à 2% près avec cette méthode et qu'une parfaite reproductibilité est obtenue sur plusieurs échantillons ; sans cela, la réalisation de composants DT-SJMOS à très faible résistance passante sera compromise.

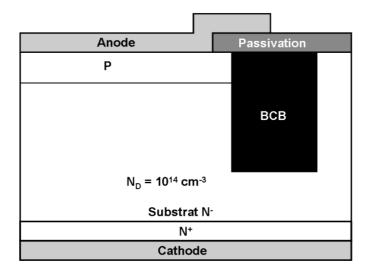

# 5.5. Validation de la terminaison DT<sup>2</sup>

Afin de valider « l'enchaînement » des briques technologiques mais également la terminaison imaginée, il est indispensable de réaliser un dispositif test. Nous avons choisi, dans un premier temps, une diode conventionnelle PN afin de déterminer la performance en tenue en tension de la terminaison.

La diode que nous avons réalisée pour nos tests est présentée en Figure 24. Elle a été fabriquée sur un substrat dopé N dont la concentration est  $10^{14}~\rm cm^{-3}$ : avec cette valeur, la tenue en tension théorique de la jonction plane PN est de 1400 V. Le claquage devrait donc avoir lieu en terminaison puisque les simulations 2D prédisent un claquage à 1290 V. La  $DT^2$  est réalisée avec une tranchée de 100  $\mu$ m de profondeur et de 70  $\mu$ m de large, associée à une plaque de champ de 40  $\mu$ m de longueur.

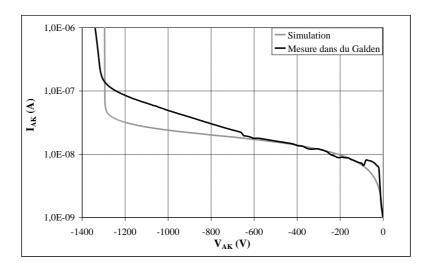

Nous avons effectué les mesures électriques avec une alimentation 10 kV et un microampèremètre Keytlthley dans un bain de diélectrique liquide, le Galden®. La diode supporte alors une tension inverse supérieure à 1300 V (Figure 25).

Figure 24. Coupe schématique de la diode de test.

**Figure 25.** Caractéristiques simulées et mesurées en inverse I(V) de la diode conventionnelle avec la terminaison  $DT^2$ .

Nous pouvons noter la bonne correspondance des tenues en tension et des courants de fuite simulés et mesurés. La concordance des courants de fuite nous rassure sur l'état d'interface entre le silicium et le BCB au niveau de la terminaison. En effet, des charges à l'interface silicium / BCB auraient augmenté le courant de

fuite de façon significative. Nous devons souligner aussi le fait que les mesures présentent une tenue en tension supérieure aux prédictions obtenues en simulation. Ceci est dû à la surgravure latérale de la tranchée de terminaison qui est plus large que prévu (de l'ordre de 5µm) et qui tient donc mieux la tension comme présenté en Figure 16.

## 6. Conclusion et perspectives

Dans cette étude, nous avons proposé une nouvelle structure de transistor MOS de puissance 1200 V, le DT-SJMOS, se basant sur le principe de la Superjonction, réalisée par gravure profonde. Les performances théoriques de cette structure sont comparables à celle d'un IGBT de même tenue en tension. Nous avons étudié la variation de la tenue en tension en fonction de l'erreur de la diffusion de bore, de la largeur des tranchées et de leur verticalité. De plus, cette structure a nécessité une nouvelle terminaison constituée d'une tranchée large et profonde assistée par une plaque de champ (DT<sup>2</sup>). Nous avons partiellement validé le concept de ce transistor par la réalisation expérimentale des étapes critiques et de la terminaison. Le concept de la terminaison DT<sup>2</sup> a également été validé.

Il reste maintenant à réaliser une diode à Superjonction, puis un transistor DT-SJMOS complet.

#### 7. Références

- Fujihira T., « Theory of Semiconductor Superjunction Devices », Japanese Journal of Applied Physics, Vol. 36, pp. 6254-6262, 1997.

- Lärmer F., Schilp A., Patent Nos. DE4241045 (Germany, issued 5 December 1992), US5, 501,983 (U.S., issued 26 March 1996).

- Liang Y. C., «Oxide-Bypassed VDMOS (OBVDMOS): An Alternative to Superjunction High Voltage MOS Power Devices », IEEE Electron Devices Leters, Vol. 22, n°8, pp. 407-409, 2001.

- Lorenz L., Deboy G., Knapp A., März M., « COOLMOS<sup>TM</sup> a new milestone in high voltage power MOSFET », ISPSD'99, pp. 3-10, 1999

- Mahfoz-Kotb H., Theolier Théolier L., Morancho F., Isoird K., Dubreuil P., Do Conto T., « Feasibility study of a junction termination using deep trench isolation technique for the realization of DT-SJMOSFETs », ISPSD'08, pp. 303-306, 2008.

- Morancho F., « De nouvelles limites pour le compromis « Résistance passante spécifique/tenue en tension » des composants unipolaires de puissance », HDR, Université Paul Sabatier, Toulouse, 2004.

- Motto E. R., Donlon J. F., Takahashi H., Tabata M., Iwamoto H., « Characteristics of a 1200V PT IGBT With Trench Gate and Local Life Time Control », IAS Annual Meeting, Vol. 2, pp. 811-816, 1998.

- Sagio M., Fagone D., Musumeci S., « MDmesh<sup>TM</sup>: innovative technology for high voltage PowerMOSFETs », ISPSD'00, pp. 65-68, 2000.

- Saito W., Omura I., Aida S., Koduki S., Izumisawa M., Ogura T., « Semisuperjunction MOSFETs: New Design Concept for Lower On-Resistance and Softer Reverse-Recovery Body Diode », IEEE Transactions on Electron Devices, Vol. 50, n° 8, pp. 1801-1806, 2003.

- Saito W., Omura I., Aida S., Koduki S., Izumisawa M., Yoshioka H., Okumura H., Yamaguchi M., Ogura T.: « A 15.5 mΩcm²-680V Superjunction MOSFET Reduced On-Resistance by Lateral Pitch Narrowing », ISPSD'06, pp. 293-296, 2006.

- Sze S. M., Gibbons G., «Avalanche breakdown voltage of abrupt and linearly graded pn junctions in Ge, Si, GaAs, and GaP », Applied Physics Letters, Vol. 8, 111 p., 1966.

- Théolier L., « Conception de transistors MOS haute tension (1200 Volts) pour l'électronique de puissance », Thèse de l'Université Paul Sabatier, Toulouse, 2008.