# Oscilloscope intégré sur puce appliqué à la caractérisation d'un générateur d'impulsions à 20 GHz

Thomas Epert, Fabrice Caignet, Christophe Viallon, Anqing Wang, Nicolas Mauran, Thierry Parra

#### ▶ To cite this version:

Thomas Epert, Fabrice Caignet, Christophe Viallon, Anqing Wang, Nicolas Mauran, et al.. Oscilloscope intégré sur puce appliqué à la caractérisation d'un générateur d'impulsions à 20 GHz. 18èmes Journées Nationales Microondes, May 2013, Paris, France. pp.4. hal-00924176

HAL Id: hal-00924176

https://hal.science/hal-00924176

Submitted on 6 Jan 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### 18<sup>e</sup> Journées Nationales Microondes 15-16-17 Mai 2013 - Paris

## Oscilloscope intégré sur puce appliqué à la caractérisation d'un générateur d'impulsions à 20 GHz

T. Epert<sup>1,2,3</sup>, F. Caignet<sup>2,3</sup>, C. Viallon<sup>2,3</sup>, A. Wang<sup>2</sup>, N. Mauran<sup>2</sup> et T. Parra<sup>2,3</sup>

<sup>1</sup>Axess Europe; 118 route d'Espagne, 31100 Toulouse <sup>2</sup> LAAS-CNRS; 7 avenue du colonel Roche, 31077 Toulouse

<sup>3</sup> Université de Toulouse ; UPS, INSA, INP, ISAE ; UT1, UTM, LAAS ; F-31077 Toulouse

#### Résumé

Cet article propose l'intégration sur puce d'un oscilloscope qui permet de relever la forme temporelle d'un signal microonde. D'encombrement réduit (340 µm²) et fonctionnant à très haute fréquence, au moyen de sa sonde dont la bande passante est de 72 GHz et la résolution de l'oscilloscope de 4 ps, ce système est utilisé pour caractériser un générateur d'impulsions conçu pour fonctionner jusqu'à 20 GHz.

#### 1. Introduction

Le développement des circuits actifs submicroniques intégrés dans des systèmes de plus en plus complexes s'accompagne d'un besoin croissant en systèmes de test offrant une large bande passante et une précision élevée. Des solutions existent telles que les oscilloscopes hautes fréquences qui outre leurs coûts élevés, disposent d'une sonde haute fréquence dont l'impédance d'entrée est habituellement 50Ω. Cette faible impédance peut altérer le signal observé et ainsi rendre impossible la lecture de la tension de sortie du système. L'intégration sur puce de fonctions dédiées au test présente ainsi un grand intérêt pour la simplification et l'augmentation de la rapidité des procédures (Built-In Test) grâce à l'implémentation simple et faible coût et parce qu'elle permet la caractérisation du circuit en fonctionnement dans son environnement. L'oscilloscope que nous proposons dans cet article se place dans ce contexte. Le système de mesure est présenté en première partie, avec une description des différents blocs constitutifs et des techniques pour son étalonnage. Dans un second paragraphe nous présentons les résultats obtenus lors de la caractérisation d'un générateur d'impulsions concu pour fonctionner jusqu'à 20 GHz.

#### 2. Description du système de mesure

#### 2.a Technique d'échantillonnage blocage

La méthode de mesure est basée sur une technique d'échantillonnage-blocage déjà utilisée depuis quelques années par de nombreux laboratoires [1, 2, 3, 4, 5, 6], mais qui souvent ne donnent que peu de détails sur les circuits qui composent la sonde ainsi que les méthodes d'étalonnage. Cette technique consiste à prélever successivement

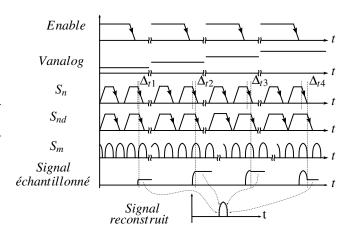

des échantillons de tension décalés dans le temps les uns par rapport aux autres. Chaque échantillon est momentanément stocké par plusieurs capacités le temps d'être numériser par une carte d'acquisition pilotée par un PC. Les échantillons sont recalés dans le temps pour reconstituer le signal original observé (figure 1).

FIGURE 1 – Reconstruction du signal échantillonné.

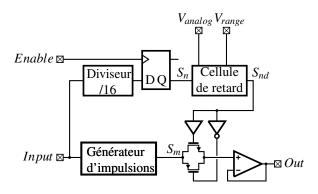

FIGURE 2 – Diagramme fonctionnel de la technique d'échantillonnage.

La figure 2 présente les différents blocs intégrés dans la puce. Lorsque la carte d'acquisition est prête, celle-ci bascule l'état de l'entrée «Enable» à 1. L'acquisition est

déclenchée par la bascule D  $(S_n(t))$  de manière synchrone avec le signal à capturer  $S_m(t)$ . Un délai supplémentaire ajustable et parfaitement contrôlé est introduit à l'aide de la cellule de retard du système  $(S_{nd}(t))$  de manière à capturer progressivement plusieurs périodes du signal à observer. Le signal  $S_{nd}(t)$  commande la cellule d'échantillonnage qui prend la forme d'un intérrupteur à transistors MOS décrit plus bas. Lorsque l'entrée «Enable» est remise à l'état bas,  $S_{nd}(t)$  s'annule, la cellule d'échantillonnage bascule dans un état haute impédance et l'échantillon est bloqué en sortie de l'amplificateur (out) le temps de l'acquisition par la carte externe. Un autre amplificateur câblé en suiveur est disposé en dehors de la puce pour augmenter la durée pendant laquelle l'échantillon est maintenu en vu de sa numérisation.

#### 2.b Contrôle du retard d'échantillonnage

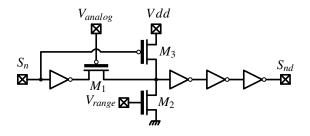

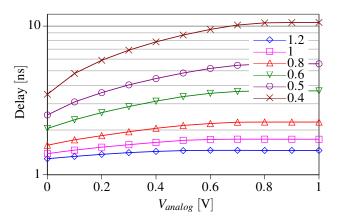

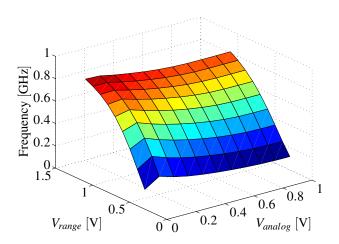

Le retard introduit par cette cellule est contrôlée par deux tensions analogiques  $V_{range}$ , et  $V_{analog}$  appliquées respectivement sur les grilles des transistors M1 (PMOS) et M2 (NMOS) (figure 3). La croissance de  $V_{analog}$  a pour effet d'augmenter le retard introduit. La tension  $V_{range}$  modifie l'échelle de temps. Par exemple pour  $V_{range} = 1.2 \, \text{V}$ , on obtient une résolution minimale de 4 ps (figure 4).

FIGURE 3 – Diagramme de la cellule de retard.

FIGURE 4 – Mesure de la variation du délai en fonction des tensions  $V_{range}$  et  $V_{analog}$ .

La plus grande fenêtre de temps observable est de 50 ns correspondant à  $V_{range} = 0.3 \text{ V}$ , ce qui est proche de la tension de pincement du MOS. Le signal issu de cette cellule, commande la sonde présentée dans le paragraphe suivant.

#### 2.c Sonde de tension hyperfréquence

Cette sonde est constituée d'une porte de transmission conçue à l'aide de deux transistors MOS complémentaires suivie d'un amplificateur opérationnel (AOP) monté en suiveur (figure 2). Compte tenu de la fréquence fondamentale élevée (20 GHz) du signal que l'on cherhce à observer, il convient de réduire la capacité d'entrée de cette sonde ainsi que la résistance de canal des transistors MOS afin de maximiser la bande passante et de minimiser les pertes de transmission. La meilleure performance fréquentielle est obtenue pour 8 portes en parallèle. Cette configuration permet d'atteindre une bande passante simulée de 72 GHz.

FIGURE 5 – Dessin des masques de l'échantillonneur.

Le dessin des masques (figure 5) est réalisé de manière symétrique selon un axe vertical mais aussi horizontal afin d'assurer un parfait équilibre sur la structure pour conserver les bienfaits de la mise en parallèle des portes de transmission.

#### 2.d Structures de calibrage

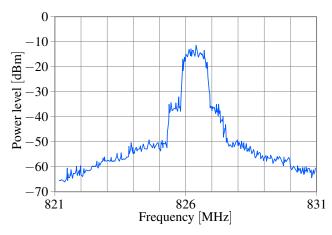

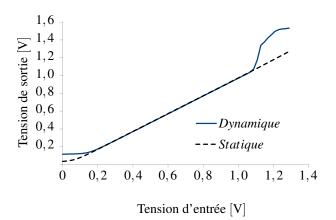

Pour être fonctionnel, le système intégré sur puce doit être étalonner, le retard exact introduit par la cellule de délai ainsi que les décalages de tension introduits par l'amplificateur suiveur et de la porte de transmission sonde doit être déterminé. Pour caractériser la cellule de retard, nous l'avons intégrés dans un oscillateur en anneaux dotés de 15 inverseurs MOS. Les tensions analogiques  $V_{range}$  et  $V_{analog}$ permettent de faire varier la fréquence de cet oscillateur (figure 6) à partir de laquelle les retards sont déduits. Cette technique est simple et précise compte tenu de la faible gigue de l'oscillateur, environ 1 MHz ce qui correspond à une incertitude de 1 ps sur la résolution de 4 ps de l'oscilloscope déjà mentionnée au-dessus (figure 7). Les décalages en tension introduits par le système de mesure peuvent être de deux natures différentes : statique et dynamique. Ces deux décalages sont déterminés grâce à un motif de test implémenté dans la puce comprenant une porte de transmission avec son inverseur et l'amplificateur à gain unitaire. Pour déterminer les déclages statiques engendrés par le

système plusieurs tensions DC sont appliquées successivement en entrée de la sonde sur toute une plage de valeurs prédéterminées. La tension présente en sortie pour chaque valeurs est mesurée ce qui permettra par la suite de corriger automatiquement les écantillons recueillis par le système de mesure. Pour déterminer les décalages dynamiques, on procède de la même manière que précedemment mais cette fois-ci la porte de transmission est ici activée pour chaque échantillon (figure 8). Cette étape permet d'évaluer les effets dynamiques liés à la porte de transmission (injection de charge, fuites d'horloge, etc...) [7].

FIGURE 6 – Calibrage de l'oscillateur en anneaux programmable.

FIGURE 7 – Mesure du spectre de sortie du VCO pour  $V_{range}(max) = 1.2 \, \mathrm{V}$  et  $V_{analog}(min) = 0 \, \mathrm{V}$ .

FIGURE 8 – Etalonnage statique et dynamique du transfert de l'ensemble "porte de transmission + Amplificateur suiveur".

## 3. Caractérisation du générateur d'impulsions

Le système a été intégré dans une technologie BiCMOS SiGe 130 nm.

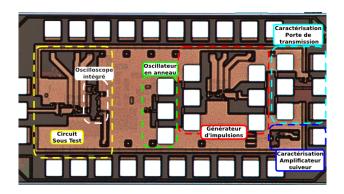

FIGURE 9 - Microphotographie de la puce.

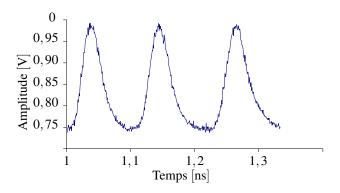

Le système de mesure occupe une surface de  $340 \mu m^2$ (zone repérée en blanc sur la figure 9). La consommation globale est de 90mW décomposée en 25 mW, 40 mW et 24 mW respectivement pour le générateur d'impulsion, le système de mesure et les cellules de calibrage. le graphe de la figure 10 présente le résultat de la caractérisation du générateur d'impulsions lorque celui-ci fonctionne à 10GHz, l'amplitude du signal est alors de 250mV. Il s'agit là de la limite basse d'amplitude par rapport aux objectifs que nous nous sommes fixés relativement à l'utilisation de ce circuit [8]. A 20GHz l'oscilloscope intégré met en évidence une amplitude inférieure avec un rapport cyclique dégradé. Ce résultat nous a permis d'identifier que ce générateur d'impulsions était trop sensible aux variations technologiques du procédé. Une autre conception corrigeant ces problèmes a depuis été réalisée et est présentée en [8].

FIGURE 10 - Mesure des impulsions à 10 GHz.

#### 4. Conclusion

Cet article présente l'intégration sur puce d'un oscilloscope. L'ensemble de la méthode de conception est développée ainsi que la procédure d'étalonnage. Le système est utilisé pour relever la forme temporelle de la tension de sortie d'un générateur d'impulsions. Le bon fonctionnement de l'ensemble du système de mesure a permis de valider la méthode de conception du générateur d'impulsions qui fonctionne comme attendu jusqu'à environ 10GHz. Ce travail nous a également permis de mettre en évidence la forte sensibilité de ce générateur d'impulsions par rapport aux variations du procédé technologique ce qui se traduit par une limite haute de la fréquence de fonctionnement inférieure à ce qui était attendue.

Les performances à hautes fréquences et le faible encombrement de ce système de mesure lui confèrent un grand intérêt pour le "Built-In Test".

#### Références

- [1] F. Caignet, S. Dhia, and E. Sicard, "On the measurement of crosstalk in integrated circuits," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 8, no. 5, pp. 606–609, Oct. 2000.

- [2] F. Caignet, S. Delmas-Bendhia, and E. Sicard, "The challenge of signal integrity in deep-submicrometer CMOS technology," *Proceedings of the IEEE*, vol. 89, no. 4, pp. 556 –573, Apr. 2001.

- [3] B. Vrignon and S. Dhia, "On-chip sampling sensors for high frequency signals measurement: evolution and improvements," in *Proceedings of the Fifth IEEE International Caracas Conference on Devices, Circuits and Systems*, 2004, vol. 1, Nov. 2004, pp. 270 275.

- [4] K. Inagaki, D. Antono, M. Takamiya, S. Kumashiro, and T. Sakurai, "A 1-ps resolution on-chip sampling oscilloscope with 64:1 tunable sampling range based on ramp waveform division scheme," in 2006 Symposium on VLSI Circuits, 2006. Digest of Technical Papers, 2006, pp. 61–62.

- [5] M. Safi-Harb and G. Roberts, "70-GHz effective sampling time-base on-chip oscilloscope in CMOS," *IEEE Journal of Solid-State Circuits*, vol. 42, no. 8, pp. 1743 –1757, Aug. 2007.

- [6] P. Milosevic and J. Schutt-Aine, "On-chip oscilloscope for signal integrity characterization of interconnects in 130nm CMOS technology," in *Electrical Performance* of *Electronic Packaging*, 2008 IEEE-EPEP, Oct. 2008, pp. 65 –68.

- [7] B. Razavi, *Design of Analog CMOS Integrated*. McGraw-Hill Companies, 2003.

- [8] A. Magnani, Convertisseur de fréquences BiCMOS en bande K basé sur un mélange passif à faibles pertes. Journées Nationales Microondes, 2013.