# Stable microcrystalline silicon thin-film transistors produced by the layer-by-layer technique

Pere Roca I Cabarrocas, Romain Brenot, Pavel Bulkin, Regis Vanderhaghen, Bernard Drévillon, Ian French

### ▶ To cite this version:

Pere Roca I Cabarrocas, Romain Brenot, Pavel Bulkin, Regis Vanderhaghen, Bernard Drévillon, et al.. Stable microcrystalline silicon thin-film transistors produced by the layer-by-layer technique. Journal of Applied Physics, 1999, 86 (12), pp.7079-7082. 10.1063/1.371795. hal-00905877

HAL Id: hal-00905877

https://hal.science/hal-00905877

Submitted on 18 Nov 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Stable microcrystalline silicon thin-film transistors produced by the layer-by-layer technique

P. Roca i Cabarrocas, R. Brenot, P. Bulkin, R. Vanderhaghen, B. Drévillon, and I. French

Citation: Journal of Applied Physics 86, 7079 (1999); doi: 10.1063/1.371795

View online: http://dx.doi.org/10.1063/1.371795

View Table of Contents: http://scitation.aip.org/content/aip/journal/jap/86/12?ver=pdfcov

Published by the AIP Publishing

## Re-register for Table of Content Alerts

Create a profile.

Sign up today!

JOURNAL OF APPLIED PHYSICS VOLUME 86, NUMBER 12 15 DECEMBER 1999

### Stable microcrystalline silicon thin-film transistors produced by the layer-by-layer technique

P. Roca i Cabarrocas, <sup>a)</sup> R. Brenot, P. Bulkin, R. Vanderhaghen, and B. Drévillon *Laboratoire de Physique des Interfaces et des Couches Minces (UMR 7647 CNRS), Ecole Polytechnique, 91128 Palaiseau Cedex, France*

#### I. French

Thin Film Electronics Group, Philips Research Laboratories, Cross Oak Lane, Redhill, Surrey, RH1 5HA, England, United Kingdom

(Received 24 May 1999; accepted for publication 14 September 1999)

Microcrystalline silicon thin films prepared by the layer-by-layer technique in a standard radio-frequency glow discharge reactor were used as the active layer of top-gate thin-film transistors (TFTs). Crystalline fractions above 90% were achieved for silicon films as thin as 40 nm and resulted in TFTs with smaller threshold voltages than amorphous silicon TFTs, but similar field effect mobilities of around  $0.6 \text{ cm}^2/\text{V}$  s. The most striking property of these microcrystalline silicon transistors was their high electrical stability when submitted to bias-stress tests. We suggest that the excellent stability of these TFTs, prepared in a conventional plasma reactor, is due to the stability of the  $\mu c$ -Si:H films. These TFTs can be used in applications that require high stability for which a-Si:H TFTs cannot be used, such as multiplexed row and column drivers in flat-panel display applications, and active matrix addressing of polymer light-emitting diodes. © 1999 American Institute of Physics. [S0021-8979(99)05324-4]

#### I. INTRODUCTION

Active matrix liquid crystal displays (LCD) in which each pixel is addressed by an a-Si:H based thin-film transistor (TFT) are the base of a mature industry, 1,2 in spite of hydrogenated amorphous silicon (a-Si:H) TFTs having low mobility and poor threshold voltage stability. This can be due to the metastability of a-Si:H films or to a carrier trapping in the insulator.<sup>3,4</sup> Polycrystalline silicon films produced by thermal or laser annealing of a-Si:H have resulted in highly stable thin-film transistors with mobilities above 100 cm<sup>2</sup>/V s,<sup>5,6</sup> that can be used for both multiplexing the LCD and making drive circuits. However, thermal annealing requires quartz substrates and is not suitable for large area displays. Laser annealed polycrystalline silicon TFTs require complex processing, and there remain problems with the stability and large area uniformity of the laser annealing process. For manufacturing, it would be more attractive if displays incorporating integrated drive circuits could be made by the simpler a-Si:H TFT fabrication process, but with some process steps modified to give superior devices.<sup>5</sup> The highest level of driver circuit intergration, which requires the lowest number of interconnects and external drivers, requires high stability and high mobility TFTs. However, multiplexed row and column drivers, which reduce the number of interconnects, can still be made with low mobility TFTs. 7,8 The high duty ratio (ON time/OFF time) of some of the transistors in drive circuits means that high mobility TFTs with the poor stability of a-Si:H TFTs would result in drive circuits with an unacceptably short lifetime. In addition, TFTs for active matrix addressing of organic and polymer light-

Compared to a-Si:H,  $\mu c$ -Si:H films should result in thin-film transistors with higher field effect mobility and improved stability. Indeed, microcrystalline silicon ( $\mu c$ -Si:H) thin films produced at low temperatures by PECVD have been largely studied for their application to thin-film transistors.9-11 However, very few publications report on  $\mu c$ -Si TFT mobilities higher than those of a-Si:H TFTs. <sup>12,13</sup> In most cases, the mobility is smaller, and no information is provided on the stability of the devices. Although the smaller grain size in  $\mu c$ -Si:H films produced by PECVD, with respect to laser crystallized ones, can partly explain the smaller mobility, other factors like grain boundary passivation and the quality of the crystallites in the channel region may have more of an effect on the field effect mobility. The production  $^{14}$  of  $\mu c$ -Si:H films from SiF<sub>4</sub> precursors with mobilities above 30 cm<sup>2</sup>/V s and thin-film transistors<sup>12</sup> with mobilities up to 40 cm<sup>2</sup>/V s confirms that low temperature deposited  $\mu c$ -Si:H films are a serious alternative to higher temperature processes such as solid phase crystallization and laser annealing. Moreover, it has been shown that  $\mu c$ -Si:H films with crystalline fractions above 60% are stable 15 and that they result in stable solar cells.<sup>16</sup>

Here we report on the production of stable  $\mu c$ -Si:H TFTs in a standard radio-frequency glow discharge reactor.

emitting diodes (LEDs) must also have high stability. For this reason, we have investigated the properties of TFTs made by a standard a-Si:H top-gate TFT process, but with the a-Si:H layer replaced by microcrystalline ( $\mu c$ -Si:H) films directly deposited by plasma enhanced chemical vapor deposition (PECVD) at low temperature, with particular emphasis being placed on device stability.

<sup>&</sup>lt;sup>a)</sup>Electronic mail: roca@poly.polytechnique.fr

#### **II. EXPERIMENTS**

Top-gate transistors were prepared as follows. Indium tin oxyde (ITO) on glass was patterned to form source and drain contacts. In a multichamber PECVD system, the substrates were exposed to a PH<sub>3</sub> plasma, followed by the deposition of a 20-nm-thick a-Si:H layer. It has been shown that this forms doped a-Si:H layers in contact with the ITO.  $^{17}$ After an HF dip to remove the native oxide, the substrates were loaded into a multiplasma-monochamber reactor<sup>18</sup> for the deposition of the  $\mu c$ -Si:H layer and a 80-nm-thick a-SiN:H layer at 250 °C. Silicon nitride films were produced at 40 Pa from the decomposition of a gas mixture consisting of 2 sccm of silane, 100 sccm of NH<sub>3</sub>, and 100 sccm of hydrogen under an rf power of 60 mW/cm<sup>2</sup> resulting in a deposition rate of 1 Å/s and a material with an optical gap  $E_{o4}$  of 5.5 eV. In some cases, SiO<sub>2</sub> films deposited at 250 °C in a IDECR reactor 19 were used as an alternative dielectric

Microcrystalline silicon films were produced by the layer-by-layer technique,<sup>20</sup> in which the deposition of a thin a-Si:H film is followed by its exposure to an hydrogen plasma, and this sequence is repeated until the desired thickness is achieved. The deposition and hydrogen exposure times were fixed at 20 and 30 s, respectively. Because of the hydrogen plasma treatment, the porosity of the a-Si:H film increases during the first LBL cycles. In subsequent silane/ hydrogen cycles, the nucleation of crystallites takes place; the crystalline fraction increases while the amorphous phase and porosity decrease until a steady state growth is reached. After this the crystalline fraction remains constant<sup>21</sup> but the transport properties improve with film thickness.<sup>14</sup> The a-Si:H deposition was carried out from a 50% silane in hydrogen mixture at 10 mW/cm<sup>2</sup>, whereas the hydrogen plasma exposure was performed at 100 mW/cm<sup>2</sup>. The process pressure was kept constant at 40 Pa. Under these conditions, the effective deposition rate was 0.15 Å/s. This deposition rate can be increased up to 1 Å/s by an appropriate choice of the plasma conditions. 22 In principle, all of the plasma processes could have been carried out in a single PECVD system, but at the moment, we have different processes optimized in different deposition systems.

After  $\mu c$ -Si:H and a-SiN:H or SiO<sub>2</sub> deposition, the samples were processed into standard top-gate TFT structures, which included a second a-SiN:H deposition to make a total gate dielectric thickness of 330 nm.

Top-gate TFTs were chosen in preference to bottom-gate TFTs because the channel is formed on top of the microcrystalline silicon where the growth process has stabilized, rather than at the bottom surface where the nucleation takes place. We expect the top surface to have better material properties and to be more reproducible. The TFT measurements reported here were made on long channel TFTs ( $w = 1000 \, \mu \text{m}$  and  $L = 100 \, \mu \text{m}$ ), to avoid contact limitations. Annealing the TFTs for 1 h at 200 °C resulted in a 10%–20% increase of their mobility, and a decrease of their threshold voltage. The transfer characteristics were measured at 30 °C on annealed TFTs with source-drain voltages of 0.25 V (linear regime) and 20 V (saturation regime). Stress

FIG. 1. Spectroscopic ellipsometry measurements performed on (i) a  $\mu c$ -Si:H film obtained after 80 LBL cycles on a Corning glass (full circles); (ii) the same film deposited on a crystalline silicon substrate coated with 50-nm-thick a-Si:H film (open circles); and (iii) a  $\mu c$ -Si:H film obtained after 60 LBL cycles on a Corning glass (open triangles). The three films were produced at 250 °C.

tests were performed under a gate voltage of 30 V and a substrate temperature of 60 °C.

#### III. RESULTS AND DISCUSSION

Figure 1 shows the result of spectroscopic ellipsometry measurements performed on samples codeposited with the TFT structures, without the a-SiN:H layer. Full circles represent the imaginary part of the pseudo-dielectric function  $(\langle \epsilon_2 \rangle)$  of a  $\mu c$ -Si:H film obtained after 80 LBL cycles directly on Corning glass (Cg), while open circles show the spectrum of a film deposited in the same run but on a crystalline silicon substrate coated with 50-nm-thick a-Si:H layer, in order to reproduce the conditions used for the TFTs fabrication. Apart from the differences in the low energy part of the spectra (interference fringes with different substrates), one can see that the amplitude of  $\text{Im}(\langle \epsilon_2 \rangle)$  of the  $\mu c$ -Si:H film deposited on a-Si:H is smaller than that of the film directly deposited on glass. Indeed, the growth of  $\mu c$ -Si:H on a-Si:H strongly depends on the quality of the a-Si:H layer<sup>23</sup> and may result in  $\mu c$ -Si:H films with higher surface roughness. The analysis of the spectra presented in Fig. 1, with Bruggeman effective medium approximation, 21 shows

TABLE I. Thickness and composition of the microcrystalline silicon films deduced from the analysis of the spectroscopic data shown in Fig. 1. N is the number of cycles used in the deposition of the  $\mu c$ -Si:H layer, d the layer thickness,  $F_c$  the crystalline fraction and  $F_a$  the amorphous fraction. The complement to 100% corresponds to the fraction of voids.

|             |    | Sur  | face roug | hness     | Bulk |           |                           |

|-------------|----|------|-----------|-----------|------|-----------|---------------------------|

| Sample      | N  | d(Å) | $F_c(\%)$ | $F_a(\%)$ | d(Å) | $F_c(\%)$ | <i>F</i> <sub>a</sub> (%) |

| EP20/Cg     | 80 | 36   | 48        | 8         | 564  | 87        | 6                         |

| EP20/a-Si:H | 80 | 82   | 46        | 20        | 413  | 98        | 0                         |

| EP16/Cg     | 60 | 53   | 49        | 13        | 208  | 86        | 11                        |

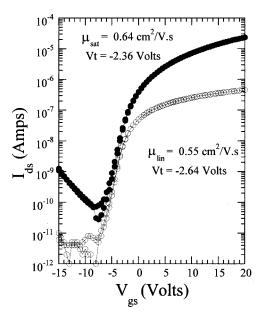

FIG. 2. Transfer characteristics of a  $\mu c$ -Si:H TFT measured in the linear regime ( $V_{\rm DS}$ =0.25 V) and in the saturated regime ( $V_{\rm DS}$ =20). The threshold voltage and effective field effect mobility are also shown.

that the surface layer is more amorphous in the case of deposition on a-Si:H (see Table I). The higher amorphous fraction and roughness of the film in the channel region of the TFT can be of crucial importance for the TFT characteristics. In the case of the film on glass after 60 cycles (open triangles), we obtain a higher void fraction in the bulk and the higher amorphous fraction in the surface layer region, as expected in a film for which a steady-state growth has not been achieved. Then, TFTs produced at N=60 have  $\mu c$ -Si:H films deposited during the evolutionary phase of LBL growth, where the film porosity decreases and its crystalline fraction increases, and N=80 corresponds to the steady-state growth with maximum crystalline fraction.  $^{20}$

Figure 2 shows the transfer characteristics of top-gate TFT EP20 measured with a gate voltage swept from -15 to +20 V. In the linear regime, the source-drain voltage was 0.25 V, and 20 V in the saturated regime. The values of the field effect mobility and threshold voltage in each regime are also shown in the figure. Despite the high crystalline fractions (see Table I), mobility values are typical of a-Si:H TFTs. However, the threshold voltage and the OFF current

TABLE II. Summary of the microcrystalline TFT characteristics. The mobility and threshold voltage are those measured in the saturated regime. The leakage current was measured under a gate voltage of -15 V and a source-to-drain voltage of 20 V.  $\Delta V_T$  is the shift in the threshold voltage measured after 1000 s stress with a gate voltage of 30 V and a substrate temperature of 60 °C. The  $I_{\rm ON}/I_{\rm OFF}$  ratio has been measured at +15/-15 V and a source-to-drain voltage of 0.25 V. Only EP20 has SiO<sub>2</sub> as a dielectric layer.

| Sample | N  | $\mu$ (cm <sup>2</sup> /V s) | V <sub>T</sub> (V) | I <sub>OFF</sub> (A) | $I_{ m ON}/I_{ m OFF}$ | $\frac{\Delta V_T}{({ m V})}$ |

|--------|----|------------------------------|--------------------|----------------------|------------------------|-------------------------------|

| EP6    | 80 | 0.60                         | -0.4               | $9.10^{-8}$          | $4.10^{4}$             | 0.64                          |

| EP21   | 80 | 0.54                         | -1.2               | $2.10^{-9}$          | $1.10^{4}$             | 0.62                          |

| EP17   | 60 | 0.49                         | 1.3                | $3.10^{-9}$          | $3.10^4$               | 0.87                          |

| EP20   | 80 | 0.64                         | -2.4               | $1.10^{-9}$          | $5.10^4$               | -0.18                         |

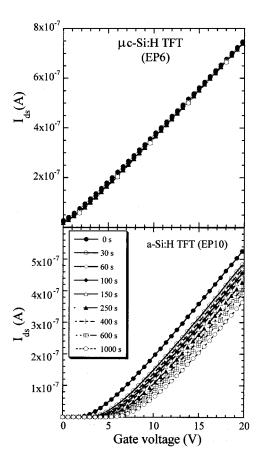

FIG. 3. Linear transfer characteristics taken during threshold voltage shift measurements on a  $\mu c$ -Si:H TFT (EP6) and on a standard a-Si:H TFT (EP10).

are respectively smaller and higher than those of a-Si:H TFTs, as expected for  $\mu c$ -Si:H TFTs. Table II summarizes some properties of  $\mu c$ -Si:H TFTs. EP6 and EP21 where nominally made with the same process, but produced and measured at a six month interval. We can see that there is a good reproducibility of the characteristics, which is further supported by the stability tests. We attribute the factor of 50 lower value of the OFF current in sample EP21 to a better process in the formation of the ohmic contact between the ITO source/drain contacts and the a-Si:H layer. TFT EP17, with a thinner  $\mu c$ -Si:H layer (N = 60 as for EP16) had a somewhat lower field effect mobility and higher threshold voltage, suggesting a less crystallized channel region, in agreement with the spectroscopic ellipsometry results (Table I). Finally, sample EP20, with a SiO<sub>2</sub> dielectric layer shows mobility and OFF-current values comparable to those of TFT EP21 deposited under the same conditions, but with a-SiN:H as the dielectric layer. However, the negative threshold voltage shift of only 0.18 V indicates that SiO<sub>2</sub> gives more stable results than a-SiN:H. Let us now focus on the stability of these  $\mu c$ -Si:H TFTs.

Figure 3 shows the linear transfer characteristics taken during threshold voltage shift measurements on a  $\mu c$ -Si:H (EP6) and a standard a-Si:H (EP10) top-gate TFTs. The characteristics are recorded at different stressing times (0, 30, 60, 100, 150, 250, 400, 600, and 1000 s). Compared to the standard a-Si:H TFTs, the stability of the  $\mu c$ -Si:H TFT is

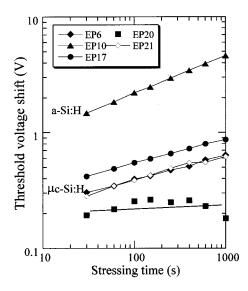

FIG. 4. Threshold voltage shifts as functions of stressing time at 60 °C under a gate voltage of 30 V. Note the small shift for the  $\mu c$ -Si:H TFTs, especially when compared to the a-Si:H TFT and the excellent stability of TFT EP20 in which SiO $_2$  was used as a gate dielectric. The lines are provided as guides to the eye.

remarkable and comparable to that of a-Si:H TFT prepared by hot wire chemical vapor deposition. The stability of these  $\mu c$ -Si:H TFTs is also demonstrated in Fig. 4, where we plot the threshold voltage shift as a function of the stressing time for four  $\mu c$ -Si:H TFTs and a standard a-Si:H TFT of comparable mobility. Clearly, all  $\mu c$ -Si:H TFTs show smaller threshold voltage shifts than the a-Si:H TFT. One can notice again the excellent reproducibility of the results (EP6 versus EP21) and a slightly higher shift for the TFT with the thinner and less crystallized surface layer (EP17). Finally, TFT EP20 with SiO<sub>2</sub> as a dielectric layer shows almost no threshold voltage shift.

We attribute the stability of these  $\mu c$ -Si:H TFTs to the high crystalline fraction achieved in the layer-by-layer technique even for very thin  $\mu c$ -Si:H layers. Indeed, stability studies performed on  $\mu c$ -Si:H layers have shown that films with crystalline fractions above 60% are stable. <sup>15</sup> All of the microcrystalline TFTs had much better stability than amorphous silicon TFTs, such as EP10. Also samples EP6 and EP21 had a higher crystalline fraction than EP17 (Table I), and they also had a better  $V_T$  stability. These results indicate that the stability of  $\mu c$ -Si:H films is the main reason for the stable TFTs. Nevertheless, the improved stability for TFT EP20 with an SiO<sub>2</sub> dielectric layer suggests that the insulator does have a secondary effect.

#### **IV. CONCLUSIONS**

As a conclusion, we have shown that stable microcrystalline silicon thin-film transistors with mobilities similar to those of *a*-Si:H TFTs can be produced by the standard rf glow discharge technique. While further work is necessary to increase their field effect mobility, the remarkable stability of these transistors will favor their use as driver circuits directly incorporated onto flat-panel displays, and other applications that require high stability devices.

#### **ACKNOWLEDGMENTS**

The authors would like to express their gratitude to Jeff Chapman and Denise Theobald of PRL for device fabrication.

- <sup>1</sup>R. A. Street, Phys. Status Solidi A 166, 695 (1998).

- <sup>2</sup>T. Sameshima, J. Non-Cryst. Solids 227-230, 1196 (1998).

- <sup>3</sup>M. J. Powell, C. v. Berkel, and J. R. Hughes, Appl. Phys. Lett. **54**, 1323 (1989).

- <sup>4</sup>J. Kanicki, C. Godet, and A. V. Gelatos, Mater. Res. Soc. Symp. Proc. **219**, 45 (1991).

- <sup>5</sup>S. D. Brotherton, Semicond. Sci. Technol. 10, 721 (1995).

- <sup>6</sup>J. B. Boyce, P. Mei, R. T. Fulks, and J. Ho, Phys. Status Solidi A **166**, 729 (1998).

- <sup>7</sup>H. Lebrun, F. Maurice, J. Margarino, and N. Szydio, SID 95 Digest, 403 (1995).

- <sup>8</sup>R. I. Hornsey, T. Mahnke, P. Madeira, K. Aflatooni, and A. Nathan, Mater. Res. Soc. Symp. Proc. 467, 887 (1997).

- <sup>9</sup>S. D. Brotherthon, J. R. Ayres, and N. D. Young, Solid-State Electron. 34, 671 (1991).

- <sup>10</sup>C. Liang, W. Chiang, and M. Feng, Jpn. J. Appl. Phys., Part 1 34, 5943 (1995).

- <sup>11</sup> K. Hsu, B. Chen, H. Hsu, K. Wang, T. Yew, and H. Hwang, Jpn. J. Appl. Phys., Part 1 33, 639 (1994).

- <sup>12</sup> N. Kono, T. Nagahara, K. Fujimoto, Y. Kashiwagi, and H. Kakinoki, Mater. Res. Soc. Symp. Proc. 283, 629 (1993).

- <sup>13</sup> A. H. Jayatissa, Y. Hatanaka, Y. Nakanishi, and T. Yamaguchi, Jpn. J. Appl. Phys., Part 1 35, 5687 (1996).

- <sup>14</sup>R. Brenot, R. Vanderhaghen, B. Drévillon, and P. Roca i Cabarrocas, Appl. Phys. Lett. **74**, 58 (1999).

- 15 P. St'ahel, S. Hamma, P. Sladek, and P. Roca i Cabarrocas, J. Non-Cryst. Solids 227–230, 276 (1998).

- <sup>16</sup>J. Meier, R. Flückiger, H. Kepner, and A. Shah, Appl. Phys. Lett. **65**, 860 (1994)

- <sup>17</sup> Y. Ugai, T. Yukawa, K. Amano, and S. Aoki, Jpn. J. Appl. Phys., Part 1 37, 3226 (1998).

- <sup>18</sup>P. Roca i Cabarrocas, J. B. Chévrier, J. Huc, A. Lloret, J. Y. Parey, and J. P. M. Schmitt, J. Vac. Sci. Technol. A 9, 2331 (1991).

- <sup>19</sup>P. Bulkin, N. Bertrand, B. Drévillon, J. C. Rostaing, F. Delmotte, M. C. Hugon, and B. Agius, Thin Solid Films 308–309, 63 (1997).

- <sup>20</sup>S. Hamma and P. Roca i Cabarrocas, J. Appl. Phys. **81**, 7282 (1997).

- <sup>21</sup> P. Roca i Cabarrocas, S. Hamma, A. Hadjadj, J. Bertomeu, and J. Andreu, Appl. Phys. Lett. **69**, 529 (1996).

- <sup>22</sup>S. Hamma, D. Colliquet, and P. Roca i Cabarrocas, Mater. Res. Soc. Symp. Proc. 507, 505 (1998).

- <sup>23</sup>S. Hamma and P. Roca i Cabarrocas, Thin Solid Films **296**, 11 (1997).

- <sup>24</sup>H. Meiling and R. E. I. Schropp, Appl. Phys. Lett. **70**, 2681 (1997).