# Analysis of the SiC VJFET gate punch-through and its dependence with the temperature

Fabien Dubois, Dominique Bergogne, Dominique Tournier, Cyril Buttay, Régis Meuret, Hervé Morel

## ▶ To cite this version:

Fabien Dubois, Dominique Bergogne, Dominique Tournier, Cyril Buttay, Régis Meuret, et al.. Analysis of the SiC VJFET gate punch-through and its dependence with the temperature. EPE, Sep 2013, Lille, France. Paper 344, 10.1109/EPE.2013.6631963. hal-00874655

HAL Id: hal-00874655

https://hal.science/hal-00874655

Submitted on 18 Oct 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Analysis of the SiC VJFET gate punch-through and its dependence with the temperature

Fabien Dubois<sup>1,2,3</sup>, Dominique Bergogne<sup>2</sup>, Dominique Tournier<sup>1</sup>,

Cyril Buttay<sup>1</sup>, Régis Meuret<sup>3</sup> and Hervé Morel<sup>1</sup>

<sup>1</sup> Université de Lyon, INSA-Lyon, Lab. Ampère, F-69621, France,

<sup>2</sup> Université de Lyon, Université Lyon 1, Lab. Ampère, F-69621, France,

<sup>3</sup> Hispano-Suiza, Safran Group, Réau, France

Tel.: +33 / (0) – 472.43.87.24 Fax: +33 / (0) – 472.43.85.30 E-Mail: Herve.Morel@insa-lyon.fr URL: http://ampere-lab.fr

## **Keywords**

«Silicon Carbide (SiC)», «JFET», «Device characterisation», «Device modeling», «High temperature electronics».

## **Abstract**

Turning off a SiC VJFET from INFINEON requires to apply a gate-to-source voltage comprised between the JFET gate threshold voltage and the punch-through voltage. Unfortunately, for applications operating over a large temperature range, these two limits vary with the temperature and reduce the useful blocking gate-to-source voltage range as the temperature rises. So, the punch-through temperature dependence is a very important feature for applications operating in a wide temperature range like aeronautic applications. This paper addresses the analysis and modeling of the punch-through phenomenon and its dependence to the temperature. The proposed model gives a good agreement with the experimental data.

## Introduction

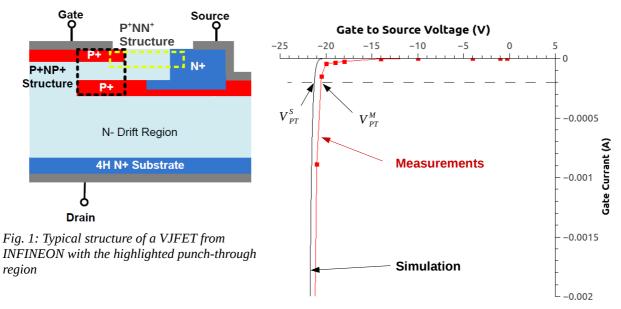

On a vertical SiC-JFET like those of INFINEON, there is a N-type lateral channel with two P-layers connected to the source and the gate terminals respectively. Because of the difference in potentials between the two P-regions of a PNP structure (Fig. 1), the punch-through phenomenon may occur. When this happens, the gate current dramatically increases.

The punch-through phenomenon was firstly described in bipolar junction transistors [1]. It occurs when the two space-charge regions of a PNP structure join. Holes may then diffuse from one P-layer to the other one.

Punch-through can also be observed in PIN diodes, when the space-charge region spreads all over the low-doped base [1]. This corresponds to a PNN<sup>+</sup> structure, so there is no current increase, but an electric field rise. Therefore, this is a very different phenomena, even though it has the same name.

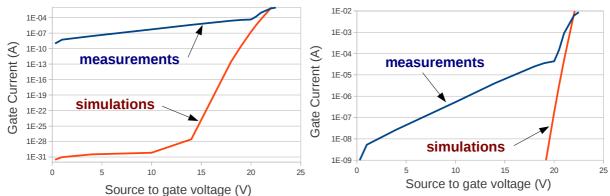

The devices under test (DUTs) investigated here are  $100 \text{ m}\Omega$ , 1200 V VJFETs from SiCED which is the company which developed the VJFET for INFINEON. In such a VJFET, the punch-through occurrence defines the practical gate-to-source voltage limit (Fig. 2), i.e. when the hole current starts to flow in the PNP structure,  $V_{PT}$  as shown in Fig. 2. This was described in [2].

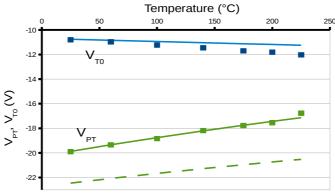

Fig. 3 shows the measurement of the threshold voltage,  $V_{T0}$ , and the punch-trough voltage,  $V_{PT}$ , versus the temperature. The threshold voltage,  $V_{T0}$ , is classically defined from the saturation current characteristics,  $i_D^{SAT} \left( V_{GS} \right)$  [3]. A quadratic fitting of the characteristics around zero current is useful to improve the accuracy of  $V_{T0}$  extraction.

$$i_{D}^{SAT}(V_{TO})=0 \tag{1}$$

The punch-trough voltage,  $V_{PT}$ , is defined from the characteristic in Fig. 2. The punch-through reference current is arbitrarily defined as in [4],

$$i_{pT}^{REF} = 200 \,\mu\text{A}$$

(2)

And the punch-trough voltage,  $V_{\text{PT}}$ , is defined as,

$$i_{G}(V_{PT}) = i_{PT}^{REF}$$

(3)

Clearly as shown in Fig. 3, the gate-to-source voltage range allowed to turn the JFET off decreases with the temperature. So the point has to be carefully accounted to design a system operating over a wide range of temperature for example in aeronautic applications. Therefore, the analysis and the modeling of both  $V_{T0}(T)$  and  $V_{PT}(T)$  are of great interest.

Fig. 2: Measurements and simulation of the I-V gate characteristics for the DUT in linear scales.

## Analysis and modeling of the punch-through phenomenon

The detailed modeling of the punch-through current is given in appendix. It is classically based on the calculation of the current passing through a potential barrier height [5], given by,

$$i_{PT} = -\frac{i_{PT}^{0} \frac{\sqrt{\pi}}{2} \sqrt{\frac{u_{T}}{V_{P}}}}{\frac{1}{a} \int_{0}^{2a} \exp \frac{\psi(y)}{u_{T}} dy} \left( 1 - \exp \left( \frac{V_{GS}}{u_{T}} \right) \right)$$

$$(4)$$

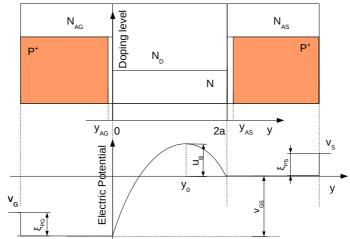

Where,  $V_{GS}$ , is the gate-to-source voltage,  $u_T$ , is the thermal potential, a , is the half thickness of the channel,  $i_{PT}^{ref}$ , is a reference punch-through current defined in appendix, and  $\psi(y)$  the electric potential along the channel. Fig. 4 shows the simplified 1D representation of the punch-through phenomenon as already shown in [2] and [4]. The computation of the punch-through current in the PNP case was presented in [4] and yields to

$$i_{pT} = i_{pT}^{0} \left( 1 - e^{\frac{v_{cs}}{u_{T}}} \right) e^{-\frac{u_{B}}{u_{T}}}$$

(5)

where  $i_{PT}^0 \simeq 7 \, kA$  is a constant defined in appendix representing the maximal punch-through current. The pinch-off voltage is classically given by,

$$V_{p} = \frac{q N_{D} a^{2}}{2 \epsilon} \tag{6}$$

Fig. 3: Measurements (dots) and simulation (lines) of the threshold (top) and punch-through (bottom) voltages, versus the temperature, for the DUT. The green dashed line corresponds to the simulation of the punch-through voltage for k=1 (see Eq. 10).

The barrier height is given by,

$$\mathbf{u}_{\mathrm{B}} = \mathbf{V}_{\mathrm{p}} \left( 1 + \frac{\mathbf{V}_{\mathrm{GS}}}{4 \, \mathbf{V}_{\mathrm{p}}} \right)^{2} \tag{7}$$

| Symbol         | Definition                                         | Value                      |

|----------------|----------------------------------------------------|----------------------------|

| $N_{A}$        | Doping concentration in both gates                 | $5 \times 10^{19} cm^{-3}$ |

| $A_{G}$        | Gate Equivalent Area, estimated from the die area. | 8 mm <sup>2</sup>          |

| V <sub>P</sub> | Pinch-off voltage                                  | 7.29 <i>V</i>              |

Fig. 4: Typical representation of the electric potential for  $V_{\text{GS}}$  between  $V_{\text{T0}}$  and  $V_{\text{PT}}$

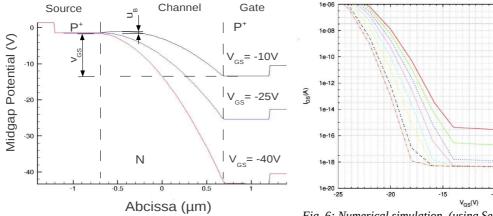

Fig. 7 and Fig. 8 show the leakage current between gate and source. From 0 to the break in Fig. 8 the current is the leakage current of the P+NN+ junction (see Fig. 1) between gate and source. Classically in SiC devices, the measured leakage current is much greater than the generation current of this junction [6]. Higher values of the current correspond to the punch-through current. Fig. 6 shows numerical simulation of the punch-through current and yields to a similar value of the punch-through voltage. The simulated leakage current is very low too!

The calculation is detailed in appendix. The parabolic shape of the electrical potential shown in Fig. 5, is confirmed by the numerical simulations in Fig. 5 and in Equation (7).

Fig. 5: Numerical simulation (using Sentaurus) of the potential across the PNP structure for various  $V_{\text{GS}}$  values

Fig. 6: Numerical simulation (using Sentaurus) of punchthrough current in the PNP structure

Fig. 7 Comparison between simulation and measurements of the gate current (showing the generation current)

Fig. 8: Comparison between simulation and measurements of the gate current (Zoom)

## Computation of the punch-through voltage

Clearly, for sufficiently negative gate-to-source voltage, the punch-through current increases dramatically, and  $1 \gg e^{\frac{V_{GS}}{u_r}}$  so equation (2) may be simplified as,

$$i_{PT} = i_{PT}^0 e^{-\frac{u_B}{u_T}}$$

(8)

Considering the definition of  $V_{PT}$  in (3), combining (8) with (7), yields to

$$\alpha = \ln \left( \frac{i_{pT}^{0}}{i_{pT}^{ref}} \right) = \frac{u_{B}}{u_{T}} = \frac{V_{p}}{u_{T}} \left( 1 + \frac{V_{pT}}{4 V_{p}} \right)^{2}$$

(9)

So,

$$V_{PT} = 4 V_{P} \left( 1 - \sqrt{(k + \alpha) \frac{u_{T}}{V_{P}}} \right)$$

(10)

Which defines the temperature dependence of  $V_{PT}$  because of the temperature dependence of the thermal voltage,  $u_T$ , and the hole mobility,  $\mu_P$ , through  $i_{PT}^0$  (Eq. 37). The factor k has been introduced to account the current level. Without this ratio,  $i_{PT}^{REF} \sim 1 \text{ nA}$  has to be chosen which is not acceptable for the measurement data, but it is compatible with the numerical simulation in Fig. 6. Moreover, the

temperature dependencies are defined by the equations given in appendix and the material data used in [7].

## Computation the gate threshold voltage

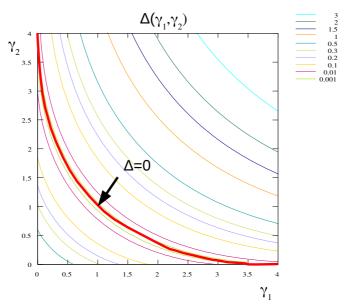

The threshold voltage,  $V_{T0}$ , is by definition the gate-source voltage threshold for which the saturation current reach zero as given in (1). Reference [3] yields a model of the double channel JFET and gives the following expression for the pinch-off current in the lateral channel,

$$i_{CH}^{P} = \frac{V_{P}}{3R_{CH}} \Delta(\gamma_{1}, \gamma_{2})$$

(11)

Where  $R_{CH}$  is the non-modulated channel resistance and  $\gamma_1$  and  $\gamma_2$  are standardized driven values. In blocking condition, that yields to the definition of standardized driven values as,

$$\gamma_1^{\text{OFF}} = \frac{V_{\text{BI}} - V_{\text{GS}}}{V_{\text{p}}} \tag{12}$$

and,

$$\gamma_2^{\text{OFF}} = \gamma_0 = \frac{V_{\text{BI}}}{V_{\text{P}}} \tag{13}$$

By definition, in blocking condition the pinch-off current equals zero [3], so,

$$\Delta(\gamma_1^{\text{OFF}}, \gamma_2^{\text{OFF}}) = 0 \tag{14}$$

The plot of the  $\Delta$  function is given in Fig. 9.

Fig. 9: Plot of the  $\Delta$  function

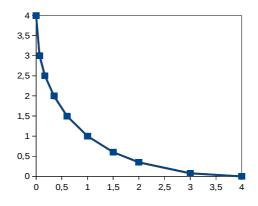

So that defines a relation between  $\gamma_1^{\text{OFF}}$  and  $\gamma_2^{\text{OFF}}$  or  $\gamma_0$ .

$$\mathbf{y}_{1}^{\text{OFF}} = \Gamma_{1}(\mathbf{y}_{0}) \tag{15}$$

*Fig.* 10: Plot of Function  $\Gamma_1(\gamma_0)$

At the blocking threshold, Equation (12) may be rewritten as,

$$\mathbf{v}_{GS} = \mathbf{V}_{TO} \tag{16}$$

$$\gamma_1^{\text{OFF}} = \frac{V_{\text{BI}} - V_{\text{T0}}}{V_{\text{P}}} \tag{17}$$

Which may be expressed as,

$$V_{T0} = V_{BI} - \Gamma_1 \left( \frac{V_{BI}}{V_p} \right) V_p \tag{18}$$

The later expression yields the temperature dependence of  $V_{\text{T0}}$  through the temperature dependence of  $V_{\text{BI}}$ .

Notice that Equation (18) is different from the standard JFET model given by,

$$V_{T0} = V_{RI} - V_{P} \tag{19}$$

#### **Results and discussion**

The punch-through and threshold voltages were computed using equation (10) and (19) respectively. Fig. 5 Shows the superimposition of these computations and the experimental data. Clearly a good agreement was reached. An empirical value, k, has been used in equation (10) to reach a better fitting with experimental data. The issue is probably related to the modeling of the leakage current that classically failed in wide band gap device as shown in Fig. 6 but the obtained temperature dependence is very good, and based on physical data of the SiC-4H material. Moreover the empirical value, k, introduces a shift of about 2 V in the value of the punch-through voltage, so about 10% of error without correction with the empirical factor. If the computation seems to be complex because of the number of equations, these equations may be easily implemented in a compact model of the JFET, as in [3] using a modeling language like MAST or VHDL-AMS.

#### Conclusion

The punch-through voltage,  $V_{PT}$ , and the threshold voltage,  $V_{T0}$ , are the limits that define the gate-to-source range allowed to block the VJFET. Unfortunately, both parameters depend on the temperature. The paper has presented some measurement results versus the temperature of these parameters. Clearly, the useful gate-voltage range reduces with increasing temperatures. The paper has also developed from a physical analysis of the VJFET device, a complete analysis of the dependence of these parameters with respect to the temperature by deriving analytical expressions of these parameters. The obtained models are in good agreement with the experimental data. It remains to integrate these expressions in a complete model of the VJFET.

## References

- [1] S. M. Sze and Kwok K. Ng, Physics of semiconductor devices, Wiley-Intersciences, 2007

- [2] Kaminski, N.; Niemann, E.; Sheppard, S.T.; Punch-through behaviour of wide bandgap materials (with example in 6H-SiC) and its benefit to JFETs Materials Science Forum, vols. 264-268, pt. 2, pp. 1073-1076. 1998

- [3] MOREL Hervé, HAMIEH Youness, TOURNIER Dominique, ROBUTEL Rémi, DUBOIS Fabien, RISALETTO Damien, MARTIN Christian, BERGOGNE Dominique, BUTTAY Cyril, MEURET Régis, "A Multi-Physical Model of the VJFET With a Lateral Channel", EPE 2011, 30 Aug. 1st Sept. 2011, Birmingham.

- [4] Fabien Dubois, Hervé Morel, Dominique Bergogne and Régis Meuret, «Modeling of the Punch-Through Effect in Normally-On SiC JFET used in High Temperature Inverter for Aerospace Application», IMAPS, High Temperature Electronics Conference (HITEC), p. 154–161, May 2012.

- [5] B. Jayant Baliga, Modern Power Devices, Kriger Pub. Company, 1992.

- [6] Charles E. Weitzel, John W. Palmour, Calvin H. Carter, Karen Moore, Kevin J. Nordquist, Scott Allen, Christine Thero and Mohit Bhatnagar, "Silicon Carbide High-Power Devices", IEEE Trans. On Electron Devices, VOL. 43, NO. 10, OCTOBER 1996.

- [7] Christophe Raynaud, Dominique Tournier, Hervé Morel and Dominique Planson, "Comparison of high voltage and high temperature performances of wide bandgap semiconductors for vertical power devices", Diamond and Related Materials, Volume 19, Issue 1, January 2010, Pages 1-6

## **Appendix**

#### Calculating the barrier height

In the N-type region, it is obtained,

$$\frac{\partial E}{\partial y} = \frac{q N_D}{\epsilon}$$

(20)

Which yields to the following expression for the electric potential in the N-region,

$$\psi(y) = \psi_{M} - \frac{q N_{D}}{\epsilon} \frac{(y - y_{0})^{2}}{2} = \psi_{M} - V_{P} \left(\frac{y - y_{0}}{a}\right)^{2}$$

(21)

Assuming,

$$\psi(2a) = 0 = \psi_{M} - V_{P} \left( \frac{2a - y_{0}}{a} \right)^{2}$$

(22)

The definitions in Fig. 2 yield to,

$$\psi(0) = v_{GS} = \psi_{M} - V_{P} \left(\frac{0 - y_{0}}{a}\right)^{2}$$

(23)

The maximum is reached for,

$$\psi(\mathbf{y}_0) = \mathbf{u}_{\mathbf{p}} = \psi_{\mathbf{M}} \tag{24}$$

So, the difference between Equations (23) and (22) yields to,

$$\mathbf{v}_{GS} = -\mathbf{V}_{P} \left( \left( 2 - \frac{\mathbf{y}_{0}}{\mathbf{a}} \right)^{2} - \left( \frac{\mathbf{y}_{0}}{\mathbf{a}} \right)^{2} \right) = -4 \, \mathbf{V}_{P} \left( 1 - \frac{\mathbf{y}_{0}}{\mathbf{a}} \right)$$

(25)

and

$$\frac{y_0}{a} = 1 - \frac{v_{GS}}{4 V_P}$$

(26)

Substituting it in (22) yields to Equation (7),

$$u_{\rm B} = \psi_{\rm M} = V_{\rm P} \left( 2 - \frac{y_0}{a} \right)^2 = V_{\rm P} \left( 1 + \frac{v_{\rm GS}}{4 V_{\rm P}} \right)^2 \tag{27}$$

The electrical potential is obtained from Equation (21) by substituting (26) and (27),

$$\psi(y) = V_{p} \left[ \left( 1 + \frac{V_{GS}}{4 V_{p}} \right)^{2} - \left( \frac{y}{a} - 1 + \frac{V_{GS}}{4 V_{p}} \right)^{2} \right] = V_{GS} - V_{p} \left[ \frac{y^{2}}{a^{2}} + \frac{2 y}{a} \left( \frac{V_{GS}}{4 V_{p}} - 1 \right) \right]$$

(28)

#### Calculating the punch-through current

Assuming a constant hole-mobility, the drift-diffusion equation for the holes may be written as,

$$J_{p} = q\mu_{p} \left( pE - u_{T} \frac{\partial p}{\partial y} \right) = -q\mu_{p} \left( p \frac{\partial \psi}{\partial y} + u_{T} \frac{\partial p}{\partial y} \right)$$

(29)

Moreover it is well known that,

$$\frac{\partial}{\partial y} \left( p e^{\frac{\psi}{u_{T}}} \right) = \frac{\partial p}{\partial y} e^{\frac{\psi}{u_{T}}} + \frac{p}{u_{T}} e^{\frac{\psi}{u_{T}}} \frac{\partial \psi}{\partial y} = e^{\frac{\psi}{u_{T}}} \left( \frac{\partial p}{\partial y} + \frac{p}{u_{T}} \frac{\partial \psi}{\partial y} \right)$$

(30)

So,

$$J_{p}e^{\frac{\Psi}{u_{T}}} = -q\mu_{p}u_{T}e^{\frac{\Psi}{u_{T}}}\left(\frac{p}{u_{T}}\frac{\partial\Psi}{\partial y} + \frac{\partial p}{\partial y}\right) = -q\mu_{p}u_{T}\frac{\partial}{\partial y}\left(pe^{\frac{\Psi}{u_{T}}}\right)$$

(31)

The integration of equation (31) in the interval  $\left[0-\epsilon_y,2a+\epsilon_y\right]$  where  $\epsilon_y$  is a small length that insures the side are both in the P+ layers, yields to,

$$\int_{-\epsilon_{v}}^{2a+\epsilon_{y}} J_{p} e^{\frac{\psi}{u_{T}}} dy = -q \mu_{p} u_{T} \int_{-\epsilon_{v}}^{2a+\epsilon_{y}} \frac{\partial}{\partial y} \left( p e^{\frac{\psi}{u_{T}}} \right) dy = -q \mu_{p} u_{T} \left[ p e^{\frac{\psi}{u_{T}}} \right]_{-\epsilon_{y}}^{2a+\epsilon_{y}}$$

(32)

Assuming a uniform current density inside the channel, that may be simplified as,

$$J_{p} \int_{-\epsilon_{u}}^{2a+\epsilon_{y}} e^{\frac{\psi}{u_{r}}} dy = -q \mu_{p} u_{T} \left( N_{AS} e^{\frac{\psi(2a+\epsilon_{y})}{u_{r}}} - N_{AG} e^{\frac{\psi(-\epsilon_{y})}{u_{r}}} \right)$$

(33)

Assuming same value of the doping concentration in the both sides, it is obtained,

$$J_{p} \int_{0}^{2a} e^{\frac{\psi}{u_{r}}} dy = q \mu_{p} u_{T} N_{A} \left( 1 - e^{\frac{v_{GS}}{u_{T}}} \right)$$

(34)

The current through the structure is given by,

$$i_{pT} = J_p A_G \tag{35}$$

So Equation (4) is obtained

$$i_{PT} = -\frac{i_{PT}^{r0}}{\frac{1}{a} \int_{0}^{2a} \exp \frac{\psi(y)}{u_{T}} dy} \left( 1 - \exp \left( \frac{V_{GS}}{u_{T}} \right) \right)$$

(36)

Where,

$$i_{PT}^{r0} = \frac{q \,\mu_{P} \,N_{A} \,u_{T} \,A_{G}}{a} \tag{37}$$

And,

$$\alpha_{\rm PT} = \frac{1}{a} \int_0^{2a} \exp \frac{\psi(y)}{u_{\rm T}} dy \tag{38}$$

Equation (36)

$$i_{PT} = -\frac{i_{PT}^{r0}}{\alpha_{PT}} \left( 1 - \exp\left(\frac{V_{GS}}{u_{T}}\right) \right) \tag{39}$$

Using (28) Equation (38),

$$\alpha_{\rm PT} = \frac{1}{a} \int_{0}^{2a} \exp \left[ \frac{v_{\rm GS} - V_{\rm P} \left[ \frac{y^{2}}{a^{2}} + \frac{2y}{a} \left( \frac{v_{\rm GS}}{4 V_{\rm P}} - 1 \right) \right]}{u_{\rm T}} \right] dy \tag{40}$$

Defining,

$$\beta_{\rm PT} = \frac{V_{\rm p}}{u_{\rm T}} \tag{41}$$

$$\gamma_{\text{PT}} = \frac{\mathbf{v}_{\text{GS}}}{4 \, \mathbf{V}_{\text{p}}} - 1 \tag{42}$$

$$u = \frac{y}{a} \tag{43}$$

$$z = u + \gamma_{PT} \tag{44}$$

Equation (40) may be rewritten as,

$$\alpha_{\text{PT}} = \frac{a}{a} \exp \frac{\mathbf{v}_{\text{GS}}}{\mathbf{u}_{\text{T}}} \int_{0}^{2} \exp \left(-\beta_{\text{PT}} \left[\mathbf{u}^{2} + 2\mathbf{u} \, \mathbf{y}_{\text{PT}}\right]\right) d\mathbf{u}$$

(45)

or,

$$\alpha_{\rm PT} = \exp \frac{\mathbf{v}_{\rm GS}}{\mathbf{u}_{\rm T}} \int_{0}^{2} \exp \left(-\beta_{\rm PT} \left[\mathbf{z}^2 - \mathbf{y}_{\rm PT}^2\right]\right) d\mathbf{z} \tag{46}$$

SO.

$$\alpha_{\text{PT}} = \exp\left(\frac{\mathbf{v}_{\text{GS}}}{\mathbf{u}_{\text{T}}} + \beta_{\text{PT}} \,\mathbf{y}_{\text{PT}}^2\right) \int_0^2 \exp\left(-\beta_{\text{PT}} \,\mathbf{z}^2\right) d\mathbf{z} \tag{47}$$

Accounting the error function definition,

$$\operatorname{erf}(\mathbf{x}) = \frac{2}{\sqrt{\pi}} \int_{0}^{\mathbf{x}} \exp(-\eta^{2}) d\eta$$

(48)

Using,

$$\eta = \sqrt{\beta_{PT}} z$$

(49)

it is obtained,

$$\int_{0}^{x} \exp -\eta^{2} d\eta = \int_{0}^{\frac{x}{\sqrt{\beta_{PT}}}} \exp -\beta_{PT} z^{2} \sqrt{\beta_{PT}} dz = \frac{\sqrt{\pi}}{2} \operatorname{erf}(x)$$

(50)

Equation (47) may be rewritten as,

$$\alpha_{\text{PT}} = \frac{1}{2} \sqrt{\frac{\pi}{\beta_{\text{PT}}}} \exp\left(\frac{\mathbf{v}_{\text{GS}}}{\mathbf{u}_{\text{T}}} + \beta_{\text{PT}} \gamma_{\text{PT}}^2\right) \operatorname{erf}\left(2\sqrt{\beta_{\text{PT}}}\right)$$

(51)

Assuming that,

$$\beta_{\rm PT} \gg 1$$

(52)

and the error function is very near 1 for high abscissa values, Equation () yields to

$$\alpha_{\text{PT}} \simeq \frac{1}{2} \sqrt{\frac{\pi}{\beta_{\text{PT}}}} \exp\left(\frac{\mathbf{v}_{\text{GS}}}{\mathbf{u}_{\text{T}}} + \beta_{\text{PT}} \gamma_{\text{PT}}^2\right) = \frac{\sqrt{\pi}}{2} \sqrt{\frac{\mathbf{u}_{\text{T}}}{\mathbf{V}_{\text{P}}}} \exp\left(\frac{\mathbf{v}_{\text{GS}}}{\mathbf{u}_{\text{T}}} + \frac{\mathbf{V}_{\text{P}}}{\mathbf{u}_{\text{T}}} \left(\frac{\mathbf{v}_{\text{GS}}}{4 \mathbf{V}_{\text{P}}} - 1\right)^2\right)$$

(53)

$$i_{PT} = \frac{i_{PT}^{r0}}{\left(\frac{\sqrt{\pi}}{2}\sqrt{\frac{u_{T}}{V_{P}}}\right)} \exp\left(-\frac{v_{GS}}{u_{T}} - \frac{V_{P}}{u_{T}}\left(\frac{v_{GS}}{4V_{P}} - 1\right)^{2}\right) \left(\exp\left(\frac{V_{GS}}{u_{T}}\right) - 1\right)$$

(54)

Which may be written as Equation (5),

$$i_{PT} = i_{PT}^{0} \exp\left(-\frac{u_{B}}{u_{T}}\right) \left(\exp\left(\frac{V_{GS}}{u_{T}}\right) - 1\right)$$

(55)

$$i_{PT}^{0} = \frac{i_{PT}^{r0}}{\left(\frac{\sqrt{\pi}}{2}\sqrt{\frac{u_{T}}{V_{P}}}\right)} = \frac{q\,\mu_{P}\,N_{A}\,u_{T}\,A_{G}}{\sqrt{\frac{\pi}{2}}\,L_{ND}}$$

(56)

$$L_{ND} = \sqrt{\frac{\epsilon u_{T}}{q N_{D}}} = a \sqrt{\frac{u_{T}}{2 V_{P}}}$$

(57)

An assessed value is given by,

$$i_{PT}^{0}(300K) = \frac{q \mu_{p} u_{T} N_{A} A_{G}}{\sqrt{\frac{\pi}{2}} L_{ND}} \approx 7.0 \text{ kA}$$

(58)