## Electrical characterization of In0.53Ga0.47As/In0.52Al0.48As high electron mobility transistors on plastic flexible substrate under mechanical bending conditions

J. Shi, Nicolas Wichmann, Yannick Roelens, S. Bollaert

#### ▶ To cite this version:

J. Shi, Nicolas Wichmann, Yannick Roelens, S. Bollaert. Electrical characterization of In 0.53Ga 0.47As/In 0.52Al 0.48As high electron mobility transistors on plastic flexible substrate under mechanical bending conditions. Applied Physics Letters, 2013, 102, pp.243503-1-4. 10.1063/1.4811787. hal-00871898

### HAL Id: hal-00871898 https://hal.science/hal-00871898v1

Submitted on 27 May 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Electrical characterization of $In_{0.53}Ga_{0.47}As/In_{0.52}Al_{0.48}As$ high electron mobility transistors on plastic flexible substrate under mechanical bending conditions

Cite as: Appl. Phys. Lett. **102**, 243503 (2013); https://doi.org/10.1063/1.4811787 Submitted: 17 May 2013 • Accepted: 06 June 2013 • Published Online: 19 June 2013

J. Shi, N. Wichmann, Y. Roelens, et al.

### ARTICLES YOU MAY BE INTERESTED IN

Microwave performance of 100 nm-gate In<sub>0.53</sub>Ga<sub>0.47</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As high electron mobility transistors on plastic flexible substrate

Applied Physics Letters 99, 203505 (2011); https://doi.org/10.1063/1.3663533

A converging route towards very high frequency, mechanically flexible, and performance stable integrated electronics

Journal of Applied Physics 113, 153701 (2013); https://doi.org/10.1063/1.4801803

Gigahertz operation in flexible transistors on plastic substrates

Applied Physics Letters 88, 183509 (2006); https://doi.org/10.1063/1.2198832

## Lock-in Amplifiers up to 600 MHz

### Electrical characterization of In<sub>0.53</sub>Ga<sub>0.47</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As high electron mobility transistors on plastic flexible substrate under mechanical bending conditions

J. Shi, N. Wichmann, Y. Roelens, and S. Bollaert

Institute of Electronics, Microelectronics and Nanotechnology, UMR-CNRS 8520, University of Lille 1,

Villeneuve d'Ascq 59652, France

(Received 17 May 2013; accepted 6 June 2013; published online 19 June 2013)

InAlAs/InGaAs high electron mobility transistors (HEMTs) have been transferred onto polyimide flexible substrate. By means of epitaxial layer optimization, kink effect in HEMT on flexible substrate, which existed in our previous work, has been suppressed. The value of maximum drain current reaches  $580 \, \text{mA/mm}$  and high cut-off frequencies  $f_T = 160 \, \text{GHz}$ ,  $f_{max} = 290 \, \text{GHz}$  are obtained for unbent status. The effect of mechanical bending conditions on electrical performance has been also investigated in static and dynamic regimes. This study indicates that electrical characteristics are weakly affected by bending induced strain. These bending mechanical tests demonstrate the viable flexibility of the devices. ©  $2013 \, AIP \, Publishing \, LLC$ . [http://dx.doi.org/10.1063/1.4811787]

Flexible electronics have been attracting considerable attention over the past decade, due to their advantages, such as light weight, toughness, and mechanical bendability. In order to develop these microelectronic circuits for future wide scale applications, excellent transistors are needed. Several approaches of flexible transistors have been reported (e.g., organic thin film transistors, polycrystalline-silicon, as well as amorphous silicon). <sup>1–4</sup> However, the main problem is that their low effective carrier mobilities definitely limit their performances in the higher frequency applications. Owing to the high electron mobility of heterostructure III-V semiconductor materials, the impressive performance of high frequency III-V metal-oxide-semiconductor field-effect transistors which are fabricated directly on the flexible substrate has been demonstrated.<sup>5</sup> Recently, we reported a feasible method for transferring the InAlAs/InGaAs high electron mobility transistors (HEMTs) into the polyimide substrate (Kapton)<sup>6</sup> by means of adhesive bonding technique. The fabricated devices have provided high cut-off frequencies  $(f_T = 120 \,\mathrm{GHz})$  and  $f_{MAX} = 280 \,\mathrm{GHz}$ . However, the major defect in our previous experiment is the presence of the kink effect which leads to the abnormally low static drain current. In this letter, we propose an optimized design of the layer structure and show the improvement on electrical performance. Transistors can operate with higher drain current and cut-off frequencies, and the kink effect is completely suppressed. Moreover, static (DC) and dynamic (RF) performances comparison for various bending radius down to 12.5 mm is also presented.

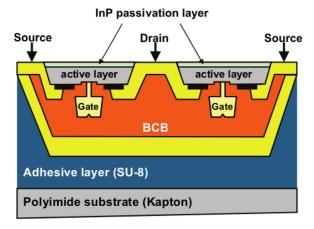

Figure 1 shows the cross section of the optimized layer structure before bonding on the polyimide substrate. Lattice-matched InAlAs-InGaAs HEMT epitaxial layers have been grown on an InP substrate by a solid source molecular beam epitaxy. Active layer is composed of an N<sup>+</sup> InGaAs cap layer  $(6 \times 10^{18} \, \mathrm{cm}^{-3})$ , an InAlAs barrier, two Silicon  $\delta$ -doping planes, two InAlAs spacers, an InGaAs channel and an InAlAs buffer layer. Next, InP passivation layer and InGaAs etch-stop layer have been added. It is important to point out that the epitaxial layer structure is upside down

during the device fabrication. Consequently, InP passivation layer is used to avoid carrier depletion of the active layer caused by the Fermi level pinning at the surface. The InGaAs etch-stop layer, used for the transfer process onto flexible substrate, is etched during the last step of device fabrication. In our previous work, InP passivation layer was not sufficient to avoid a partial depletion of the channel caused by the Fermi level pinning due to the surface potential at the air-semiconductor interface leading to high kink effect. In this work, a second Silicon delta-doping plane  $(3 \times 10^{12} \, \mathrm{cm}^{-2})$  has been added between the channel and the buffer layer which screens the surface potential effect.

The fabrication steps of HEMTs on flexible substrate (HEMT-FS) are the same as those already reported in our previous work<sup>6</sup> with identical device geometry (physical gate length of 100 nm and gate width of  $2 \times 50 \,\mu\text{m}$ ). The Ni/Ge/Au/Ni/Au ohmic contacts are defined by electronbeam lithography, metal E-beam evaporation and annealed at 295 °C for 20 s. Then, the mesa wet-etching for device isolation is performed. This wet-etching stops at the interface between InP passivation layer and InGaAs etch-stop layer. Next, bonding pads are realized by the metallization of Ti/Au/Ti. After the gate-recess process is carried out and Ti/Pt/Au/Ti gate metals are evaporated and lifted off. Next, thin-film microstrip (TFMS) access lines fabrication and adhesive bonding process. During the last step, the InP substrate and InGaAs etch-stop layer of the upside-down HEMT structure are, respectively, removed by an accurate wetetching process which stops on the InP passivation layer. Figure 2 presents the schematic representation of the 2 gate fingers HEMT-FS device at the end of fabrication process.

All the following measurements are carried out at room temperature. Hall measurement has been performed on active layer (with cap layer) of HEMT-FS after device fabrication. Hall density ( $n_H$ ) and Hall mobility ( $\mu_H$ ) reach  $8.9 \times 10^{12}$  cm<sup>-2</sup> and 7300 cm<sup>2</sup> · V<sup>-1</sup> s<sup>-1</sup>, respectively. In our previous work, it was found that  $n_H$  and  $\mu_H$  were 5.4  $\times$  10<sup>12</sup> cm<sup>-2</sup> and 7400 cm<sup>2</sup> · V<sup>-1</sup> s<sup>-1</sup>. We can observe that hall mobilities are unchanged while  $n_H$  is strongly increased

FIG. 1. Epitaxial layers of InP-based HEMT-FS (HEMT on flexible substrate).

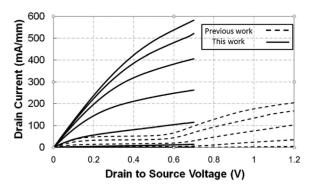

due to the additional silicon doping plane. Figure 3 shows the typical output characteristics of the transistor in unbent condition. Previously reported output characteristics are also plotted. For this work, the value of maximum drain current  $Id_{MAX}$  reaches 580 mA/mm for a gate-to-source voltage  $V_{GS} = 0 \text{ V}$ . Compared with our previous work, this value of this current increase by  $\sim 176\%$  and the kink effect is totally suppressed. The disappearance of the kink effect can be attributed to the optimized layer structure which fully prevents the depletion of the channel layer and, consequently, avoids the low electron channel concentration of the source side in the recessed area.<sup>7,8</sup> Nevertheless, the maximum extrinsic transconductance  $g_m$  is 750 mS/mm for a drain-tosource voltage  $V_{DS} = 0.6 \text{ V}$ . The  $g_m$  in our previous work is equal to 800 mS/mm. This lower value of the  $g_m$  can arise from the increase of coulomb scattering induced by adding of second  $\delta$ -doping plane. Moreover, threshold voltage  $V_{TH}$ is estimated to be  $-1.2\,\mathrm{V}$ . The value of  $V_{TH}$  is equal to -0.25 V in our previous work. This negative shift of  $V_{TH}$  can be attributed to the higher charge density in the channel observed on measured hall parameters. Consequently, higher negative gate voltage is needed to deplete the channel.

FIG. 2. Schematic representation of 2 gate- fingers HEMT-FS.

FIG. 3. (Solid line) Output characteristics of 100 nm-gate length HEMT-FS in unbent status. Gate bias voltage is 0 V for the top curve and the gate step is  $-0.2\,\mathrm{V}$ . (Dashed line) Output characteristics previously reported  $^6$  of 100 nm-gate length HEMT-FS in unbent status.

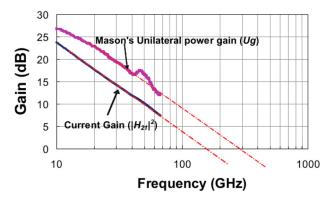

The S-parameters of the 100 nm-gate HEMT-FS have been measured by using a vector network analyzer. The Mason's unilateral power gain Ug and the extrinsic current gain  $|H_{21}|^2$  are shown as a function of frequency in Figure 4. Note that parasitic components related to the probing pads have been carefully de-embedded from the measured S-parameters using "open" and "short" devices fabricated on the same wafer. 9 Based on the usual 6 dB/octave extrapolation, the HEMT-FS exhibits a  $f_T$  of 160 GHz and a  $f_{MAX}$  of 290 GHz. In our previous work, the HEMT-FS exhibited a  $f_T$ of 120 GHz and a  $f_{MAX}$  of 280 GHz. Despite the lower  $g_m$ obtained for these devices compared with previous work,  $f_T$ and  $f_{MAX}$  have increased. This RF performance improvement can be arised from the higher charge density measured in this active layer which decrease source and drain parasitic resistances ( $R_S$  and  $R_D$ ). 10

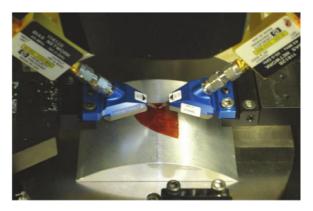

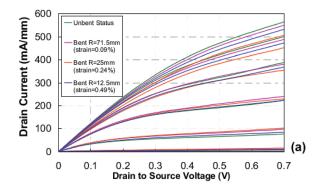

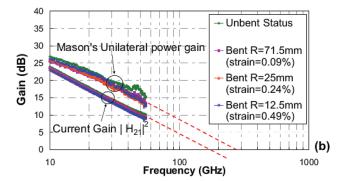

In addition, we have investigated the influence of the substrate mechanical flexure on static and dynamic performance. As shown in Figure 5, we have measured HEMT-FS by using an arc-shaped metal supports of various bending radius which allows to bend the flexible substrate during measurements. All measurements have been performed at room temperature and the bending induced strain has been applied along the gate width. Note that similar electrical results (not shown) have been obtained when strain is applied along the source-drain direction. Figure 6(a) shows a sequence of current-voltage curves measured at different bending radius: 71.5 mm, 25 mm, and 12.5 mm. The corresponding strains,

FIG. 4. Frequency dependence of Mason's unilateral power gain  $U_g$  and current gain  $|H_{21}|^2$  measured at  $V_{\rm DS} = 0.7 \, {\rm V}$  for unbent status. Dashed-dotted lines correspond to  $-20 \, {\rm dB/decade}$  extrapolation.

FIG. 5. Test bench for on wafer DC and RF measurement under bending conditions.

FIG. 6. (a) Typical HEMT-FS I-V characteristics obtained for various bending radius (and their corresponding surface strains). Gate bias voltage is 0 V for top curves and gate step is  $-0.2 \,\mathrm{V}$ . (b) Frequency dependence of current gain  $|H_{21}|^2$  and Mason's unilateral power gain  $U_g$  at  $V_{DS} = 0.7$  V for various bending radius (and their corresponding surface strains).

calculated by the mechanical modeling of multi-layers for flexible devices, 11 are 0.09%, 0.24%, and 0.49%, respectively. The slight difference between the four current-voltage curves suggests that HEMT-FS static characteristics are weakly affected by the bending conditions. Indeed, maximum change of drain current is lower than 13% for these three bending conditions. Figure 6(b) shows the comparison of frequency dependence microwave gains for these three bending conditions. One can observe that the decrease of bending radius leads to a slight decrease of  $f_T$ . Moreover,  $f_{MAX}$  of unbent status is higher than the other three bending status. In order to interpret these results, small signal equivalent circuit (SSEC) models of HEMT-FS for these different bending values have been also extracted from the measured S-parameters. Table I summarizes the measured cut-off frequencies ( $f_T$  and  $f_{MAX}$ ) and the relevant elements of SSEC models obtained for different bending conditions. Note that de-embedding procedure of parasitic components has been performed under bending status for each bending radius.

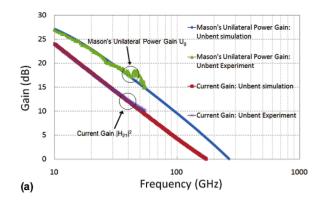

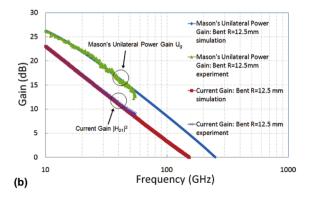

From Table I, cut-off frequencies degradation for bent devices seems to be mainly attributed to the decrease of  $gm_i$ and/or Rg since no significant change in intrinsic resistances (Rs and Rd), output conductance  $g_d$ , and intrinsic capacitances (Cgs and Cgd) is observed. In order to confirm this hypothesis, calculated gains from extracted SSEC models using Advanced Design System (ADS) software have been done. First, to validate the approach used here, experimental frequency dependence of  $|H_{21}|^2$  and Ug gains are compared with those obtained from ADS software for unbent condition (Figure 7(a)) and for the highest bending radius (Figure 7(b)). We can observe that simulated results are in good agreement with experimental measurements with similar cut-off frequencies, and hence validating our SSEC model. Next, in order to estimate the main element of SSEC responsible for cut-off frequencies degradation when strain is applied,  $|H_{21}|^2$ and Ug gains have been calculated by modifying separately  $gm_i$  value and/or Rg value from unbent SSEC model without changing values of other electrical elements. For these simulations,  $gm_i$  and Rg have taken their respective values obtained for bent condition of  $R = 12.5 \,\text{mm}$  (i.e.,  $893 \,\text{mS/mm}$ and  $104 \Omega/\text{mm}$ , respectively). Table II summarizes cut-off frequencies obtained from theses simulations.

From unbent SSEC model, by only changing  $gm_i$  value from unbent to bent condition (i.e., 1020 mS/mm to 893 mS/ mm),  $f_T$  and  $f_{MAX}$  reach 145 GHz and 275 GHz, respectively.  $f_T$  is close to experimental value (140 GHz) but  $f_{MAX}$  is relatively far away. In the same way, by only changing Rg value from unbent to bent condition (i.e., 69  $\Omega$ /mm to 104  $\Omega$ /mm),  $f_T$  and  $f_{MAX}$  reach 160 GHz and 280 GHz. In this case, only  $f_{MAX}$  is affected by the gate resistance degradation but large difference between experimental value (255 GHz) and simulated value (280 GHz) is observed. Finally, when Rg and  $gm_i$ are simultaneously modified, simulated and experimental results are similar. Consequently, this study shows RF performance degradation is related to the decrease of  $gm_i$  and Rg elements but  $gm_i$  degradation is mainly responsible of cut-off frequencies variation.  $gm_i$  decrease can be explained

TABLE I. Extracted SSEC model and extrapolated  $f_{T}f_{MAX}$  of 100 nm-gate HEMT-FS under various bending statuses.

|                        | g <sub>mi</sub> (mS/mm) | g <sub>d</sub> (mS/mm) | Cgs (fF/mm) | Cgd (fF/mm) | Rg (Ω/mm) | Rs (Ω mm) | Rd (Ω mm) | $f_T(GHz)$ | $f_{MAX}$ (GHz) |

|------------------------|-------------------------|------------------------|-------------|-------------|-----------|-----------|-----------|------------|-----------------|

| Unbent status          | 1020                    | 131                    | 597         | 194         | 69        | 0.34      | 0.35      | 160        | 290             |

| Bending radius 71.5 mm | 972                     | 124                    | 603         | 190         | 107       | 0.34      | 0.35      | 158        | 250             |

| Bending radius 25 mm   | 950                     | 128                    | 621         | 183         | 110       | 0.34      | 0.38      | 156        | 250             |

| Bending radius 12.5 mm | 893                     | 110                    | 611         | 186         | 104       | 0.35      | 0.39      | 140        | 255             |

FIG. 7. Comparison of Mason's unilateral power gain  $U_g$  and current gain  $|H_{21}|^2$  measured in fabricated 100 nm-gate HEMT-FS with those obtained from SSEC model: (a): for unbent condition, (b): for 12.5 mm bending radius.

TABLE II. Cut-off frequencies extracted from unbent SSEC model and from unbent SSEC model by changing  $gm_i$  and/or Rg values obtained with bending radius of 12.5 mm.

|                          | Experimental results with R = 12.5 mm | Unbent<br>SSEC<br>model | Unbent<br>SSEC<br>model<br>with<br>gm <sub>bent</sub> | Unbent<br>SSEC<br>model<br>with<br>Rg <sub>bent</sub> | Unbent<br>SSEC<br>model<br>with Rg <sub>bent</sub><br>and gm <sub>bent</sub> |

|--------------------------|---------------------------------------|-------------------------|-------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------|

| $f_T (\mathrm{GHz})$     | 140                                   | 160                     | 145                                                   | 160                                                   | 145                                                                          |

| $f_{MAX} (\mathrm{GHz})$ | 255                                   | 300                     | 275                                                   | 280                                                   | 260                                                                          |

by the bending induced strain on the epitaxial layer which degrades the electron transport properties in the channel. Nevertheless, Rg degradation is not clear at this time. Finally, it is noted that when devices return to original state (unbent condition) after many stress measurements,  $f_T$  and  $f_{MAX}$  retrieve their initial values. This behavior indicates that the decrease of electrical performance is not related to irreversible device degradation.

In summary, this letter reports an approach to completely eliminate the kink effect region of our  $100 \, \mathrm{nm}$ -gate  $\mathrm{In}_{0.53}\mathrm{Ga}_{0.47}\mathrm{As/In}_{0.52}\mathrm{Al}_{0.48}\mathrm{As}$  HEMTs on the flexible substrate (Kapton). The improved transistors exhibit the much higher drain current ( $580 \, \mathrm{mA/mm}$ ) and high cut-off frequencies behavior ( $f_T = 160 \, \mathrm{GHz}$ ,  $f_{MAX} = 290 \, \mathrm{GHz}$ ) in unbent condition. Moreover, measured devices for various bending radius show no obvious electrical degradation (lower than 15%). By means of SSEC model, RF performance degradation has been attributed to the decrease of  $gm_i$  and Rg. All the above characteristics together with the feasible bending properties provide the highly promising way to integrating large-area radio-frequency communication devices and highspeed processing units onto the flexible substrate.

<sup>&</sup>lt;sup>1</sup>K. H. Cherenack, A. Z. Kattamis, B. Hekmatshoar, J. C. Sturm, and S. Wagner, IEEE Electron Device Lett. **28**, 1004 (2007).

<sup>&</sup>lt;sup>2</sup>S. Saxena, D. C. Kim, J. H. Park, and J. Jang, IEEE Electron Device Lett. **31**, 1242 (2010).

<sup>&</sup>lt;sup>3</sup>U. Haas, H. Gold, A. Haase, G. Jakopic, and B. Stadlober, Appl. Phys. Lett. 91, 043511 (2007).

<sup>&</sup>lt;sup>4</sup>A. Z. Kattamis, R. J. Holmes, I.-C. Cheng, K. Long, J. C. Sturm, S. R. Forrest, and S. Wagner, IEEE Electron Device Lett. 27, 49 (2006).

<sup>&</sup>lt;sup>5</sup>C. Wang, J. Chien, H. Fang, K. Takei, J. Nah, E. Plis, S. Krishna, A. Niknejad, and A. Javey, Nano. Lett. 12(8), 4140 (2012).

<sup>&</sup>lt;sup>6</sup>J. Shi, N. Wichmann, Y. Roelens, and S. Bollaert, Appl. Phys. Lett. 99, 203505 (2011).

<sup>&</sup>lt;sup>7</sup>M. H. Somerville, A. Ernst, and J. A. del Alamo, IEEE Trans. Electron Devices 47, 922 (2000).

<sup>&</sup>lt;sup>8</sup>T. Suemistu, T. Enoki, M. Tomizawa, N. Shigekawa, and Y. Ishii, in *International Conference on Indium Phosphide and Related Materials* (IPRM 1997), p. 365.

<sup>&</sup>lt;sup>9</sup>P. J. van Wijnen, H. R. Claessen, and E. A. Wolsheimer, in *Proceedings of IEEE Bipolar Circuits and Technology Meeting* (1987), p. 70.

<sup>&</sup>lt;sup>10</sup>Paul J. Tasker and B. Hughes, IEEE Electron Device Lett. **10**, 291 (1989).

<sup>&</sup>lt;sup>11</sup>C.-J. Chiang, C. Winscom, S. Bull, and A. Monkman, Org. Electron. 10(7), 1268 (2009).