## Statistical leakage estimation in 32nm CMOS considering cells correlations

Smriti Joshi, Anne Lombardot, Marc Belleville, Edith Beigné, Stéphane Girard

#### ▶ To cite this version:

Smriti Joshi, Anne Lombardot, Marc Belleville, Edith Beigné, Stéphane Girard. Statistical leakage estimation in 32nm CMOS considering cells correlations. FTFC - 11th IEEE conference on Faible Tension Faible Consommation, Jun 2012, Paris, France. pp.1-4, 10.1109/FTFC.2012.6231721. hal-00803441

HAL Id: hal-00803441

https://hal.science/hal-00803441

Submitted on 22 Mar 2013

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Statistical Leakage Estimation in 32nm CMOS Considering Cells Correlations

Smriti Joshi <sup>1</sup>\*, Anne Lombardot <sup>1</sup>

STMicroelectronics

F-38926, Crolles, France,

{smriti.joshi,anne.lombardot }@st.com

Marc Belleville <sup>2</sup>,Edith Beigne <sup>2</sup>

<sup>2</sup>CEA, LETI, MINATEC Campus

38054, Grenoble, France

{marc.belleville,edith.beigne}@cea.fr

Stéphane Girard <sup>3</sup>

<sup>3</sup> INRIA, Montbonnot,

38334, Saint-Ismier Cedex, France

{stephane.girard}@inrialpes.fr

Abstract-In this paper a method to estimate the leakage power consumption of CMOS digital circuits taking into account input states and process variations is proposed. The statistical leakage estimation is based on a pre characterization of library cells considering correlations ( $\rho$ ) between cells leakages. A method to create cells leakage correlation matrix is introduced. The maximum relative error achieved in the correlation matrix is 0.4% with respect to the correlations obtained by Monte Carlo simulations. Next the total circuit leakage is calculated from this matrix and cells leakage means and variances. The accuracy and efficiency of the approach is demonstrated on a C3540 (8 bit ALU) ISCAS85 Benchmark circuit.

#### I. INTRODUCTION

As silicon industry is moving towards smaller and smaller critical dimensions, controlling device parameters during fabrication is becoming a great challenge. The variations in channel length, width, oxide thickness and channel doping profiles result in a large variation of the threshold voltage. As the leakage components in a device depend on the transistor geometry and threshold voltage, statistical variation of those parameters leads to a significant spread of the total leakage. This increased variability in advanced CMOS technologies is playing an increased role in determining the total leakage of a chip. This has accentuated the need to statistically account for leakage variations during the design cycle [1]. Designing for worst case leakage may cause excessive guard-banding, resulting in lower performances. Moreover, underestimating leakage variations can reduce the yield, as dies, violating the product leakage requirements, should be discarded.

In the past years, several works have focused on the problem of accurate prediction of leakage in digital circuits in the presence of variations. The previously proposed statistical leakage analyses approaches can be classified in three main groups. The first set of techniques approximate the transistor leakage currents with empirical equations (whose parameter

are found by curve-fitting) or use Taylor expansion series to approximate the logarithmic expression of the leakage current [2-5]. The main drawback of this first group of statistical techniques is that their reliability with respect to manufacturing strongly depends on the correctness of the empiric relations used for the leakage current. The second set of methodologies proposes transistor models (developed simplifying the PSP/BSIM models, elaborating manufacturing data) aware of process variations [6]. About this second group of methodologies, the major disadvantage is that the set of proposed equations needs new coefficients that have to be pre-determined (by fitting SPICE simulations or device extraction data for each library's cell). However, in [7] a novel methodology is proposed to estimate distributions of the leakage current of CMOS circuits in presence of process statistical variations integrated with standard BSIM4 and PSP transistor model. The third group consists of statistical leakage estimation based on Look Up Table (LUT) approaches [8-11]. LUT approach can be further subcategorized in two groups: a first category working at transistor level and second one working at cell level. In [10] is presented a statistical leakage estimation based on LUT of 23 stacks models of P-NMOS transistors in presence of PVT (process voltage temperature) variations combined with Neural Networks.

In this work we propose a solution to estimate the leakage current of larger circuit by modeling each gate for every input vector. This work is based on pre-characterizing library cells, and storing data like leakage mean, variance and correlations in tables. This is done for every input vector of each cell 10].

The rest of the paper is organized as follows. In Section II we describe briefly the motivation for using a Correlation Model. At this stage, we propose an approach to get cells leakage correlations. Section III describes a look up table approach for statistical leakage estimation. Then, in Section IV, we present the results obtained with this approach on the ISCAS 85 benchmark, 8-bit ALU,C3540 circuit, with a complete comparative analysis of our Look Up Table approach with a Monte Carlo approach. Conclusions are presented in Section V.

#### II. CORRELATION MODEL

#### A. Need of Correlation Models

To estimate accurately the full-chip leakage we must take into account the process variability and the inputs state, and the correlations between the different leakages have to be considered and modeled. In general, process variations can be classified into the following categories: inter-die variations are the variations from die to die, while intra-die variations correspond to the variability within a single chip. Inter-die variations affect all the devices on a same chip in the same way, while the intra-die variations may affect devices differently on the same chip. In addition, intra-die variations exhibit spatial correlation, i.e., devices located close to each other are more likely to have similar characteristics than those placed far away. Mathematically, inter-die variations can be regarded as a special case of intra-die variations with a correlation value of one. Under only inter-die variations, as the leakages of all gates or devices are sensitive to the process parameters in similar ways, the circuit performance can be analyzed at multiple process comers using deterministic analysis methods. With intra-die variations, statistical methods must be used to correctly predict the leakage [12].

In literature, to take into account the correlations, [12], [13] have taken into consideration both the effects of gate topologies and within-die spatial correlation. In [13] spatial correlations are modeled using a quad-tree die partitioning method. In [14], a grid model is used and the leakage is determined within a grid by summing a set of correlated lognormal distributions; then the full-chip leakage distribution is found by summing the leakage distributions of each grid. In [6] the correlation model is found by fitting the cell's leakage into a functional form to get three fitting parameters (a, b, c). Using these parameters, the leakage mean and standard deviation are analytically obtained. The fitted parameters also allow determining the leakage correlation between any pair of gates, given the channel length correlation .All these proposed methods, based on correlation models are complex for large circuits. In this paper, we propose a simpler approach to take into account the correlations, considering the inter and intra die variations.

#### B. Correlation matrix

The correlation is the degree to which two or more quantities are linearly associated. Given any pair of components, Xi and Xj, we denote their correlation as either cor(Xi,Xj) or  $\rho$  i,j. This Correlation is defined as

$$\rho_{i,i} = cov(Xi,Xj) / (\sigma_i \sigma_i) \tag{1}$$

where  $\sigma$  i and  $\sigma$  j are the standard deviations of Xi and Xj.

As with covariance, we can summarize all the correlations of a random vector X with a symmetric correlation matrix,

which gives the correlation coefficients between any pair of components:

$$\mathbf{p} = \begin{pmatrix} \rho_{1,1} & \rho_{1,2} & \rho_{1,3} & \cdots & \rho_{1,n} \\ \rho_{2,1} & \rho_{2,2} & \rho_{2,3} & & & \\ \rho_{3,1} & \rho_{3,2} & \rho_{3,3} & & \vdots \\ \vdots & & & \ddots & \\ \rho_{n,1} & & \cdots & & \rho_{n,n} \end{pmatrix}$$

Figure 1. Correlation Matrix

To build this correlation matrix for a digital circuit we successively find out the correlation between the leakages of all standard library cells present in the circuit under study. We can use the following approaches

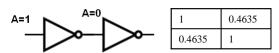

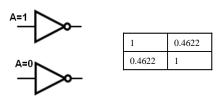

The simpler approach is to simulate the circuit and extract the leakage of each cell using Monte Carlo (MC) electrical simulations, and import the data from Monte Carlo to get the correlation matrix. This approach is not feasible for a big circuit, but will be used as a reference in this work. As an example, we used a small circuit made up of two inverters connected in series, we performed MC simulation on this circuit, extracted the leakage of each inverter and then calculated the correlation matrix shown in fig. 2.

In this work, we propose to use MC on single independent cells, including all input states combinations. We illustrate this approach with the two inverters as shown in fig. 3. We performed MC simulation on these two inverters (no connection between inverters), extracted the leakage of each inverter and then calculated the correlation matrix shown in fig. 3. If we compare the correlation matrix obtained from first and second approach we see that second approach gives 0.28% relative error with respect to correlation obtained from first approach i.e. Monte Carlo.

Figure 2. Schematic for First Approach and correlation matrix using MC

Figure 3. Schematic for Second Approach and correlation matrix using MC on single independent cells

We get similar correlation factors for Fig. 2 and Fig. 3 because gate leakage is negligible in 32nm high k metal technology, compared to other sources like sub threshold leakage, GIDL, DIBL. Thus cells can be considered as high impedance input devices, and their interconnections have a negligible impact.

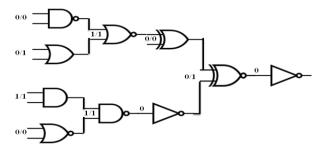

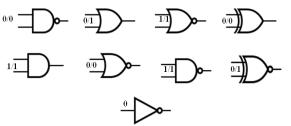

We verified this approach on another schematic which consists of 10 cells (fig. 4a). We performed a 10,000 runs Monte Carlo simulation on the split schematic (fig. 4b) and we found similar results of approximately 0.4% of relative error

with respect to full-circuit Monte Carlo simulation extracted correlation coefficients.

Figure 4a. Schematic A: Circuit with 10 gates

Figure 4b. Schematic for Second Approach for correlation matrix for Schematic A: Circuit with 10 gates

One major advantage of this approach is to limit the size of the simulations, as two identical cells will be replaced by a single instance. Therefore, it is compatible with a full standard cell library pre-characterization.

#### III. LEAKAGE ESTIMATION METHODOLOGY

Again, Monte Carlo will be used as a reference for this work. In this study leakage estimation is performed on technology mapped ISCAS circuits, which consist of fixed sets of cells. In order to enable a fast and efficient estimation, some information is pre computed for each cell of the library and stored in look-up tables. We also used the correlation matrix created for our leakage estimations.

#### A. Look Up Table Method at Cell Level

Look Up table approach involves the characterization of the mean ( $\mu$ ), variance ( $\sigma^2$ ), and correlation ( $\rho$ ) of leakage of each cell for each input state. To build each cell table (leakage mean and variance for each input state), we performed 10,000 simulations of Monte-Carlo Process Variations (MC-PV) at temperature (T=125C). In the MC-PV all process parameters are considered independents of each other and the variations are considered Gaussian with a deviation of  $\pm 3~\sigma$  around of their nominal value. In addition, the correlation matrix is built as previously described.

Table1 summarizes the content of the cells LUT.

Table 1. Content of Look Up table for Pre Characterized Cell

|             | A   |     | В   | <br>Z    |

|-------------|-----|-----|-----|----------|

| Cell Name   | INV | INV | AND | <br>NAND |

| Input state | 0   | 1   | 00  | <br>1111 |

| Mean        |     |     |     |          |

| Variance    |     |     |     |          |

The mean ( $\mu$ ) of the entire circuit is calculated as the sum of all mean's of all independent cells for a specific input state.

The variance ( $\sigma^2$ ) of the entire circuit is calculated by taking the sum of all variance of each pre-characterized cell. For e.g. if there are two cells X and Y then the variance will be

$$\sigma^2 \left( I_{Leak} \right) = \sigma^2_X + \sigma^2_Y + 2\rho_{XY} \sigma_X \sigma_Y \tag{2}$$

We explored this approach for the C3540 ISCAS 85 benchmark circuit.

### IV. LEAKAGE ESTIMATION OF A SIMPLE CIRCUIT AND THE ISCAS C3540 CIRCUIT

In this section we present the results of the leakage estimation for the schematic A shown in figure 4 and for ISCAS 85 C3540 circuit, with a detailed comparison between Monte Carlo and the LUT approach.

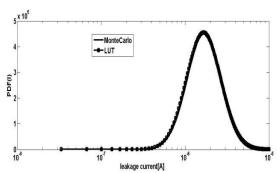

Figure 5. Comparison of MC and LUT approach for Circuit with 10 gates i.e. Schematic A, PDF normalized by area, X axis (log scale): leakage current [A], Y axis: PDF(I)

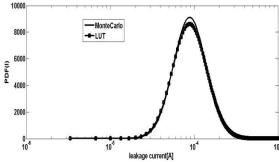

Figure 6. Comparison of MC and LUT approach for C3540 ISCAS 85 circuit PDF normalized by area, X axis (log scale): leakage current [A], Y axis: PDF(I)

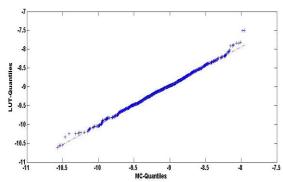

Variance calculated from LUT approach gives accurate results as we are considering the input state of each cell. We show the comparison of MC and LUT in fig. 5 and in fig. 6 for Schematic A and ISCAS C3540 circuit respectively. Detailed comparison for C3540 is shown in fig. 7, Q-Q plot, which compares Monte Carlo quantiles on horizontal axis with LUT quantiles on the vertical axis for ISCAS C3540 circuit. The linearity of the points shows that LUT fits the MC well. From Q-Q plot we can see that blue points are aligned with red points. From fig. 7, we computed that 99.9% of data are accurately mapped (blue line superimposed over red line in Q-Q plot) only 0.1% of data is overestimated by LUT approach, using the cell correlation coefficients.

Figure 7. Normalized Q-Q plot for MC and LUT approach for ISCAS C3540 circuit

As already mentioned one of the major advantage of this approach is to limit the size of the simulations, so by this methodology computational time will be reduced. For ISCAS C3540, Monte Carlo Simulation time was approximately one hr and leakage computation time by LUT approach, with cells correlations, was few seconds.

#### V. CONCLUSION

In this work we propose statistical leakage estimation methodology i.e. Look Up Table approach, taking into account cells leakage correlations. LUT approach is based on pre-characterized library cells and uses the cell leakage correlation factor for total variance calculation. This method had been validated using the ISCAS85 Benchmarks circuit C3540. The maximum relative error is 0.4% for correlation factor for bigger circuits. Also computational time for leakage estimation for bigger circuits is reduced by LUT approach.

#### REFERENCES

- [1] Mohab Anis and Mohamed H. Aburahma, 'Leakage Current Variability in Nanometer Technologies', 9th IDEA Symposium 2005,pp. 60-63.

- [2] R. Rao, A. Srivastava, D. Blaauw, D. Sylvester, "Statistical Estimation of Leakage Current Considering Inter- and Intra Die Process Variation", in IEEE Proc. Int. Symp. Low Power Electronics and Des., 2003, pp. 84-89.

- [3] Mukhopadhyay S. and Roy K., "Modeling and estimation of total leakage current in nano-scaled CMOS devices considering the effect of parameter variation", in Proc. of the international Symposium on Low Power Electronics and Design, 2003, pp. 172-175.

- [4] T. Li, W. Zhang, Z. Yu, "Full-chip leakage analysis in nano-scale technologies: Mechanisms, variation sources, and verification". Design Automation Conference, 45th ACM/IEEE, June 2008, pages .594-599

- [5] Zhigang Hao, Ruijing Shen, Tan, S.X.-D, Bao Liu; Guoyong Shi "Statistical full-chip dynamic power estimation considering spatial correlations", Quality Electronic Design (ISQED), 12th International Symposium, 2011, pp. 1-6.

- [6] Khaled R. Heloue, Student Member, IEEE, Navid Azizi, and Farid N. Najm, Fellow, IEEE," Full-Chip Model for Leakage Current Estimation Considering Within-Die Correlation", Computer Aided Design of Integrated Circuits and Systems, IEEE Transactions in 2009, pp. 874-887.

- [7] C. D'Agostino, P. Flatresse, E. Beigne, M. Belleville, "An Accurate Approach for Statistical Estimation of Leakage Current Considering Multi-Parameter Process Variations in Nanometer CMOS Technologies" in Proc. of ESSDERC 2009.

- [8] A. Ferre, et. al, "Leakage power bounds in CMOS digital technologies" IEEE Trans. on Comp.-Aided Design of IC and Systems, Vol. 21, Issue 6, June 2002, pp. 731-738.

- [9] A. Rastogi, et. al, On Composite Leakage Current Maximization", J. Electron. Test, Vol 24, No. 4, 2008 pp. 405-420.

- [10] J. Viraraghavan, et. al, "Voltage and Temperature Scalable Standard Cell Leakage Models Based On Stack For Statistical Leakage Characterization", VLSID 2008, 4-8 Jan. 2008, pp. 667-672.

- [11] D. Helms, et. al, "Analysis and modeling of subthreshold leakage of RT-components under PTV and state variation", ISLPED06, 2006,pp. 220-225.

- [12] Hongliang Chang and Sachin S. Sapatnekar "Full-chip analysis of leakage power under process variations, including spatial correlations" IEEE Design Automation Conference, 2005,pp.523-528

- [13] Amit Agarwal, Kunhyuk Kang, and Kaushik Roy."Accurate estimation and modeling of total chip leakage considering inter- & intra-die process variations",IEEE International Conference on Computer-aided Design, 2005,pp. 736-741.

- [14] H. Chang and S. S. Sapatnekar. Statistical timing analysis considering spatial correlations using a single PERT-like traversal. In ICCAD, San Jose, CA, November 9-13 2003,pp 621-625.