## Extension des méthodes DFM pour l'industrialisation de produits microélectroniques

Muhammad Kashif Shahzad, Michel Tollenaere, Stéphane Hubac, Ali Siadat

#### ▶ To cite this version:

Muhammad Kashif Shahzad, Michel Tollenaere, Stéphane Hubac, Ali Siadat. Extension des méthodes DFM pour l'industrialisation de produits microélectroniques. 9e Congrès International de Génie Industriel, Oct 2011, Saint-Sauveur, Montréal, Canada. hal-00782413

HAL Id: hal-00782413

https://hal.science/hal-00782413

Submitted on 29 Jan 2013

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **CIGI 2011**

# Extension des méthodes DFM pour l'industrialisation de produits microélectroniques

Muhammad Kashif SHAHZAD <sup>1,2,3</sup>, Michel TOLLENAERE <sup>2</sup>, Stéphane HUBAC <sup>1</sup>, Ali SIADAT <sup>3</sup>

<sup>1</sup> STMicroelectronics, 850 Rue Jean Monnet. 38926 Crolles CEDEX, France muhammadkashif.shahzad@st.com <sup>1,2,3</sup> stephane.hubac@st.com<sup>1</sup>

<sup>2</sup>G-SCOP -- Université de Grenoble Grenoble-INP/ UJF-Grenoble 1/ CNRS UMR5272 Grenoble, F-38031, France michel.tollenaere@grenoble-inp.fr<sup>2</sup>

<sup>3</sup> LCFC

Arts et Métiers Paris Tech, LCFC 4 rue Augustin Fresnel-57078 Metz, France ali.siadat@ensam.fr <sup>3</sup>

#### Résumé -

L'industrie des semi-conducteurs (SMI) est caractérisée par de rapides évolutions sur une courte période de temps. Pour maîtriser les temps de développement (Time to Market) et les montées en cadence (Time-to-Volume), le DFM (Design for Manufacturing) a été intégré dès 1980 dans les outils de conception en tant que stratégie d'atteinte des objectifs de rendement. DFM est ainsi devenu un standard industriel pour estimer le rendement et la fabricabilité dès la conception. Cet article propose une méthodologie DFM pour inclure les résultats des mesures géométriques en corrélation avec les résultats des tests électriques, capturant les capabilités process liées aux performances des produits. L'étude de cas sur la modélisation d'interconnexion est réalisée chez un industriel de haut rang et une méthodologie destinée à aligner rapidement les modèles sur la cible des spécifications est proposée. Le BPR (business process reengineering) et IDEF0 sont utilisés pour définir les workflows qui accompagne la méthodologie proposée; un modèle de données est ainsi mis en œuvre via un outil destiné aux ingénieurs R&D.

#### Abstract -

Semiconductor manufacturing industry (SMI) is characterized by the fastest change in smallest period of time; hence to address time-to-market and time-to-volume challenges, DFM was included in design flow (1980) as a yield enhancement strategy. It has become an industrial standard to assess yield/manufacturability of the design. Test chip is used to validate the geometric stack against resulted specs and models are frozen and distributed to the CAD department for inclusion in design and DFM kits. This paper proposes a DFM methodology to include geometric measurements which could impact significantly electrical test results making it difficult to adapt the target models. It requires site to site mapping on the wafer which is not trivial because wafer center is different than the mask center and the test structures PCS/M (process control/monitoring structure) could be present in the horizontal or vertical scribe lines. A case study on the interconnect modeling is performed in a top ranked SMI and an extended methodology to rapidly align local interconnect models on target the source specs is proposed. BPR (business process reengineering) and IDEFO are used for analysis and newly proposed methodology along with a data model which is implemented in a tool for R&D engineers.

**Mots clés -** conception en vue de la fabrication (CVF), analyse de données d'ingénierie, temps de mise sur le marché, atteinte des volumes, délai d'atteinte de la qualité.

**Keywords** - design for manufacturing (DFM), manufacturing for design (MFD), time to market, (T2M), time to volume (T2V) and time to quality (T2Q), engineering data analysis (EDA)

#### 1. Introduction

L'industrie des semi-conducteurs (SMI) est caractérisée par une fluctuation cyclique de la demande et la loi de Moore qui prédit le doublement du nombre de composants par unité de surface tous les 18/24 mois (TR-IBS, USA). En 2001/2002, l'industrie a été confrontée à une chute de 31% des volumes suivie par 64% de croissance entre 2003 et 2007, elle même suivie d'une chute de 22% en 2009. Malgré ces chutes cycliques, les investissements en R&D n'ont cessé d'augmenter

et devraient atteindre 18% du total des revenus d'ici 2012. Les efforts en R&D sont axés sur le développement de nouvelles plateformes technologiques incluant des méthodes de fabricabilité dans le but de développer la compétitivité. Le DFM a été adopté dans les années 80 comme une stratégie d'amélioration du rendement, mais maintenant le DFM est devenu un outil clé pour la compétitivité.

Le DFM est défini comme la capacité d'évaluer le rendement et la fabricabilité d'un produit dès les premiers stades de la conception (Hermann, 2004), conduisant à une meilleure maîtrise des couts et donc de la compétitivité (Raina, 2006). Les concepts du DFM sont classés en (Mehrabi et al., 2002) "DFM produit" (design de produits manufacturables pour des processus de production définis) et "DFM processus" (processus de développement minimisant les modifications et itérations avec prises en compte précoces des contraintes). Les premières recherches sur le DFM, basées sur des estimations approximatives, visaient à assurer la fabricabilité mais laissaient l'obtention du rendement aux contrôles en ligne de la production (APC/AEC). Cette politique a porté ses fruits jusqu'aux technologies 250mm, mais avec le 300mm, la complexité croissante de la topologie des circuits et la diminution de longueur d'onde lors de la lithographie ont entraîné de nombreux rebuts et des pertes de rendement (Cliff, 2003). "Du point de vue d'un concepteur, les choses deviennent plus difficiles parce que les capabilités-machine issues de la fabrication sont tellement serrées qu'ils ont du mal à trouver les bonnes pratiques de conception" (Peters, 2005).

Le concept de DFM a émergé accompagné d'un foisonnement de termes tels que DFY, DFV et DFT etc, regroupés sous le label DFX visant à la maîtrise des coût, qualité, rendement et délai de mise sur le marché (Anderson, 2006). Pour (Kuo et al., 2001), les outils DFX visent à apporter aux concepteurs, l'information sur la prévisibilité des éléments de cycle de vie. Ces outils s'appliquent directement sur des modèles de CAO et fournissent des conseils sur l'analyse des coûts, l'amélioration de performances du produit (qualitative, quantitative et binaire). Pour (Seino, 2009) les raisons qui peuvent expliquer la mise en œuvre infructueuse du DFM sont le manque de sensibilisation sur l'importance de DFM par les concepteurs de produits et l'analyse erronée des variations lors de la production par les différents d'ingénieurs/managers.

L'industrie des semi-conducteurs (McGregor, 2007) a commencé avec une très forte intégration économique verticale comme un dispositif intégré (IDM) qui conçoit, fabrique et commercialise les équipements et les produits microélectroniques ; mais au milieu des années 70, la fabrication d'équipements et la conception/production des wafers se sont séparés avec des finalités industrielles distinctes. A la fin des années 1980, l'idée d'une industrie sans fabrication (fabless) a émergé afin de concentrer les ressources capitalistiques sur l'innovation de nouveaux modèles plutôt que sur des équipements de fabrication à obsolescence rapide.

Pour rester compétitives, (Morinaga et al., 2006), les SMI ont besoin de mettre les produits sur le marché rapidement avec un rendement de production maitrisé, alors que les durées de vie des produits sont de plus en plus courtes et qu'on observe un déclin rapide des prix de vente. L'évolution des SMI poussée par la compétitivité soutenue s'appuie sur les plates-formes technologiques, l'équipement et les matériaux. Le DFM joue un rôle important dans le développement technologique et l'amélioration continue de processus de fabrication. Les coûts de maîtrise d'une technologie sont en constante augmentation : pour la plateforme 32 nm, un cout de 7 milliards de dollars est escompté (Web 2008). Chaque nouvelle technologie devrait voir un doublement de densité de transistors accompagné d'une capacité de montée en cadence rapidement avec une diversité de produits (axés sur les règles DFM). INTEL company a autorisé l'évolution des règles de conception et l'étude a montré que la quasitotalité des règles de conception a été modifiée avant la production de série afin d'assurer le rendement le plus élevé; par conséquent, au cours du prototypage, les règles de conception (DFM) doivent pouvoir changer si nous voulons une rapide montée en cadence des volumes de production.

Sur la base des faits énoncés ci dessus, il est bien évident que le DFM a pris une place importante à l'articulation de la conception et de la production en tant qu'outil méthodologique clé. Pour partager les coûts de R&D, l'industrie microélectronique constitue des "jointventure" pour le développement des plateformes technologiques ; ce

changement stratégique permet de réduire le temps de déploiement et le coût d'une plate-forme technologique, mais met sous pression la production pour adopter les modèles issus du DFM délivrés par une alliance. Dans cet article, nous proposons une méthodologie étendue basée sur DFM pour le développement d'interconnexions pour identifier, estimer et corriger les sources de variation.

Cet article est divisé en 4 parties. La première présente une synthèse des concepts de DFM, des difficultés rencontrées par l'industrie et de mettre en évidence la nécessité d'une approche rigoureuse pour le modèle DFM. La seconde partie présente le processus de modélisation et l'approche utilisée par l'industrie pour aligner / développer des modèles de référence. La partie 3 propose une méthodologie DFM étendue en ajoutant un contrôle supplémentaire des corrélations entre tests géométriques et électriques. Elle est soutenue par un diagramme de classes UML du système et est mise en œuvre en tant qu'outil pour les ingénieurs R&D. Enfin la partie 4 conclut l'article en discutant les résultats obtenus et les perspectives.

#### 1 MODÉLISATION DES INTERCONNECTIONS

Schématiquement, les circuits électroniques sont constitués de transistors fabriqués sur chaque plaquette de silicium et reliés par un réseau de câblage (couches d'interconnexion en métal). La taille standard des plaquettes est aujourd'hui de 300nm de diamètre, une taille couramment utilisée aujourd'hui avec la technologie CMOS (Complementary Metal Oxide Semiconductor) ; cette technologie nécessite plus de 400 opérations et environ 8 semaines de traitement.

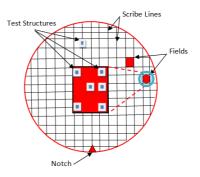

Commençons par la description de la plaquette (Fig.1) : elle est fabriquée à partir de silicium et est divisée en lignes horizontales et verticales qui sont connues sous le nom de lignes de découpe. Ces lignes ont un double objectif au cours du processus de fabrication, d'abord elles contiennent des structures de test (PCS: structures de contrôle, PCM: moniteurs de contrôle de processus et PMB: boîte de surveillance de processus) et sont utilisées lors des mesures électriques à différentes étapes du flux de production. À la fin du processus de production, la plaquette est découpée le long des lignes de découpe pour séparer les puces. Ces puces sont emballées et expédiées chez le client. Le "notch" est une coupe dans la plaquette utilisée pour identifier la position de référence au cours du processus. Les formes rectangulaires résultant de l'intersection des lignes horizontales et verticales constituent ce qui peut être un circuit complet (SoC: System on Chip) ou un composant. Afin de mesurer les variations d'épaisseur, des structures de test peuvent être placées dans la plaque à différentes positions comme le montre la figure 1. Il faut noter que les circuits réels ne sont pas testés jusqu'à ce que le test final soit effectué sur le produit. Les tests en ligne sont représentatifs du produit et sont utilisés pour surveiller et mesurer des mesures électriques et géométriques au cours du processus de fabrication.

Fig.1 description des tranches de 300 mm de diamètre

Le processus de fabrication est divisé en étapes amont ou front-end (FE) et étapes aval ou back end (BE). Le Front End est constitué par la fabrication de transistors sur une surface de silicium et 1-9 couches de métal dans une plaquette de silicium pour l'interconnexion. Au cours de chaque étape, les dimensions géométriques sont mesurées et contrôlées à travers des cartes de contrôle pour assurer le meilleur rendement paramétrique. Le premier test électrique (PT) est effectué pour mesurer les performances électriques (R, C et RC). L'objectif principal de l'analyse de la variance des caractéristiques dans le Back End (BE) est d'analyser de localisation en localisation, de plaquette en plaquette et de lot en lot, la corrélation spatiale et de classer les variations significatives, systématiques ou aléatoires. Notons que les plaquettes R&D ne comprennent pas de structures de test : aussi des domaines géométriques sont ils identifiés HG (en haut à gauche), HD (en haut à droite), C (Centre), CD (centre droit), BD (en bas à droite) et BG (en bas à gauche). La direction de ces éléments est essentielle pour la détermination du rendement fonctionnel de la plaquette.

Pour conserver une surface de la puce aussi constante que possible, les dimensions des lignes et des portes diminuent d'un facteur 2 tous les 2 ans augmentant ainsi la densité de circuits sur une plaquette. Parce que les périphériques sont connectés par le biais des interconnexions, l'augmentation de la densité augmente la longueur des interconnexions.

Les interconnexions sont des pistes de métal déposé ; elles présentent donc une résistance électrique et sont des causes de retard du signal. De même les interconnexions métalliques sont séparées par un diélectrique ayant un potentiel de condensateurs, de sorte que ces grandeurs parasites (résistance/capacité) doivent être modélisées sous peine de risque d'échec du produit final. Les ingénieurs R&D sont confrontés au défi d'adapter les spécificités locales d'interconnexion avec celles connues au sein d'une alliance d'industriels (DFM à l'échelle d'une filière industrielle).

#### 2.1 PLATEFORME TECHNOLOGIQUE 'FONCTIONS ET USAGES'

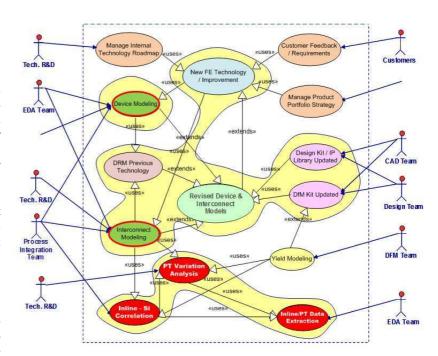

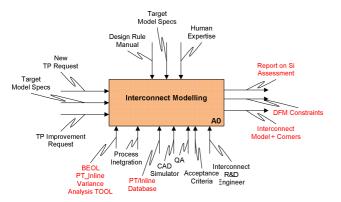

Le concept de *plate-forme technologique* dédiée à une taille de gravure (22, 32 nm par exemple), et l'utilisation d'une bibliothèque standardisée de cellules fonctionnelles constituent les clés de la compétitivité. Nous présentons, en formalisme UML, les "cas d'utilisation" destinés à la mise en place des concepts informationnels du DFM étendu présenté dans cet article. Cette analyse a servi de base pour le déploiement logiciel qui a permis de valider la pertinence de l'approche chez un grand industriel du semi-conducteur (Fig.2).

Les équipes directement impliquées dans ce processus sont l'intégration des procédés, la R&D, la modélisation de dispositifs et d'interconnexion ; elles focalisent leurs efforts vers le développement/amélioration de la *plateforme technologique* (32nm, 22nm, 40nm) qui sert de base pour les nouveaux modèles.

Les modèles de fonctions (*devices*) et d'interconnexion définissent l'interaction entre la conception et la fabrication, mais ils sont élaborés en utilisant des simulations de CAO et sont validées sur la base des résultats de tests électriques (dits Parametric Tests ou **PT**). Les principales étapes dans le

Fig.2 Les "cas d'utilisation" de la plateforme technologique

développement d'une plate-forme technologique commencent par la définition des valeurs cibles sur les principaux paramètres critiques. Une liste de paramètres physiques est élaborée en conformité avec le manuel des règles et bonnes pratiques de conception (dit Design Rules Manual **DRM**); les valeurs sont simulées et itérées jusqu'à la cohérence du modèle avec les spécifications du design. L'objectif est d'identifier la séquence des interconnections pour chaque couche de métal en utilisant les connaissances existantes qui comprennent le DRM précédent (manuel des règles de conception), l'expertise humaine et des données issues de la production. Pour chaque nouveau produit, chaque couche de métal doit être simulée dans le simulateur SPICE ainsi que' l'empilement des couches pour être enfin testé et comparé par rapport aux résultats d'essais (capacité, résistance). La dernière étape est la comparaison des résultats obtenus par prototypage dans la 'fab' avec ceux de simulation. Les modèles finaux sont alors traduits en 'kit de conception' intégré aux outils de CAO. Les équipes de développement se concentrent sur l'identification des variations systématiques en production afin d'enrichir le 'kit **DFM'** par les contraintes induites sur la conception.

Nos efforts se sont concentrés sur la modélisation des interconnexions et ont identifié trois principales sous-fonctions en vue d'une extension de la méthode DFM ; la méthode nécessite les résultats de mesure électriques (metal) et géométriques (processus) sur les lignes de découpe. Chaque mesure doit être identifiée par sa localisation (x, y) afin de permettre les corrélations par localisation. Jusqu'à présent, les ingénieurs R&D ont porté les corrélations sur les résultats des tests électriques, car ils ne pouvaient pas établir une cartographie basée sur les localisations (x, y) entre les résultats des mesures électriques et géométriques. Au cours des mesures électriques, la position de l'encoche (fig. 1) est orientée pour aligner la structure de test dans le sens horizontal et vertical avec le testeur. Les coordonnées lors des mesures électriques entraînent les coordonnées sont "normalisées" avant d'être transférées à la base de données à des fins de corrélation PT-

#### 2.2 PROCESSUS DE MODELISATION DES INTERCONNECTIONS

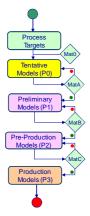

Les modèles d'interconnexion sont des équations physiques complexes qui prennent en entrée les caractéristiques des lignes métalliques, comme la largeur, l'épaisseur, la nature du matériau, le sens de dépôt, la rugosité ... et le contexte pour calculer la résistance et la capacité résultantes. Le processus générique de modélisation des interconnexions est présenté cidessous (Fig.3):

Fig.3 Processus de modélisation des interconnections

La cible de résistance et de capacité est fournie par l'équipe de Process Integration (PI). La liste des valeurs cible est définie en utilisant le DRM, l'expertise humaine et un modèle type qui est simulé et validé par rapport aux limites des spécifications. Si des divergences apparaissent, la liste est itérée en étroite collaboration avec l'équipe d'intégration processus jusqu'à ce que les résultats de simulation soient dans les spécifications. Cette étape suit la définition du modèle de "bord de plaque" qui sont validées par l'objectif du modèle de simulation. La liste des paramètres de définition est la sortie du processus (P0) à partir de simulations CAD. Une fois le modèle approuvé, une plaquette d'essai est préparée pour vérification physique dans la ligne de production afin d'évaluer la production en terme de qualité et volume. Lors de l'évaluation de ces règles sur les prototypes physiques, des règles DFM ou contraintes supplémentaires pourraient être identifiés et ajoutés au manuel DRM. La dernière étape est la documentation où le DRM pour le modèle est figé et les modèles numériques sont envoyés pour être ajoutés à l'ensemble pour la conception des kits. Après cette étape, bien que les modèles puissent encore être améliorés avec la dispersion, les concepteurs ne permettent généralement pas le changement dans les règles du manuel de conception ou dans les modèles de bords de plaque.

Voici les principales observations formulées lors de l'analyse:

- l'extraction de données avec des filtres prédéfinis est une pratique courante, d'où des données antérieures à l'extraction qui sont déjà normalisées et aucune corrélation significative ne peut conduire à la source des variations : les résultats peuvent être trompeurs

- les ingénieurs travaillent avec des feuilles Excel de 8 Mo et plus, taille qui non seulement exigent des ressources supplémentaires, mais pour lesquelles il est très difficile de traiter, d'harmoniser, de prétraiter et de dégager des analyses précises.

- l'erreur humaine est hautement probable dans ces traitements, ce qui conduit à des interprétations erronées.

- plusieurs outils sont utilisés pour établir une analyse des flux acceptée comme il est défini dans les produits appelés «flux

- de référence de calcul", où les étapes de conception et de simulation ainsi que les outils sont décrits sous forme de flux "en or". Cette stratégie peut s'avérer très trompeuse dans le cas de grande quantité des données à analyser et interpréter.

- la dispersion sur les caractéristiques fonctionnelles des circuits ne sera pas réduite par le fait que de bonnes corrélations existent et que les données électriques s'avèrent se conformer à des distributions "normales".

#### 2.3 CORRELATIONS INTER-LOCALISATIONS

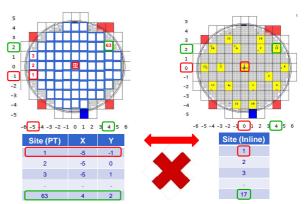

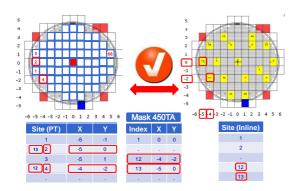

Aucune amélioration importante ne peut être envisagée sans que des corrélations inter-localisations sur les mesures en ligne et les tests électriques sur la plaquette soient faites, parce que les résultats électriques sont directement influencés par les caractéristiques géométriques relevées sur la plaquette. Observons cette question par un exemple (Fig. 4). Il a été admis que les résultats électriques dans la base de données sont affectés à des coordonnées x, y, qui sont normalisés par rapport à l'orientation de la plaquette pendant les essais. Le centre de la plaquette avec l'encoche en position «haut» est pris comme référence 0,0 et dans toutes les autres zones, les coordonnées sont calculées sur la base de ce point de référence. Un index de localisation variant de 1 à n est affecté à chaque localisation par déplacement de bas en haut et de gauche à droite, par exemple loc1 a x, y (-5, -1) et loc63 à (4,2). Dans la base de données en ligne l'index de localisation n'est pas présent mais la référence est toujours 0,0 au centre. Il n'est donc pas possible d'associer des coordonnées aux numéros d'index de localisation.

Fig.4 Problème de corrélation inter-localisations

#### 2.4 NORMALISATION DES CORRELATIONS INTER-LOCALISATIONS

Afin de permettre d'améliorer les corrélations entre étapes successives du process, une classe *Mask* a été créée dans le modèle de données (Fig. 5) ; cette classe permet d'établir un lien pour la cartographie des coordonnées entre tests paramétriques PT et bases de données en ligne. Sur la plaquette de gauche de la Fig.5, nous disposons de données PT avec des coordonnées x, y normalisées tandis que sur la plaquette droite les données en ligne ne sont identifiées qu'à l'aide de l'indice de localisation. Un utilitaire défini comme une méthode de la classe *Mask* et *Mask\_Sequence* permet de corréler les localisations des différentes mesures géométriques et électriques effectuées sur des machines différentes.

Fig.5 Solution de corrélation inter-localisations

#### 3. PROPOSITION D'EXTENSION DE LA METHODOLOGIE DFM

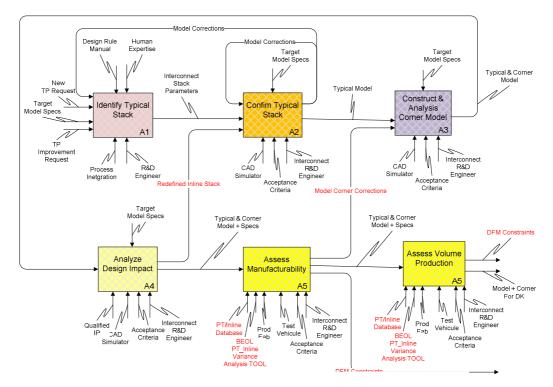

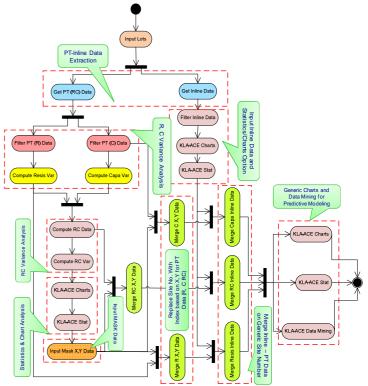

Les principaux constats mis en évidence lors de l'analyse des processus de la section 2-2 montre l'intérêt d'une méthode basée sur un DFM étendu et s'appuyant sur un triangle Données-Méthode-Statistique (DMS), qui est décrit ci dessous en IDEF0. Tel que discuté dans les sections 2.1 et 2.2, le s valeurs moyennes sont calibrées sur la base des résultats de simulation validés par les résultats des tests électriques. La corrélation PT-PT avec la localisation sur la plaquette est possible ; les résultats des mesures électriques sont pris en charge par la normalisation des coordonnées x, y, mais la corrélation PT-ligne avec une localisation est très demandée par les ingénieurs R&D. En l'absence de coordonnées x, y pour les mesures en ligne, il n'était pas possible de la fournir. Cet article présente un modèle de données qui recueille la localisation des coordonnées x, y pour le masque associé avec le produit pour des mesures en ligne. L'outil d'analyse de variance Back End Off Line (BEOL) PT-Inline est conçu pour faciliter aux ingénieurs R&D l'analyse des variations PT, mais aussi la cartographie PT-ligne. Le modèle IDEF0 de la méthodologie proposée est présenté sur la (Fig.6):

Fig.6 IDEF0 pour la proposition d'extension de DFM

Le détail de l'IDEF0 est présenté Fig.7. Les flèches rouges montrent la contribution additionnelle au système actuel dont les flèches noires représentent les éléments actuellement utilisés avec Excel. Le modèle proposé prévoit pour l'utilisateur final la possibilité d'analyser les résultats des tests électriques et de générer des rapports d'essai. D'autres ingénieurs R&D ont accès à la cartographie PT-ligne selon localisation pour la corrélation avancée afin d'identifier mieux les sources de variation au sein du processus.

Le modèle géométrique et physique de la plaquette (*Interconnect stack parameters*) comporte la définition de toutes les dimensions géométriques comprenant le matériau et

les tolérances qui peuvent influer sur la simulation du modèle cible qui permet d'analyser les caractéristiques électriques. Ce modèle géométrique et physique est celui utilisé dans la simulation CAO pour valider la simulation SPICE par rapport aux spécifications. Le modèle géométrique et physique est issu d'un long processus itératif (A1) et/ou (A2) ponctué de changements mineurs afin que la simulation SPICE confirment les paramètres cible. L'activité (A3 - Construct and analyse corner Model) définit les limites admissibles à partir de simulations CAD, pour les circuits les plus lents et les plus rapides. Avant d'envoyer vers la base de test de validation les résultats de la simulation, l'activité (A4 Analyse Design Impact) propose l'analyse d'impact de la conception où un produit qualifié est sélectionné dans la bibliothèque et simulé en utilisant les limites admissibles en utilisant le simulateur SPICE. La procédure (A5) permet d'évaluer la fabricabilité de la composante Silicium. À ce stade, des mesures électriques autorisent l'analyse les variations du modèle rapport à l'objectif et les spécifications limites. Si les résultats sont bien centrés et dans les limites de dispersion, l'activité (A6 - Estimation du rendement de production) peut être lancée.

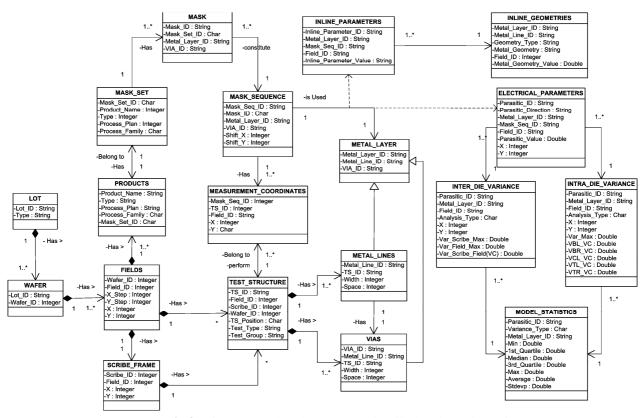

DMS Triangle s'appuie sur le diagramme de classes (Fig.8) pour soutenir la méthodologie proposée. Le même diagramme a été utilisé pour la réalisation d'une base de données relationnelle utilisée par les ingénieurs R&D avec l'outil d'analyse de la variance BEOL. Le diagramme de classes est divisé logiquement en trois parties pour mieux structurer les fonctionnalités du système. La première partie du modèle permet de mettre en place des corrélations de localisation pour des mesures électriques et en ligne sur toutes les plaquettes dans un lot ou de plusieurs lots. Les ingénieurs peuvent directement utiliser les mesures sans avoir à se soucier des positions x - y des points mesurés.

Pour décrire le diagramme de classes fig 8, un lot de production est composé de plusieurs plaques (25 plaques dans le cas d'étude) et chaque plaque comporte plusieurs localisations. Toutes les localisations sont entourées par un périmètre (scribe frame), et les localisations et les périmètres contiennent les structures de tests (TS). La position de la structure de test sur le périmètre est alignée sur une ligne horizontale ou verticale. Le but est d'analyser la variance des caractéristiques électriques d'une localisation à une autre. Chaque produit est réalisé à l'aide d'un ensemble de masques, la fabrication de chaque couche métallique mobilisant une séquence particulière de masques parmi l'ensemble précédent. Chaque couche métallique est identifiée par le numéro de métal et la "via" qui est utilisée pour relier deux métaux. Chaque masque a ses coordonnées x, y décalées par rapport au centre de la plaquette et on utilise de décalage pour calculer les coordonnées de chaque localisation imprimé sur la surface de la plaquette. Un algorithme d'optimisation tourne pour identifier les 17 localisations pour faire la mesure avec l'hypothèse que la structure de tests représente la configuration du produit dans une localisation. Le choix des 17 localisations est fait par les experts et sont les mêmes pour tous les produits. « measurement coordinates » classe contient coordonnées x, y de chaque mesure. Les mesures géométriques collectées sont reliées à la couche de métal et au masque. Les paramètres mesurés sont utilisés pour calculer largeur et épaisseur de chaque piste métallique.

Fig.7 Modèle IDEF0 détaillé pour l'outil d'analyse de variance BEOL

Fig.8 Diagramme de Classes pour l'outil d'analyse de variance

Grâce à ce modèle, les mesures en ligne avec leurs coordonnées x, y normalisées ont pu être corrélées avec les mesures électriques. De la même façon, les paramètres électriques classés par capacité et résistance sont liés à une couche de métal et au masque. Ainsi l'analyse de variance par rapport aux mesures électriques est réalisée pour identifier les déviations significatives.

La corrélation entre les mesures en ligne et les mesures électriques localisation par localisation peut être exploitée afin de déterminer les causes de déviation. Ce diagramme de classe et le modèle IDEF0 ont été implémentés comme une application en utilisant le langage de programmation VB6.0 et une base de donnée relationnelle MS Access 2007. Le temps de calcul s'est avéré coûteux (2 heures) pour un fichier de 4 422 enregistrements de données de résistance et capa, alors cette base de donnée relationnelle a été transférée dans une base de donnée multidimensionnelle et le temps de calcul a été réduit de 2 heures à 5 minutes.

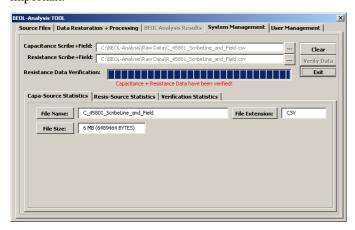

Un applicatif «Outil d'analyse de variance BEOL» a été développé (Fig.10) pour les ingénieurs en R&D. Après

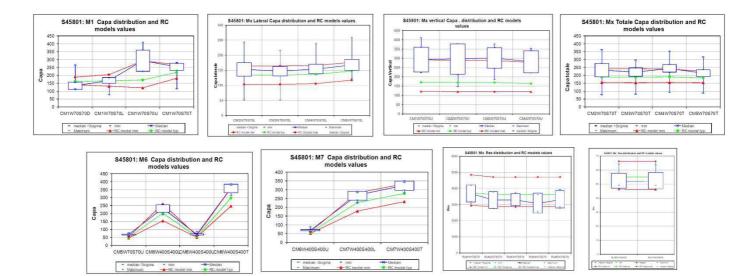

vérification, l'utilisateur est invité à importer les données de feuilles Excel (résistance, capa et les mesures géométriques) dans la base multidimensionnelle, tout en ayant la possibilité d'appliquer les filtres LSL-USL (limite de spécifications) ou LVL-UVL (limite de validation). Après traitement, le résultat final (analyse de variance) est sauvegardé dans des fichiers avec d'éventuels graphiques au choix de utilisateur. Le résultat met en évidence la déviation et la corrélation avec les mesures géométriques : cette étape est particulièrement critique parce que les limites de chaque paramètre doivent être définies in fine. Si les limites n'englobent pas les valeurs cible, des itérations sont enclenchées. L'applicatif fournit une option à l'utilisateur de choisir les algorithmes de calcul programmé. Les diagrammes de Box-Whisker confirment que capa et résistance calculés avec le filtre LSL-USL sont biaisés; néanmoins il n'y a pas de variation dans le calcul lorsque les fonctions programmées sont utilisées. Une réponse possible peut être qu'on a calculé seulement des statistique descriptives alors qu'avec une statistique prédictive, l'impact serait plus important.

Fig.9 Outil d'analyse de variance BEOL

Le flux de travaux usuel pour l'outil développé est présenté sur la Fig.10. On commence par analyser les variances de résistance R, de capacité C et enfin du produit R\*C suivi par le calcul des statistiques et l'élaboration du graphique. L'étape suivante est d'appliquer la normalisation aux coordonnées des localisations afin de faire la corrélation de localisation à localisation. L'option de réaliser une modélisation prédictive est implémentée dans l'outil KLA-ACE, un outil très connu dans l'industrie microélectronique pour les analyses statistiques avancées.

#### 4. RESULTATS, CONCLUSIONS ET PERSPECTIVE FUTURE

Le résultat principal obtenu par l'applicatif BEOL (voir figure Fig. 11 (a)(b)(c)) est de fournir une option d'appliquer les limites comme un filtre, également pour les ingénieurs de R&D et modélisation. Après analyse du résultat, il a été montré que les limites LVL-UVL n'ont aucun influence mais les filtres LCL-UCL et LSL-USL doivent être utilisés, avec attention parce que ils ont une influence forte sur le calcul des statistiques. Box-Whisker plot utilisé pour l'analyse graphique de variance est choisi parce qu'il montre non seulement la dispersion et les quartiles mais aussi la forme de la distribution.

Fig.10 Workflow pour l'outil d'analyse de variance

Comme nous disposons de 4 422 mesures, on pourrait, en application du théorème central limite facilement faire l'hypothèse que les données suivent une loi normale. On propose que pour tous les lots R&D, on ajoute une plaquette de référence dans les étapes des mesures qui valide l'équipement et aussi les mesures faites. Cet article est centré sur l'industrie microélectronique qui est caractérisée par les changements

|       |              |                  | No Limits Filter     |          |        |        |         |                    |         |         |        |                     |        |       |         | LSL-USL Filter |       |                    |         |        |        |                     |      |      | LVL-UVL Filter |         |                    |       |       |       |      |         |       |       |       |

|-------|--------------|------------------|----------------------|----------|--------|--------|---------|--------------------|---------|---------|--------|---------------------|--------|-------|---------|----------------|-------|--------------------|---------|--------|--------|---------------------|------|------|----------------|---------|--------------------|-------|-------|-------|------|---------|-------|-------|-------|

| 36    | Layer_ID     |                  | Programmed Functions |          |        |        |         | Built in Functions |         |         |        | Programed Functions |        |       |         |                |       | Built in Functions |         |        |        | Programed Functions |      |      |                |         | Built in Functions |       |       |       |      |         |       |       |       |

|       |              | Cou              | int µ                | Me       | dian   | σ      | Min     | Max                | μ       | Median  | σ      | Min                 | Max    | Count | μ       | Median         | σ     | Min                | Max     | μ      | Median | σ                   | Min  | Max  | Count          | μ       | Median             | σ     | Min   | Max   | μ    | Median  | σ     | Min   | Max   |

|       | CM1W70S70D   | 442              | 21 134               | .73 133  | .06    | 7.67   | 113.36  | 266.02             | 134.725 | 133.06  | 7.672  | 113.36              | 266.02 | 599   | 147.846 | 145.065        | 7.201 | 141.57             | 188.304 | 147.85 | 145.07 | 7.201               | 142  | 188  | 4421           | 134.725 | 133.06             | 7.672 | 113.4 | 266   | 135  | 133.06  | 7.672 | 113.4 | 266   |

|       | CM1W70S70L   | <u>a</u> 442     | 22 167               | .81 167  | .54    | 6.21   | 77.27   | 185.24             | 167.814 | 167.535 | 6.21   | 77.274              | 185.24 | 4421  | 167.834 | 167.535        | 6.059 | 137.61             | 185.242 | 167.83 | 167.54 | 6.059               | 138  | 185  | 4422           | 167.814 | 167.54             | 6.21  | 77.27 | 185.2 | 168  | 167.535 | 6.21  | 77.27 | 185.2 |

|       | CM1W70S70U   | ў <sub>441</sub> | 17 297               | .66 293  | .35    | 22.24  | 223.24  | 411.05             | 297.663 | 293.347 | 22.235 | 223.24              | 411.05 | 2147  | 277.896 | 279.069        | 8.687 | 223.24             | 292.111 | 277.9  | 279.07 | 8.687               | 223  | 292  | 4417           | 297.663 | 293.35             | 22.24 | 223.2 | 411.1 | 298  | 293.347 | 22.24 | 223.2 | 411.1 |

| 1 [   | CM1W70S70T   | 442              | 23 256               | .39 254  | .89    | 7.52   | 115.52  | 282.75             | 256.394 | 254.892 | 7.519  | 115.52              | 282.75 | 4202  | 255.601 | 254.453        | 6.107 | 211.8              | 269.481 | 255.6  | 254.45 | 6.107               | 212  | 269  | 4423           | 256.394 | 254.89             | 7.519 | 115.5 | 282.7 | 256  | 254.892 | 7.519 | 115.5 | 282.7 |

| ١.    | CM2W70S70L   | 공 306            | 14 152               | .97 152  | .73    | 7.26   | 51.76   | 243.72             | 152.969 | 152.728 | 7.263  | 51.762              | 243.72 | 29394 | 152.588 | 152.461        | 5.39  | 103.98             | 164.367 | 152.59 | 152.46 | 5.39                | 104  | 164  | 30614          | 152.969 | 152.73             | 7.263 | 51.76 | 243.7 | 153  | 152.728 | 7.263 | 51.76 | 243.7 |

|       | CM3W70S70L   | ± 309            | 04 147               | .13 147  | .19    | 5.34   | 51.81   | 215.82             | 147.127 | 147.192 | 5.335  | 51.809              | 215.82 | 30831 | 147.233 | 147.195        | 4.14  | 103.95             | 164.346 | 147.23 | 147.2  | 4.14                | 104  | 164  | 30904          | 147.127 | 147.19             | 5.335 | 51.81 | 215.8 | 147  | 147.192 | 5.335 | 51.81 | 215.8 |

|       | CM4W70S70L   | हुँ<br>309       | 46 154               | .32 153  | .98    | 5.27   | 138.82  | 238.86             | 154.323 | 153.982 | 5.271  | 138.82              | 238.86 | 30577 | 154.148 | 153.897        | 4.991 | 138.82             | 166.047 | 154.15 | 153.9  | 4.991               | 139  | 166  | 30946          | 154.323 | 153.98             | 5.271 | 138.8 | 238.9 | 154  | 153.982 | 5.271 | 138.8 | 238.9 |

|       | CM5W70S70L   | 309              | 50 167               | .54 168  | .07    | 5.99   | 122.04  | 258.16             | 167.54  | 168.072 | 5.993  | 122.04              | 258.16 | 29615 | 166.996 | 167.743        | 5.41  | 122.04             | 176.789 | 167    | 167.74 | 5.41                | 122  | 177  | 30950          | 167.54  | 168.07             | 5.993 | 122   | 258.2 | 168  | 168.072 | 5.993 | 122   | 258.2 |

|       | CM1W70S70U   | 441              | 17 297               | .66 293  | .35    | 22.24  | 223.24  | 411.05             | 297.663 | 293.347 | 22.235 | 223.24              | 411.05 | 2147  | 277.896 | 279.069        | 8.687 | 223.24             | 292.111 | 277.9  | 279.07 | 8.687               | 223  | 292  | 4417           | 297.663 | 293.35             | 22.24 | 223.2 | 411.1 | 298  | 293.347 | 22.24 | 223.2 | 411.1 |

|       | CM2W70S70U   | g 441            | 12 300               | .15 296  | .87    | 27.32  | 147.36  | 369.34             | 300.148 | 296.87  | 27.324 | 147.36              | 369.34 | 1688  | 272.104 | 273.014        | 11.21 | 147.36             | 288.52  | 272.1  | 273.01 | 11.21               | 147  | 289  | 4412           | 300.148 | 296.87             | 27.32 | 147.4 | 369.3 | 300  | 296.87  | 27.32 | 147.4 | 369.3 |

| nce   | CM3W70S70U   | Š 442            | 23 304               | .09 302  | .21    | 18.57  | 186.06  | 377.45             | 304.091 | 302.213 | 18.571 | 186.06              | 377.45 | 1016  | 280.983 | 282.295        | 7.449 | 186.06             | 288.934 | 280.98 | 282.3  | 7.449               | 186  | 289  | 4423           | 304.091 | 302.21             | 18.57 | 186.1 | 377.5 | 304  | 302.213 | 18.57 | 186.1 | 377.5 |

| acita | CM4W70S70U   | 442              | 22 282               | .82 281  | .83    | 19.98  | 242.55  | 354.04             | 282.819 | 281.826 | 19.983 | 242.55              | 354.04 | 1941  | 264.154 | 264.574        | 8.216 | 242.55             | 277.6   | 264.15 | 264.57 | 8.216               | 243  | 278  | 4422           | 282.819 | 281.83             | 19.98 | 242.5 | 354   | 283  | 281.826 | 19.98 | 242.5 | 354   |

| g     | CM2W70S70T   | 263              | 88 233               | .46 233  | .45    | 14.11  | 77.88   | 363.23             | 233.456 | 233.452 | 14.105 | 77.881              | 363.23 | 21719 | 231.613 | 231.731        | 6.209 | 154.84             | 242.637 | 231.61 | 231.73 | 6.209               | 155  | 243  | 26388          | 233.456 | 233.45             | 14.11 | 77.88 | 363.2 | 233  | 233.452 | 14.11 | 77.88 | 363.2 |

|       | CM3W70S70T   | 265              | 29 220               | .13 220  | .75    | 9.00   | 80.50   | 297.10             | 220.127 | 220.75  | 8.998  | 80.503              | 297.1  | 26426 | 220.402 | 220.768        | 6.741 | 155.15             | 242.176 | 220.4  | 220.77 | 6.741               | 155  | 242  | 26529          | 220.127 | 220.75             | 8.998 | 80.5  | 297.1 | 220  | 220.75  | 8.998 | 80.5  | 297.1 |

|       | CM4W70S70T   | 265              | 20 244               | .75 244  | .24    | 8.05   | 91.57   | 353.41             | 244.748 | 244.238 | 8.053  | 91.571              | 353.41 | 9264  | 236.628 | 237.042        | 2.925 | 222.68             | 240.968 | 236.63 | 237.04 | 2.925               | 223  | 241  | 26520          | 244.748 | 244.24             | 8.053 | 91.57 | 353.4 | 245  | 244.238 | 8.053 | 91.57 | 353.4 |

| 1 L   | CM5W70S70T   | 265              | 30 212               | .75 213  | .01    | 7.12   | 87.29   | 316.53             | 212.752 | 213.01  | 7.121  | 87.288              | 316.53 | 25867 | 212.297 | 212.82         | 6.267 | 159.68             | 225.931 | 212.3  | 212.82 | 6.267               | 160  | 226  | 26530          | 212.752 | 213.01             | 7.121 | 87.29 | 316.5 | 213  | 213.01  | 7.121 | 87.29 | 316.5 |

|       | CM5W70S70U   | 440              | 09 68.               | 80 68.   | 80     | 0.99   | 63.76   | 80.22              | 68.8    | 68.797  | 0.994  | 63.758              | 80.215 | 1     | 68.8    | 68.797         | 0.994 | 63.758             | 80.215  | 68.8   | 68.797 | 0.994               | 63.8 | 80.2 | 4409           | 68.8    | 68.797             | 0.994 | 63.76 | 80.22 | 68.8 | 68.797  | 0.994 | 63.76 | 80.22 |

|       | CM6W400S400L | g 442            | 23 231               | .42 232  | .89    | 7.89   | 192.86  | 258.91             | 231.415 | 232.885 | 7.893  | 192.86              | 258.91 | 4423  | 231.415 | 232.885        | 7.893 | 192.86             | 258.907 | 231.42 | 232.89 | 7.893               | 193  | 259  | 4423           | 231.415 | 232.89             | 7.893 | 192.9 | 258.9 | 231  | 232.885 | 7.893 | 192.9 | 258.9 |

|       | CM6W400S400U | Š 441            | 12 69.               | 32 69.   | 38     | 1.06   | 65.85   | 88.70              | 69.323  | 69.376  | 1.063  | 65.85               | 88.701 | 1     | 69.323  | 69.376         | 1.063 | 65.85              | 88.701  | 69.323 | 69.376 | 1.063               | 65.9 | 88.7 | 4412           | 69.323  | 69.376             | 1.063 | 65.85 | 88.7  | 69.3 | 69.376  | 1.063 | 65.85 | 88.7  |

| 1 L   | CM6W400S400T | 442              | 23 358               | .04 359  | .25    | 9.00   | 313.08  | 376.98             | 358.037 | 359.251 | 9.003  | 313.08              | 376.98 | 1821  | 349.584 | 351.58         | 6.961 | 313.08             | 357.466 | 349.58 | 351.58 | 6.961               | 313  | 357  | 4423           | 358.037 | 359.25             | 9.003 | 313.1 | 377   | 358  | 359.251 | 9.003 | 313.1 | 377   |

|       | CM6W400S400U | o 441            | 12 69.               | 32 69.   | 38     | 1.06   | 65.85   | 88.70              | 69.323  | 69.376  | 1.063  | 65.85               | 88.701 | 1     | 69.323  | 69.376         | 1.063 | 65.85              | 88.701  | 69.323 | 69.376 | 1.063               | 65.9 | 88.7 | 4412           | 69.323  | 69.376             | 1.063 | 65.85 | 88.7  | 69.3 | 69.376  | 1.063 | 65.85 | 88.7  |

| 1 5   | CM7W400S400L | £ 442            | 23 265               | .99 268  | .12    | 8.36   | 225.72  | 282.15             | 265.985 | 268.121 | 8.364  | 225.72              | 282.15 | 4423  | 265.985 | 268.121        | 8.364 | 225.72             | 282.154 | 265.99 | 268.12 | 8.364               | 226  | 282  | 4423           | 265.985 | 268.12             | 8.364 | 225.7 | 282.2 | 266  | 268.121 | 8.364 | 225.7 | 282.2 |

| Ш     | CM7W400S400T | 442              | 322                  | .91 325  | .09    | 8.64   | 282.10  | 340.67             | 322.906 | 325.09  | 8.64   | 282.1               | 340.67 | 4252  | 322.406 | 324.707        | 8.433 | 282.1              | 333.857 | 322.41 | 324.71 | 8.433               | 282  | 334  | 4423           | 322.906 | 325.09             | 8.64  | 282.1 | 340.7 | 323  | 325.09  | 8.64  | 282.1 | 340.7 |

| П     | RLM1W70S70   | 442              | 3695                 | 368      | .76 1  | 176.81 | 3042.82 | 4200.97            | 3695.32 | 3684.76 | 176.81 | 3042.8              | 4201   | 4422  | 3695.32 | 3684.76        | 176.8 | 3042.8             | 4200.97 | 3695.3 | 3684.8 | 176.8               | 3043 | 4201 | 4422           | 3695.32 | 3684.8             | 176.8 | 3043  | 4201  | 3695 | 3684.76 | 176.8 | 3043  | 4201  |

|       | RLM2W70S70   | 442              | 3288                 | 3.51 329 | 7.04 1 | 174.75 | 2762.50 | 3769.43            | 3288.51 | 3297.04 | 174.75 | 2762.5              | 3769.4 | 4412  | 3289.63 | 3297.37        | 173.5 | 2866.9             | 3769.43 | 3289.6 | 3297.4 | 173.5               | 2867 | 3769 | 4423           | 3288.51 | 3297               | 174.7 | 2763  | 3769  | 3289 | 3297.04 | 174.7 | 2763  | 3769  |

| eg.   | RLM3W70S70   | 442              | 3311                 | 1.67 330 | 2.25 1 | 127.64 | 2830.50 | 3758.42            | 3311.67 | 3302.25 | 127.64 | 2830.5              | 3758.4 | 4421  | 3311.78 | 3302.25        | 127.5 | 2885.2             | 3758.42 | 3311.8 | 3302.2 | 127.5               | 2885 | 3758 | 4422           | 3311.67 | 3302.2             | 127.6 | 2830  | 3758  | 3312 | 3302.25 | 127.6 | 2830  | 3758  |

| is to | RLM4W70S70   | 442              | 23 3102              | 307      | 3.28 2 | 204.57 | 2599.42 | 3633.55            | 3102.3  | 3073.28 | 204.57 | 2599.4              | 3633.5 | 3896  | 3144.49 | 3110.99        | 179.4 | 2866.9             | 3633.55 | 3144.5 | 3111   | 179.4               | 2867 | 3634 | 4423           | 3102.3  | 3073.3             | 204.6 | 2599  | 3634  | 3102 | 3073.28 | 204.6 | 2599  | 3634  |

| Re    | RLM5W70S70   | 442              | 23 3337              | 7.23 331 | 3.04 1 | 183.67 | 2871.54 | 3940.76            | 3337.23 | 3313.04 | 183.67 | 2871.5              | 3940.8 | 4423  | 3337.23 | 3313.04        | 183.7 | 2871.5             | 3940.76 | 3337.2 | 3313   | 183.7               | 2872 | 3941 | 4423           | 3337.23 | 3313               | 183.7 | 2872  | 3941  | 3337 | 3313.04 | 183.7 | 2872  | 3941  |

| П     | RLM6W400S400 | 442              | 23 52.               | 30 51.   | 89     | 1.79   | 49.22   | 64.01              | 52.297  | 51.885  | 1.788  | 49.22               | 64.011 | 4423  | 52.297  | 51.885         | 1.788 | 49.22              | 64.011  | 52.297 | 51.885 | 1.788               | 49.2 | 64   | 4423           | 52.297  | 51.885             | 1.788 | 49.22 | 64.01 | 52.3 | 51.885  | 1.788 | 49.22 | 64.01 |

| Ш     | RLM7W400S400 | 442              | 23 52.               | 33 51.   | 85     | 1.95   | 49.07   | 63.65              | 52.333  | 51.845  | 1.945  | 49.065              | 63.653 | 4423  | 52.333  | 51.845         | 1.945 | 49.065             | 63.653  | 52.333 | 51.845 | 1.945               | 49.1 | 63.7 | 4423           | 52.333  | 51.845             | 1.945 | 49.07 | 63.65 | 52.3 | 51.845  | 1.945 | 49.07 | 63.65 |

rapides sur une durée très courte. La technologie de la plateforme est la clé du succès et le DFM a pour but d'améliorer les modèles CAD de transistor et des interconnexions.

Dans le contexte d'une alliance industrielle qui vise à mutualiser des ressources en équipement, le partage d'une plate-forme technologique est une avancée fondamentale où les modèles agréés par l'alliance doivent être adaptés à l'environnement local le plus rapidement possible. Les équipes de périphériques et d'interconnexion effectuent leurs meilleurs efforts pour atteindre cet objectif, mais sur la base des résultats de simulation CAD versus tests électriques. Les difficultés d'adaptation des modèles et l'interconnexion avec ceux offerts par l'alliance sont de plus en plus importantes. Nous concluons et suggèrons que nous devons être plus "DFM orientés" pour réagir rapidement ; cet article a proposé une méthode DFM étendue qui permet aux ingénieurs R&D de réorienter leurs activités depuis l'extraction des données d'alignement et les questions de pré-traitement vers l'analyse et l'identification des causes profondes. Nous avons proposé une méthode de corrélation de localisation pour les systèmes électriques et en ligne (géométrique de mesure).

Nous avons pu observer que les ingénieurs R & D utilisent plusieurs outils statistiques en conformité avec la stratégie utilisée pour le flux de conception de référence. La référence de calcul pour chaque technologie est définie par l'alliance et comprend, modèles, des outils, des séquences de faible utilisation de chaque outil dans les flux de conception et les critères d'acceptation. Les multiples combinaisons des outils statistiques pour l'analyse des données sont sources de confusions : chaque outil est une boîte noire et la mise en œuvre interne de l'algorithme est cachée. Ce fait prend plus d'importance lorsque des filtres sans causes assignables sont appliqués et que des analyses sont effectuées sans veiller à ce que les paramètres sont distribués normalement. Les ingénieurs R&D sont la ressource clé d'une organisation et la compétitivité est directement issue de l'innovation conduite par ces ingénieurs ; il est certainement préférable de ne pas disperser leur capital productif en leur confiant l'extraction de données et les tâches d'analyse, mais de focaliser leurs compétences pour leur permettre de trouver les causes profondes afin de mieux comprendre les mécanismes d'obtention des meilleurs rendements.

#### REFERENCES

Anderson, D.M.; (2006) Design for Manufacturability & Concurrent Engineering; How to Design for Low Cost, Design in High Quality, Design for Lean Manufacture, and Design Quickly for Fast Production, 448 pages; CIM Press

Clair Webb., (2008) Intel Design for Manufacturing and Evolution of Design Rules, Intel technology Journal, Vol. 12, Issue 02

Cliff, M.; (2003) DFM - An Industry Paradigm Shift, International Test Conference (ITC'03)

Harik R.F.; (2007) Spécifications de fonctions pour un système d'aide à la génération automatique de gamme d'usinage : Application aux pièces aéronautiques de structure, prototype logiciel dans le cadre du projet RNTL USIQUICK, Doctorat en Automatique de l'Université Henri Poincaré, Nancy-I, juin 2007.

Herrmann, J.W.; Cooper, J.; Gupta, S.K.; Hayes, C.C.; Ishii, K.; Kazmer, D.; Sandborn P.A.; Wood, W.H.; (2004) New Directions in Design for Manufacturing, Proceedings of DETC'04 ASME design engineering technical conferences and computers and information in engineering conference

Key trends in technology and supply for advanced features within IC industry, Technical Report by International Business Strategies Inc., USA, CA 95030, retrieved from: ibs\_inc@ix.netcom.com

McGregor, J.; (2007) The Common Platform Technology: A New Model for Semiconductor Manufacturing, Technical Report retrieved from: http://www.in-stat.com

Mehrabi, M.G.; Ulsoy, A.G.; Koren Y.; Heytler, P.; (2002) Trends and perspectives in flexible and reconfigurable manufacturing systems, Journal of Intelligent Manufacturing, 13, 135-146

Morinaga, H.; Kakinuma, H.; Ito, T.; Higashiki, T.; (2006) Development of a Platform for Collaborative Engineering data flow between design and manufacturing, IEEE International Symposium on Semiconductor Manufacturing, pp. 45-48

Peters, L.; (2005) DFM Worlds Collide, Then Cooperate, EETimes Magazine, retrieved from: http://www.eetimes.com

Rajesh Raina, (2006) What is DFM & DFY and Why Should I Care?, IEEE International test Conference (ITC'06) pp 1-9

Remy L.; (2010) Mise en place d'une nouvelle méthode de conception orientée DFM, Doctorat en Micro et Nanoélectronique de l'université Aix Marseille I, janvier 2010.

Seino, T.; Honda, S.; Tanaka, T.; (2009) Manufacturing technology management to accelerate "design for manufacturability", Portland International Conference on Management of Engineering & Technology (PICMET) pp. 1137-1142

Tsai-C Kuo, Samuel H. Huang, Hong C. Zhang.; (2001) Design for manufacture and design for 'X': concepts, applications and perspectives, Computer and Industrial Engineering 41, pp. 241-260