# Chip on board 3-10 GHz Impulse Radio Ultra Wideband transmitter with optimized die to antenna wire bond transition

O. Fourquin, Sylvain Bourdel, Jean Gaubert, R. Vauche, N. Dehaese, A. Chami, Jean-Yves Dauvignac, Georges Kossiavas, Nicolas Fortino, P. Brachat

# ▶ To cite this version:

O. Fourquin, Sylvain Bourdel, Jean Gaubert, R. Vauche, N. Dehaese, et al.. Chip on board 3-10 GHz Impulse Radio Ultra Wideband transmitter with optimized die to antenna wire bond transition. IEEE Transactions on Components, Packaging and Manufacturing Technology. Part A, Manufacturing Technology, 2013, 3 (5), pp.749-758. 10.1109/TCPMT.2012.2231466 . hal-00779298

HAL Id: hal-00779298

https://hal.science/hal-00779298

Submitted on 20 Dec 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Chip on board 3-10GHz IR-UWB Transmitter with optimized die to antenna wire bond transition

O. Fourquin, S. Bourdel, *Member, IEEE*, J. Gaubert, *Member, IEEE*, R. Vauché, N. Dehaese A. Chami, J-Y Dauvignac, G. Kossiavas, N. Fortino, P. Brachat

Abstract— In this paper, a low power and low cost Ultra WideBand Impulse Radio (IR-UWB) transmitter is presented. The transmitter includes a pulse generator integrated in a 0.13µm standard CMOS technology and an antenna printed on the chip carrier. The board is manufactured with Roger 4003 laminate substrate and has a total area of 50mm x 18mm. The transmitter provides 1.4V peak to peak FCC compliant pulses at antenna input for data rates up to 36Mb/s in an on-off keying (OOK) modulation scheme. The transmitter's power consumption is 12mW at 1.2GHz Pulse Repetition Frequency and the energy consumption is 10pJ per pulse. A 365mV peak voltage emitted pulse is measured in an anechoic room at 0.8m range with a receiver including a horn antenna (8.3 dBi), a LNA (32 dB), and a 12GHz real time oscilloscope.

Index Terms—antenna, CMOS impulse generator, circuit on board (CoB), transmitter, ultra wideband (UWB), wire bond interconnection.

#### I. INTRODUCTION

The US Federal Communications Commission (FCC) 1 authorizes transmission in the wide frequency bandwidth from 3.1 to 10.6 GHz since the signal bandwidth exceeds 500MHz, its mean Power Spectral Density (PSD) is lower than -41,3dBm/MHz and the peak PSD is lower than 0dBm/50MHz at the frequency where the power is maximum. Thus it is possible to transmit data by using short duration pulses and no carrier. Usually, this method of transmitting information is named Impulse Radio Ultra WideBand (IR-UWB) and enables the front end to be implemented by very simple architectures. Indeed the typical architecture of a non coherent energy detection receiver does not require a mixer and fully digital transmitters operating without any inductors have been reported. In addition the front-end only needs to be powered-on during the short pulse duration time. As a consequence the power consumption tends to be extremely low at low data rates. Thanks to its low cost and low power capacities, IR-UWB can address applications such as Radio Frequency IDentification (RFID) [1], Wireless Body Area Network (WBAN) [2] or Sensor NetWork (SNW). In addition because of its very large bandwidth, IR-UWB can be used in high resolution sensing applications [3]. So, to be suitable for these applications, power consumption and physical implementation of IR-UWB systems have to be carefully

taken into consideration.

An efficient way to drastically reduce the power consumption is to transmit pulses with very short duration and to switch off the transmitter between each emitted pulse. The shortest pulses are obtained by using the full 3.1-10.6 GHz bandwidth. However, because of the limited performance of low cost CMOS technologies, most of published transmitters use only the lower part of the FCC bandwidth which is limited from 3 to 5 GHz. In [4], we demonstrated a CMOS pulse generator die compliant with the full 3.1-10.6 GHz FCC bandwidth having an energy consumption lower than 10pJ/pulse even with the emission of pulses with a peak to peak voltage greater than 1V. With such low energy consumption per pulse, very low power consumption levels can be reached for low data rate without reducing the communication range. In addition short pulse duration enables high pulse repetition frequency to achieve high data rate and low power communications simultaneously.

Other important points which need to be considered for mobile technologies systems are volume, shape factor and cost of the final product, including the antenna. A low cost implementation can be achieved by using a single chip made in a standard CMOS technology connected to an antenna with a low cost package. Nevertheless stringent requirements must be fulfilled in order to guarantee signal integrity with such low cost packages when very large bandwidth pulses are used. Ultra compact transmitters can be manufactured by integrating both the front end and the antenna into a single CMOS die [5]. The use of an on chip antenna avoids problems of signal integrity due to the interconnection between pulse generator die and a remote antenna. However, this technique reduces the antenna efficiency and consequently the communication range. Nevertheless, high efficiency antennas can be obtained by integrating them in Low Temperature Co-fired Ceramic (LTCC) packages using System on Package (SoP) approaches [6]. These packages can also be used to implement pulse shaping networks such as band pass filter [7]. In this way compact transceiver can be implemented using multi layer packages or multi layer Print Circuit Boards (PCB) but at a higher cost. A Chip on Board approach (CoB) can also be used with a planar antenna or a filter [8][9] on the board. For this type of structure, low cost PCB carriers can be used at the expense of a larger surface for the final product.

This paper presents a simple and compact UWB transmitter for low cost and low power applications. The transmitter includes a CMOS pulse generator die and a UWB antenna in a miniature CoB. By using the full 3.1-10.6 GHz FCC bandwidth, very low energy per pulse consumption is reached thanks to short pulse duration. The transmitter is made with low cost technologies: a single die fabricated in a standard CMOS process and a CoB package using conventional wire bonds and two metal layer interconnects. The transmitter provides 1.4V peak to peak FCC compliant pulses at antenna input for data rates up to 36Mb/s in an OOK modulation scheme. The transmitter power consumption is 12mW at 1.2GHz Pulse Repetition Frequency and the energy consumption is 10pJ per pulse. Emitted pulse measurements show 700mV peak to peak voltage pulse measured at 0.8m range with a 40.3dB gain receiver.

This paper is organized as follows. Section II describes the CMOS pulse generator die implemented in a 0.13µm standard CMOS technology. In section III the design of a compact planar UWB antenna is presented. Section IV describes the CoB assembly and presents the design of the wideband wire bond transition between the antenna and the output of the pulse generator. The transition is optimized to achieve the 3-10 GHz bandwidth. The measured results of the transmitter are presented in section V.

#### II. PULSE GENERATOR

This section presents the transmitter die. The transmitter converts the incoming numeric data into a 3-10GHz IR-UWB pulse sequence with an OOK modulation scheme particularly well suited for low cost and low power consumption applications [4].

#### A. Pulse Generator Sizing

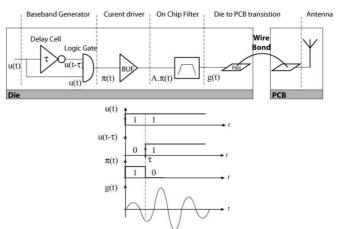

The transmitter uses a CMOS integrated pulse generator [4] designed to achieve high magnitude pulses on  $50\Omega$  load (coming from antenna impedance). As shown in Fig. 1, the generator is based on a filter impulse response technique which consists in applying a very short baseband pulse at the filter input in order to generate its Dirac response [10]. We consider that, instead of a Dirac, the filter is excited by a rectangular function  $\pi_t(t)$  which is formed by the product of a Heaviside step function (u(t)) with its delayed and inverted replica  $(\overline{u(t-\tau)})$ . The output (g(t)) and its Fourier transform are given by:

$$g(t) = \frac{A}{\sqrt{l}} \pi_{\tau}(t) * h_e(t)$$

(1)

$$G(f) = \frac{A\tau \operatorname{sinc}(\pi\tau f).H_{e}(f)}{\sqrt{l}},$$

(2)

where A is the magnitude of the signal at the filter input,  $\tau$  the width of the rectangular function, l the power loss of the filter and  $H_e(f)$  the normalized transfer function of the filter. As the spectrum shape of the pulse (G(f)) is mainly due to  $\tau$  and  $H_e(f)$ , these parameters must be chosen to comply to a particular standard mask.

This technique is well suited to the FCC standard since the minimum order of the filter needed is low (N=3) due to the large width of the FCC frequency mask and enables the full integration of the filter with limited loss (I).  $3^{rd}$  order Bessel filter (which has normalized low pass filter elements respectively equal to  $g_1$ =1.225,  $g_2$ =0.5528 and  $g_3$ =0.1922) and 75ps width baseband pulse are used in this design to comply with the FCC mask.

Having  $H_e(f)$  and  $\tau$  it is possible to compute the Power Spectral Density  $(PSD_s(f))$  of a random signal (s(t)) to evaluate the magnitude of the baseband pulse (A) needed to fit the spectrum requirement:

$$PSD_s(f) = \frac{|G(f)|^2}{T_s} \left( \sigma_a^2 + \frac{\mu_a^2}{T_s} \sum_{i=-\infty}^{\infty} \delta\left( f - \frac{i}{T_s} \right) \right)$$

(3)

where  $\mu_a$  and  $\sigma_a^2$  are respectively the mean and the variance of the sequence data  $\{a_k\}$  and Ts the symbol time.

Fig. 1. Transmitter principle

To ensure low cost and low power architecture we use an OOK modulation scheme. Assuming data rates up to  $36 \text{Mbs}^{-1}$  sufficient for most of the low cost applications we get a value of A=2.56V if 3dB power loss is considered.

# B. Pulse Generator Design

The pulse generator is designed using a standard 0.13 µm CMOS technology to meet cost requirement. The use of such a technology implies constraints on design because passive components have low performances and standard CMOS digital cells based on logic inverter have a minimum propagation delay higher than several hundred picoseconds.

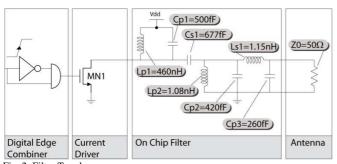

The design of the integrated filter is dominated by the choice of the filter structure, which needs components that perform well in the targeted technology. Indeed, the performances of the passive components and especially the inductor quality factor (Q) vary with the value (L) and the frequency range. For the technology used, L must be in a range of  $400 \mathrm{pH} < L < 1.5 \mathrm{nH}$  to ensure a constant value and a Q > 10 in a  $10 \mathrm{GHz}$  bandwidth. The large relative bandwidth of the FCC mask is a great advantage because the constraints on the dispersion of the inductor values needed are not high and several filters can be realized with such relative bandwidth value. In our case, the chosen Bessel filter is implemented

using a modified ladder topology which leads to the values given in Fig. 2. It is pointed out here that, if the filter structure will not lead to required values, a different  $H_e(f)$  should be chosen during the sizing step which would modify A and  $\tau$ .

Fig. 2. Filter Topology

The baseband generator uses an edge combining technique (also called triangular pulse generation) [10], [11]. To achieve pulse width lower than few hundred picoseconds, modified MOS current mode gate logic (MCML) inverters are used [12]. In order to lower the propagation delay, this technique uses differential pair and reduced output swing as in emitter coupled logic (ECL) technology. Two consecutive edges produced by the MCML inverter are then combined using fast logic gate [10] to produce the baseband pulse. Due to the limited output voltage of the baseband stage (Vdd=1.2V) and due to the low input impedance of the filter (50 $\Omega$ ), the baseband generator cannot drive the filter. A current driver is inserted between the baseband generator and the filter as presented in Fig. 1. The current driver consists of a transistor (MN1 in Fig. 2) operating in C class. MN1 is sized to supply a current value of  $I_0=A/50$  during the conduction time (7). The large amount of current needed implies a large transistor width (W). The output of the transistor must be matched to the filter. Using small signal hypothesis, the output impedance of MN1 (Rds and Cds) can be approximated during the conduction time. The value of Cds must be compensated by Cp1 (if Cds<Cp1) to avoid pulse shape modification. Moreover Rds should be equal to  $50\Omega$  to maximize power matching. Unfortunately, Rds depends on W which is fixed to achieve  $I_0$ . It is not possible to realize power matching while supplying a given  $I_0$  and a trade-off must be made, resulting in lower power efficiency. In the presented design  $W=100\mu m$  which leads to  $Rds=122\Omega$  and Cds=240fF.

# C. Pulse Generator Results

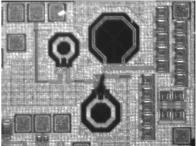

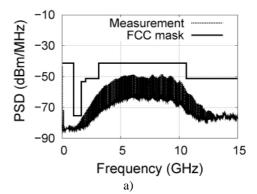

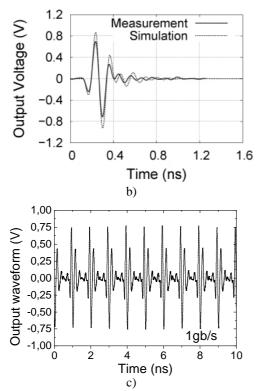

The pulse generator has been made using a standard CMOS 0.13 µm technology from ST Microelectronics. The die photograph is shown in Fig. 3 and its area is 0.54mm². The measurement of the generated pulse using on chip probing is given in Fig. 4. The maximum pulse magnitude is 1.42 Vpp. The measured spectrum of a 36Mbs¹ OOK modulation demonstrates a good compliance with FCC spectrum. Fig. 4.c presents the output waveform when the input is driven by a 1GHz "1 bit" sequence. The pulse generator can achieve data rates up to 1.2Gbs¹. In this case the measured DC power consumption of the pulse generator is 12mW leading to a

measured energy per pulse consumption of 10pJ including the DC power consumption. Table I summarizes the main performances of the pulse generator and presents a comparison with other published transmitters. The proposed transmitter die shows low energy per pulse consumption with high peak voltage and energy efficiency.

TABLE 1

TRANSMITTER PERFORMANCE COMPARISON

| I RANSMITTER FERFORMANCE COMPARISON |                                                                   |                     |               |                                               |                                        |                          |  |

|-------------------------------------|-------------------------------------------------------------------|---------------------|---------------|-----------------------------------------------|----------------------------------------|--------------------------|--|

| Ref                                 | $\begin{array}{c} Technology \\ (\mu m) \\ V_{DD}(V) \end{array}$ | BW<br>(-10dB)       | Vpp           | Energy<br>per pulse<br>consump <sup>a</sup> . | Power Cons.                            | Silicon<br>Area<br>(mm²) |  |

| [5]                                 | CMOS 0.18<br>1.8V                                                 | 6.5 to 9.5<br>GHz   | 30mV          | 12pJ                                          | 9mW<br>@750MHz<br>@PRR                 | 0.045<br>(core)          |  |

| [13]                                | CMOS 0.18<br>1.5V                                                 | 3.75 to<br>4.25 GHZ | 0.18V<br>@50Ω | 18.2pJ                                        | 1.82mW<br>@100MHz<br>@PRR              | 0,39<br>(die)            |  |

| [14]                                | CMOS 0,09<br>1V                                                   | 3.78 to<br>4.33 GHz | 0.65V<br>@50Ω | 47pJ                                          | 470μW<br>@10Mbs <sup>-1</sup><br>@BPSK | 0,08<br>(core)           |  |

| [15]                                | CMOS 0.09                                                         | 3.75 to<br>4.25 GHZ | 0.5V<br>@50Ω  | 29.2pJ                                        | 146 μW<br>@5MHz<br>@PRR                | 1.3<br>(die)             |  |

| This<br>work                        | CMOS 0,13<br>1.2V                                                 | 3.1 to 10.6<br>GHz  | 1.42V<br>@50Ω | 10pJ                                          | 12mW<br>@1.2GHz<br>@PRR                | 0,54<br>(die)            |  |

<sup>&</sup>lt;sup>a</sup> Calculated from power consumption and data rate

Fig. 3. Die photograph

Fig. 4. Pulse generator probe measurement. (a) Frequency domain. (b) Time domain. (c) Output waveform for 1gb/s pulse repetition.

#### III. ANTENNA

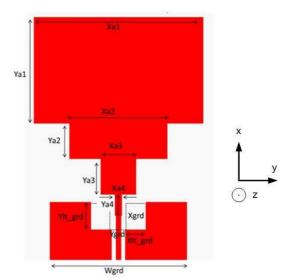

The antenna is printed on the top layer of the chip carrier. This top layer is made of Ro4003 material having a thickness of 200 $\mu$ m thickness. The generic layout of the antenna is shown in Fig. 5. The antenna is a rectangular patch composed of several rectangular steps. The antenna is fed by a 50 $\Omega$  grounded coplanar waveguide (GCPW) printed on the top substrate layer. Two rows of metallic plated holes are used to connect the upper side planes of the GCPW and the lower ground plane these two parts at the same electrical potential. In this way the parasitic modes of the transmission line are suppressed. The ground plane stops at the end of the GCPW leaving the patch antenna in free space and therefore maintaining its wideband characteristics.

#### A. Antenna design

The design of the transition between the line and the patch is crucial to obtaining UWB performances [16][17]. Therefore, a set of simulations were performed to properly tune the coupling between the rectangular patch and its feeding structure using various parameters. Notches were first cut in the two lateral planes at the end of the GCPW. Then another notch has been inserted in the ground plane in order to finalize the tuning. The proper dimensioning of these notches allows modifying the electromagnetic coupling between the line and the patch, and therefore obtaining the desired performances. The characteristics of the antenna can also be adjusted using the size of the ground plane. The final dimensions of steps and notches, corresponding to the selected antenna configuration, are given in Table 2.

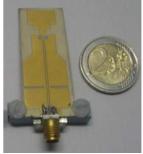

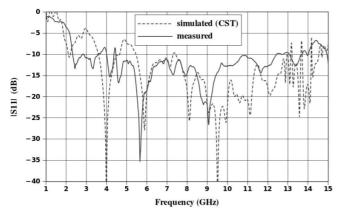

#### B. Antenna measurement results

In order to validate the simulated performances of the antenna, a stand-alone antenna prototype (see Fig. 6.) has been made and measured. The comparison between simulated and measured return loss (RL) is presented in Fig. 7. The RL is greater than 6dB from 3 GHz to 10.6 GHz

Fig. 5. Antenna geometrical parameters

TABLE 2

FINAL ANTENNA PARAMETER VALUES

| Xa1     | 12.35 mm |  |  |  |

|---------|----------|--|--|--|

| Xa2     | 7.15 mm  |  |  |  |

| Xa3     | 2.6 mm   |  |  |  |

| Xa4     | 1.52 mm  |  |  |  |

| Ya1     | 7.8 mm   |  |  |  |

| Ya2     | 2.6 mm   |  |  |  |

| Ya3     | 2.6 mm   |  |  |  |

| Ya4     | 0.56 mm  |  |  |  |

| Xlt_grd | 2 mm     |  |  |  |

| Ylt_grd | 1.5 mm   |  |  |  |

| Xgrd    | 2 mm     |  |  |  |

| Ygrd    | 0.8 mm   |  |  |  |

| Wgrd    | 10 mm    |  |  |  |

Fig. 6. Stand alone antenna prototype.

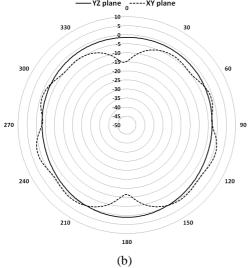

The radiation patterns at the lower and higher limits of the FCC band, respectively 3GHz and 10 GHz, are presented in Fig. 8. Radiation patterns similar to those of a monopole are obtained on the whole bandwidth.

Fig. 7. Measured and simulated antenna return loss.

Fig. 8. Measured antenna radiation patterns in YZ plane and XY plane at 3 GHz (a) and  $10~\mathrm{GHz}$  (b).

# IV. CHIP TO ANTENNA INTERCONNECTION

Large bandwidth systems require generally expensive packages. For low cost applications, wire bonds interconnections are frequently used. However such transitions present a limited bandwidth due to the parasitic inductor introduced by the wire bonds length. In this section, a design methodology is presented in order to obtain a wire bond carrier to die transition with a return loss greater than 15dB in the entire 3-10 GHz UWB band.

# A. Wire bond transition design and modelling

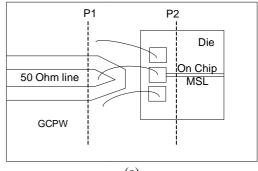

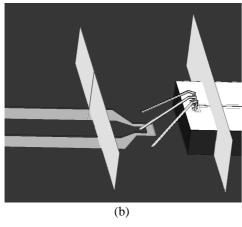

Schematic description of the wire bonds carrier to die transition is given in Fig. 9.a. The transition connects a  $50\Omega$  grounded coplanar line (GCPW) on the chip carrier to a microstrip line (MSL) on the chip. The chip carrier is made on the same top layer of Ro4003 material of 200 $\mu$ m thickness where the antenna has been printed. The major dimensions of the GCPW, which are its central strip width w, its gap g and its thickness t are respectively equal to (390/300/17)  $\mu$ m. The transition includes three  $25\mu$ m diameter aluminium wire bonds. The CMOS silicon die height is  $350\mu$ m. The design has been made to minimize the length of wire bonds while satisfying standard technological design rules for die and package, which leads to 0.8mm wire bond length.

To obtain an electrical model, the wire bond transition has been accurately simulated to provide the scattering parameters between the off die radio frequency (RF) reference plane (P1 in Fig. 9.a) and the on die RF reference plane (P2) referenced to the terminal impedance  $R_0$ . All the electromagnetic (EM) simulation results presented in this section have been obtained using a Finite Element Method EM simulator (HFSS). HFSS model of the wire bond transition between the GCPW and the die is shown in Fig. 9.b. During the simulation process, the RF reference planes are set as close as possible to the wire bond transition in order to minimize the maximum through phase shift and therefore to be closer to a lumped approximation of package transition.

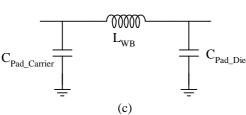

Under those conditions, the wire bond transition can be approximated by the equivalent  $\pi$  network shown in Fig. 9.c.  $L_{WB}$  is the extracted series inductance,  $C_{Pad\_Carrier}$  is the extracted shunt capacitance at the carrier RF reference plane P1 and  $C_{Pad\_Die}$  is the extracted shunt capacitance at the die RF reference plane P2. It should be pointed out that the wire bond transition model includes the effects of both the signal wire bond and the two wire bonds connecting the carrier ground to the die ground.

(a)

Fig. 9. Wire bond transition. (a) Schematic description. (b) HFSS model (c) Lumped equivalent  $\boldsymbol{\pi}$  network.

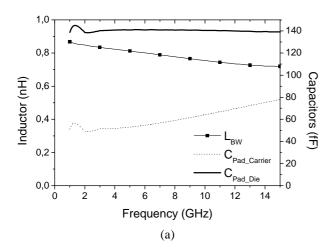

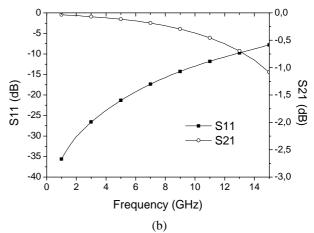

Fig. 10.a plots the extracted values of the series inductance and shunt capacitances of the wire bond transition  $\pi$  electrical model. The extracted values of the series inductance and shunt capacitances are nearly constant up to 10GHz. The capacitance and inductance differences are respectively less than 20fF and 0.1nH from DC to 10GHz.

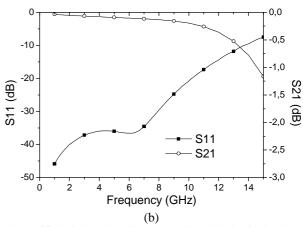

The wire bond transition scattering parameters obtained by EM simulation are given in Fig. 10.b. Transition has a return loss greater than 15dB from DC to 8.5GHz. This bandwidth is not sufficient in our case where the full 3.1-10.6 GHz UWB band is targeted.

Fig. 10. (a) Extracted series inductance and shunt capacitance of the  $\pi$  model of the wire bond transition. (b) Scattering parameters of the wire bond transition obtained by 3d EM simulation.

# B. Wire bond transition bandwidth enhancement.

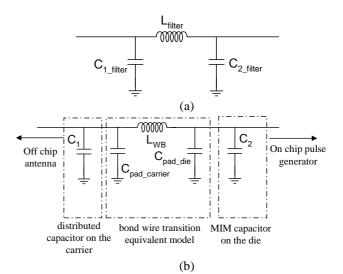

Transition bandwidth can be extended by designing a third order low pass filter embedding parasitic elements of wire bond transition [18]. As shown in Fig. 11, a third order low pass filter (Fig. 11.a) can be synthesized with the transition by adding two capacitors  $C_1$  and  $C_2$  respectively on the carrier and on the die (Fig. 11.b). Inductance  $L_{\text{filter}}$  of the low pass filter is obtained by equaling it to the inductance  $L_{\text{WB}}$  coming from the  $\pi$  network modeling the wire bond transition.

In standard filter design, for ideal inductors and capacitors, the minimum return loss in the filter bandwidth  $f_{cutoff}$  is directly linked to the  $S_{21}$  ripple  $\varepsilon_{dB}$  by

$$RL = -20*\log(\sqrt{1-10^{\frac{\varepsilon_{dB}}{10}}})$$

(4)

Embedding parasitic elements of the transition in a 0.14dB ripple low pass filter enables a transition to be obtained with a RL greater than 15dB in the whole targeted bandwidth.

Fig. 11. (a) Standard low pass filter. (b) Low pass filter embedding the wire bond transition.

In order to synthesize the normalized low pass filter we must satisfy:

$$L_{filter} = \frac{g_2 R_0}{2\pi f_{cutoff}} = L_{pkg} \tag{5}$$

$$C_{1\_filter} = \frac{g_1}{2\pi R_0 f_{cutoff}} = C_1 + C_{Pad\_Carrier}$$

(6)

$$C_{2_{-filter}} = \frac{g_3}{2\pi R_0 f_{cutoff}} = C_{Pad_{-Die}} + C_2 \tag{7}$$

Where  $g_i$  are the low pass filter coefficients allowing a given filter type synthesis (order, ripple, and response) and  $R_0$  the filter characteristic impedance (50 $\Omega$  here).

In this design  $L_{WB}$  is set by the physical geometry of the wire bond transition. With a 0.14dB ripple Butterworth response ( $g_1$ =0.57,  $g_2$ =1.13,  $g_3$ =0.57) [19] we obtain from (5) a bandwidth ( $f_{cutoff}$ ) of 12 GHz and from (6) and (7)  $C_{I\_filter}$ = $C_{2\_filter}$ =151fF.  $C_{I\_filter}$  and  $C_{2\_filter}$  are obtained by adding respectively an 80fF distributed capacitor  $C_1$  to  $C_{pad\_carrier}$  on the carrier and an 11fF metal insulator metal (MIM) capacitor  $C_2$  to  $C_{pad\_die}$  in the die.

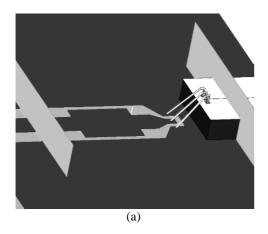

The modified wire bond transition HFSS model is shown in Fig. 12.a and Fig 12.b. shows the scattering parameters of the modified wire bond transition obtained by 3d EM simulation. Modified transition suits UWB applications since it has a return loss greater than 15dB from DC to 11.8 GHz.

Fig. 12. Modified wire bond transition. (a) HFSS model. (b) Simulated scattering parameters.

# V. UWB TRANSMITTER MEASUREMENTS AND RESULTS

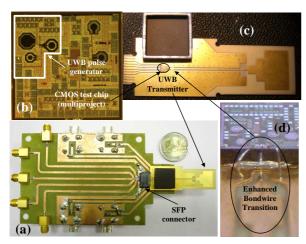

#### A. Transmitter board.

The transmitter board microphotograph is shown in Fig. 13. The board is fabricated using only two metal layers on a Roger 4003 substrate of 200 $\mu$ m high. The transmitter includes the pulse generator CMOS die presented in section III and the printed monopole antenna presented in section III fed by a 50 $\Omega$  ground coplanar line. The transmitter board is plugged into a mother board with an SFP connector which provides the DC biasing and the incoming data. The transmitter emits one pulse when a rising edge is driving the data input (data rates up to 1.2Gb/s can be achieved). The microphotograph of the carrier to die transition optimized as explained in section IV is shown in fig. 13.d. This transition provides a full band UWB access between the RF output of the pulse generator and the 50 $\Omega$  ground coplanar line that feeds the antenna.

| TABLE III: 3.1-10.6 GHz | nublished transmitter | e comparison |

|-------------------------|-----------------------|--------------|

| 1ADLE III. 3.1-10.0 UIZ | publisheu transmittei | s companison |

|              | Chip<br>technology      | Transmitter area | Power consumption | Energy per<br>pulse<br>consumption | Data rate                      | Peak to peak<br>measured<br>voltage     | Calculated emitted<br>peak<br>power at 1m |

|--------------|-------------------------|------------------|-------------------|------------------------------------|--------------------------------|-----------------------------------------|-------------------------------------------|

| This<br>Work | CMOS 0.13µm<br>VDD=1.2V | 50mmx18mm        | 12mW@1.2Gb/s      | 10 pJ <sup>1</sup>                 | up to<br>1.2 Gbs <sup>-1</sup> | 700 mV @80cm<br>@40,3dB/50Ω<br>receiver | -41.3 dBm <sup>2</sup>                    |

| [9]          | CMOS 0.35µm<br>VDD=3.3V | 39mmx40mm        | N/A               | N/A                                | 100Mbs <sup>-1</sup>           | 16 mV @1m<br>@10dB/50Ω<br>receiver      | -41.9 dBm <sup>2</sup>                    |

| [3]          | SiGe 0.8µm              | 60mmx90mm        | 38mW@200Mb/s      | 190pJ <sup>1</sup>                 | 200Mbs <sup>-1</sup>           | 34 mV @15cm<br>@6.8dB/50Ω<br>receiver   | -48.7 dBm <sup>2</sup>                    |

| [8]          | CMOS 0.35µm             | 30mmx35mm        | N/A               | N/A                                | 10Mbs <sup>-1</sup>            | 13 mV @90cm<br>Receiver gain : N/A      |                                           |

<sup>&</sup>lt;sup>1</sup> Calculated from the power consumption and the pulse repetition rate.

<sup>&</sup>lt;sup>2</sup> Calculated from the measured peak to peak voltage and the receiver gain.

Fig. 13. (a) Transmitter board plugged into the mother board. (b) CMOS multi-project test chip including the UWB pulse generator. (c) UWB transmitter. (d) Enhanced carrier to die wire bond interconnection.

# B. Transmitter measurement results.

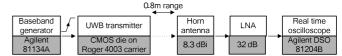

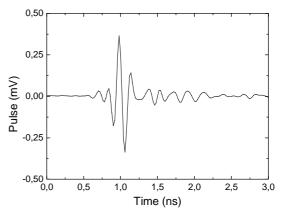

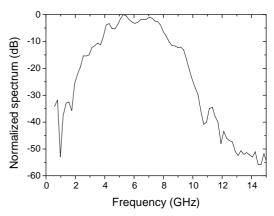

The transmitter measurement setup is described in Fig. 14. The transmitter board is driven by a pulse pattern generator (Agilent 81134A). The measurement receiver includes an 8.3dBi horn antenna, a 32dB LNA and a 12GHz real time oscilloscope (Agilent DSO81204B). All the measurements are performed in an anechoic chamber. Fig. 15 shows a pulse received at 80cm range where 700mV peak to peak voltage has been measured. Taking into account the receiver gain, including the antenna, the LNA gain and the cable loss, we can compute the emitted pulse at 1m range. The calculated peak to peak voltage is 4.3mV which corresponds to an emitted peak power of -41.3dBm at 1m range. Fig. 16 shows the normalized spectrum of the received pulse. Considering that our on chip generator is capable of emitting 1.42Vpp pulses, maximum emitted peak power at 1m range that can be delivered by the on chip generator with an ideal package and an ideal antenna can be estimated thanks to Friis free space equation and considering a frequency of propagation of 5.8GHz ((3.1\*10.6)<sup>0.5</sup>). Calculations indicate a maximum emitted peak power of -40.5dBm at 1m range. This calculated value is closed to -41.3dBm the value obtained in measurement. This demonstrates that the pulses emitted by the chip are not degraded by the antenna and the packaging.

Fig. 14. Measurement setup

Table III compares the proposed transmitter with other 3.1-10.6 GHz published transmitters. The proposed transmitter shows low energy per pulse consumption with high data rate capabilities and high emitted peak power.

Fig. 15. Received pulse at 0.8 meter range.

Fig. 16. Normalized spectrum of the received pulse.

#### VI. CONCLUSION

A compact UWB transmitter module has been presented. The transmitter uses low cost technologies: a single standard CMOS die, a two metal layer carrier, standard bonding wires and a printed monopole antenna. The transmitter demonstrates a very low energy per pulse consumption (10pJ), a pulse peak power of -41.3dBm@1m and can achieve high data rates (1.2Gb/s). These performances could be useful for applications such as low cost and low power accurate positioning or high data rate short range communications.

#### REFERENCES

- [1] M. Baghaei-Nejad, D. S. Mendoza, Z. Zhuo, S. Radiom, G. Gielen, Z. Li-Rong; H. Tenhunen, "A remote-powered RFID tag with 10Mb/s UWB uplink and -18.5dBm sensitivity UHF downlink in 0.18μm CMOS," Solid-State Circuits Conference Digest of Technical Papers, 2009. ISSCC 2009. IEEE International , vol., no., pp.198-199,199a, 8-12 Feb. 2009

- [2] J. Ryckaert, C. Desset, A. Fort, M. Badaroglu, V. De Heyn, P. Wambacq, G. Van der Plas, S. Donnay, B. Van Poucke, B. Gyselinckx, "Ultra-wide-band transmitter for low-power wireless body area networks: design and evaluation," *Circuits and Systems I: Regular Papers, IEEE Transactions on*, vol.52, no.12, pp. 2515- 2525, Dec. 2005

- [3] B. Schleicher, J. Dederer, M. Leib, I. Nasr, A. Trasser, W. Menzel, H. Schumacher, "Highly compact impulse UWB transmitter for high-resolution movement detection," *Ultra-Wideband*, 2008. ICUWB 2008. IEEE International Conference on , vol.1, no., pp.89-92, 10-12 Sept. 2008

- [4] S. Bourdel, Y. Bachelet, J. Gaubert, R. Vauche, O. Fourquin, N. Dehaese, H. Barthelemy, "A 9-pJ/Pulse 1.42-Vpp OOK CMOS UWB Pulse Generator for the 3.1–10.6-GHz FCC Band," *Microwave Theory and Techniques, IEEE Transactions on*, vol.58, no.1, pp.65-73, Jan. 2010

- [5] V. V. Kulkarni, M. Muqsith, K. Niitsu, H. Ishikuro, T. Kuroda, "A 750 Mb/s, 12 pJ/b, 6-to-10 GHz CMOS IR-UWB Transmitter With Embedded On-Chip Antenna," *Solid-State Circuits, IEEE Journal of*, vol.44, no.2, pp.394-403, Feb. 2009

- [6] G. Brzezina, L. Roy, L. MacEachern, "Planar antennas in LTCC technology with transceiver integration capability for ultra-wideband applications," *Microwave Theory and Techniques, IEEE Transactions on*, vol.54, no.6, pp.2830-2839, June 2006

- [7] Y. Changwook, P. Young-Jin, L. Junwoo, P. Hyunjeong, K. Jaemin, P.Jun-So, K. Joungho, "Design of a Low-Noise UWB Transceiver SiP," *Design & Test of Computers, IEEE*, vol.25, no.1, pp.18-28, Jan.-Feb. 2008

- [8] M. Meng, C. Nguyen, "On the Development of an Integrated CMOS-Based UWB Tunable-Pulse Transmit Module," *Microwave Theory and Techniques, IEEE Transactions on*, vol.54, no.10, pp.3681-3687, Oct. 2006

- [9] L. Junwoo, P. Young-Jin, K. Myunghoi, C. Yoon, K. Joungho, K. Kwan-Ho, "System-on-package ultra-wideband transmitter using CMOS impulse generator," *Microwave Theory and Techniques, IEEE Transactions on*, vol.54, no.4, pp. 1667- 1674, June 2006

- [10] Y. Bachelet, S. Bourdel, J. Gaubert, G. Bas, H. Chalopin, "Fully integrated CMOS UWB pulse generator," *Electronics Letters*, vol.42, no.22, pp.1277-1278, Oct. 26 2006

- [11] H. Kim, D. Park, Y. Joo, "All-digital low-power CMOS pulse generator for UWB system," *Electronics Letters*, vol.40, no.24, pp. 1534-1535, 25 Nov. 2004

- [12] K. Marsden, L. Hyung-Jin, H. Dong, L. Hyung-Soo, "Low power CMOS re-programmable pulse generator for UWB systems," *Ultra Wideband Systems and Technologies*, 2003 IEEE Conference on, vol., no., pp. 443-447, 16-19 Nov. 2003

- [13] P. Tuan-Anh, L. Jeongseon, V. Krizhanovskii, H. Seok-Kyun, L. Sang-Gug, "A 18-pJ/Pulse OOK CMOS Transmitter for Multiband UWB Impulse Radio," *Microwave and Wireless Components Letters, IEEE*, vol.17, no.9, pp.688-690, Sept. 2007

- [14] D. D. Wentzloff, A. P. Chandrakasan, "A 47pJ/pulse 3.1-to-5GHz All-Digital UWB Transmitter in 90nm CMOS," Solid-State Circuits Conference, 2007. ISSCC 2007. Digest of Technical Papers. IEEE International, vol., no., pp.118-591, 11-15 Feb. 2007

- [15] Dokania, K. Rajeev, Wang, Y. Xiao, Dorta-Quinones, I. Carlos, Godycki, Waclaw; Tallur, G. Siddharth, Apsel, B. Alyssa, "A 6μW, 100Kbps, 3–5GHz, UWB impulse radio transmitter," Low-Power Electronics and Design (ISLPED), 2010 ACM/IEEE International Symposium on , vol., no., pp.91-94, 18-20 Aug. 2010

- [16] L. Jong-Pil, P. Seong-Ook, L. Sang-Keun, "Bow-tie wide-band monopole antenna with the novel impedance-matching technique" *Microwave and Optical Technology Letters*, Volume 33, Issue 6, 20 June 2002, Pages: 448-452

- [17] A. A. Eldek; "A small ultra-wideband planar tap monopole antenna with slit, tapered transition, and notched ground plane" *Microwave and Optical Technology Letters*, Volume 48, Issue 8, August 2006, Pages: 1650-1654

- [18] J. R. Cubillo, J. Gaubert, S. Bourdel, H. Barthelemy, "RF Low-Pass Design Guiding Rules to Improve PCB to Die Transition Applied to Different Types of Low-Cost Packages," *Advanced Packaging, IEEE Transactions on*, vol.31, no.3, pp.527-535, Aug. 2008

- [19] A. I. Zverev, "Handbook of filter synthesis", John WILEY & sons, 1967

Invia Secure.

Olivier Fourquin was born in Marseilles in 1985. He received a M.Eng degree in Microelectronics and Telecommunications from Polytech' Marseille and a M.S. in Microelectronics and Nanoelectronics from Aix-Marseille University, Marseilles France, in 2008. He received a Ph.D. degree in Microelectronics from Aix-Marseille University in 2011. He currently works with the IM2NP laboratory. His current research interests include CMOS UWB radio transceiver and RFIC packaging. In September 2012 he will work for

Jean Gaubert received M.S. and Ph.D. degrees in applied physics from Paul Sabatier University, Toulouse, France, in 1985, and 1988, respectively. From 1989 to 2001, he was an Assistant Professor with the Ecole Nationale Supérieure de l'Electronique et de ses Applications, Cergy-Pontoise, France, where he was involved in high-speed GaAs and InP bipolar device modeling. In 2001, he joined Aix-Marseille University and the Institut Matériaux Microélectronique Nanosciences de Provence (IM2NP). Since 2009 he has been a

full professor in Electrical Engineering at Aix-Marseille University. His research focuses on the design and integration of RF/microwave CMOS ICs and systems for wireless communications, including low-noise amplifiers, system-in-package integration, and wireless power transmission. He has authored or coauthored over 60 refereed journal and conference papers.

Sylvain Bourdel received his Ph. D in microelectronics from the National Institute of Applied Science (INSA) of Toulouse in 2000. He was with the LASS laboratory of Toulouse where he was involved in radiofrequency system modelling and his special interests were spread spectrum techniques applied to 2.45GHz transceivers. In 2002 he joined the Integrated Circuit Design (CCI) team of the IMNP in Marseilles where he works on CMOS RF IC design and integration. His work particularly focuses on

low cost applications including RFID, UWB and narrow band systems. His area of interest also includes system level specifications, system packaging and interconnections. Since 2011 he has been the head of the CCI team of the IM2NP.

Rémy Vauché was born in Epinal, France, in 1985. He attended a special prep school in Metz, France, in 2003 so as to enter an Engineering School. He received a M.Eng degree in microelectronics and telecommunication from Polytech' Marseille and a M.S. in microelectronics and nanoelectronics from Aix-Marseille University, Marseilles, France, in 2008. He received a Ph.D. degree in 2011 for his research with the IM2NP institute on IR-UWB emitters. His current research interests include UWB radio transceiver design in 130nm & 65nm

CMOS technology for low-power and low-cost applications..

Nicolas Dehaese received a M.S degree from the ISEN engineering school, Lille, France, in 2002 and a Ph.D degree in electronics from the University of Provence, Aix-Marseille I, France, in 2005. Since 2006, he has been an assistant professor in the Integrated Circuits Design Team from the Provence Nanosciences Microelectronics and Materials Laboratory (IM2NP), Marseilles, France. His current field of research is in the design of CMOS integrated circuits and system level specifications for low-cost applications including narrow band

(2.4 GHz) and Ultra Wideband (3.1-10.6 GHz) systems.

Chami Ali was born born in Paris, France, in 1984. His first two years of higher education were at Maths Sup and Maths Spe in the School of Engineering of Beirut-Lebanon in 2003 and 2004. He got his bachelor's degree in electronics in 2005 and his master's degree in EEA (electronic electrotech automatic) in 2006 from the college of Sciences of the Lebanese University - Lebanon. He received his master's research degree in telecommunication frequency and microelectronic radio from University of Nice Sophia Antipolis, France in 2007. He obtained his PhD degree in Telecommunications and radiofrequency in 2011 from the University of Nice SophiaAntipolis with the LEAT laboratory. During his PhD, his research interests included the miniaturization and integration of UWB antennas into new pulsed systems of communication. Currently, he is a research engineer at CNRS and his work concerns innovation and development of IR-UWB systems for BAN applications.

Jean-Yves Dauvignac was born in Sisteron, France, on December 22, 1965. He received a M.S. degree in Telecommunications at the University of Sud Toulon Var (France) in 1987, a D.E.A. degree in Microwave Communications and Signal Processing from the University of Nice-Sophia Antipolis (UNS) (France) and a Ph.D. degree in Electrical Engineering from the UNS in 1993. Between 1993 and 2006, he was an assistant professor in the Telecommunications and Networks Department of the Institute of Technology at the

UNS. Since 2006 he has been a full professor at the Electrical Engineering Department of the UNS. Since 1993 he has been a researcher at the Laboratory of Electronics, Antennas and Telecommunications (LEAT) which is a joint laboratory between the University of Nice-Sophia Antipolis (UNS) and CNRS (French National Research Center). In December 2010 he became the assistant director of the LEAT, and since January 2012 he has been the director of the laboratory.

During his PhD thesis in 1993, his research activities concerned the modeling of microwave planar antennas using finite-surface-elements-method to solve integral equations of the electromagnetic field.

Since 1996 he has been involved in microwave imaging for the detection of buried objects. He developed a new class of UWB antennas (ETS Antennas) in planar printed technology for GPR (Ground Penetrating Radars) and SIMIS (Synthetic Impulse Microwave Imaging System). During this period, he also participated in several campaigns of measurements for pipe detection, road survey and mine detection in collaboration with LCPC and ONERA.

In addition, between 1998 and 2002, he studied the miniaturization and enhancement bandwidth of antennas by using dielectric resonators with high permittivity. Moreover, since 2002, he has been involved in the design of UWB antennas for telecommunication applications and the measurements of UWB antennas in both time and frequency domains. More recently he has worked on the design of high gain antennas for radar systems in millimetre

Currently, he is continuing his research activities on subsurface radar systems, UWB antennas for telecommunication and radar systems and high gain millimetre-waves-antenna. Between 2000 and 2011, he was the header of the activities "Detection and Microwave Imaging" of LEAT.

Georges Kossiavas was born in Volos, Greece, on March 14, 1953. He received a Master's in Physics from the University of Thessaloniki (Greece), a Ph. D. in Electronics from the University of Limoges (France) and the Accreditation to Supervise Research (HDR: Habilitation à Diriger des Recherches) from the University of Nice Sophia Antipolis (UNS - France). He is a full professor in the Electrical Engineering Department of the UNS. He also does research at the Laboratory of Electronics, Antennas and Telecommunications (LEAT – CNRS - UNS). His research interests are microstrip antennas: large band-width and high purity polarisation, compact, multi-standard, reconfigurable elements, MIMO systems, RFID systems and design of UWB antennas for telecommunication applications and the measurements in both time and frequency domains.

Nicolas Fortino was born in Nice, France. He received a D.E.A. degree in propagation, remote sensing, and telecommunications and a Ph. D. degree in electrical engineering from the University of Nice, Sophia Antipolis (UNSA), France, in 2002 and 2006, respectively. Since 2007, he has been an Assistant Professor at the Telecommunications and Networks Department of the Institute of Technology at the UNSA. He joined also the Laboratoria d'Electronique, Antennes et Télécommunications, CNRS-UMR 7248, Sophia Antipolis. His research interests include design and characterization of ultra wide band antenna, planar uwb array, Time and Frequency domain measurement techniques for UWB detection and imaging microwave.

Patrice Brachat was born in Gourdon (France) in 1955. He received a degree in telecommunications and electricity from Ecole Nationale Supérieure des Télécommunications (ENST), Paris, in 1978 and a Ph.D. degree from Université Paul sabatier Toulouse in 1980 and the HdR (Habilitation à diriger les Recherches) degree from Université de Nice Sophia Antipolis in 1998.

In 1981 he joined the antenna departement of France Telecom Research and Development and since 1992 he has been in charge of an Antenna

Research Group in the La Turbie Orange Lab. Since 1992 he has also held scientific appointments at university of Nice Sophia Antipolis (France). Since 2008 he has been co-head of the CREMANT, the antenna joint research center between the Orange Labs, the Nice University and the CNRS (National Scientific Research Center)

His professional interests include the areas of antenna design, small antennas, computational electromagnetics, electromagnetic modeling and simulation. He has published over 80 papers in journals or conferences, and holds 14 patents in these fields.

In 1982 he participated in the creation of JINA conference in NICE (Journées internationales de Nice sur les Antennes). Since 1982 he has been a member of the JINA steering committee, in 1998 he was in charge of scientific secretariat and since 2000 he has been the vice chairman of this conference.

In 2006 he contributed to the birth of the EuCAP conference and was local chairman of the successful EuCAP06 edition in Nice. Since 2006 he has been a member of the EuCAP Technical Committee and senior member IEEE.