# Eco-design for microelectronic products: measurement and integration of environmental criteria

Aurélie Villard, Luc Petit, Alan Lelah, Daniel Brissaud

# ▶ To cite this version:

Aurélie Villard, Luc Petit, Alan Lelah, Daniel Brissaud. Eco-design for microelectronic products: measurement and integration of environmental criteria. 12th International Design Conference DESIGN, 2012, Dubrovnik, May 2012, Dubrovnik, Croatia. pp.1177 - 1184. hal-00737163

# HAL Id: hal-00737163 https://hal.science/hal-00737163

Submitted on 1 Oct 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# ECO-DESIGN FOR MICROELECTRONIC PRODUCTS: MEASUREMENTANT AND INTEGRATION OF ENVIRONMENTAL CRITERIA FOR PACKAGE DESIGN

A. Villard, L. Petit, A. Lelah and D. Brissaud

*Keywords: eco-design, microelectronic product, life cycle assessment, chips packaging*

## 1. Introduction

In a context where more and more micro-products are embedded in day-to-day applications, designers of microelectronic components are dealing with higher and higher technologic stakes linked to circuits' miniaturization and energetic efficiency research. That trend justifies that an effort be made in the microelectronic industry to make chips cleaner.

Before envisaging designing chips taking into account environmental considerations, the designer must have indications on the environmental performances of the different manufacturing processes that could be used. This paper, illustrated by a case of study focused on the chip packaging, describes how to characterize environmental issues so as to influence a decision to be taken during the development of the manufacturing process involved.

Chips are usually encapsulated in a package prior to being embedded into electronic system. This package performs four key functions:

- 1. Provide a sturdy set of leads or balls that allow a chip to be connected to the system in which it will operate

- 2. Provide physical protection for the chip against breakage or scratching

- 3. Provide environmental protection against damage from chemicals, moisture or gases

- 4. Dissipate the heat generated by the chip during operation.

The package is manufactured with a process flow made of about fifteen steps. It begins when the finished silicon wafer is split up into individual die. The die is then assembled into the package which can be handled in the final application.

Awareness on environmental performances of packaging-technology is a key issue for microelectronic industry for three main reasons.

First, although the technological complexity lies mainly in silicon treatment, package design has a significant impact on the performance and reliability of the chip(s) it house and its business cost can be a large fraction of the total manufacturing cost [Andrae 2011]. The technological roadmaps aim to reduce the mass and volume and add the possibility to encapsulate several chips on a same package. These roadmaps drive designers to always imagine innovative solutions to ensure a solid and minimalist protection for more and more complex and fragile chips.

Secondly, with two European directives WEEE and RoHS, legislative pressure is focused on package. Indeed the package represents 95% of the mass of the chip. In the last decade, compliance to RoHS and so the search for health neutrality is leading to high technical challenges for package designers. In a study of the shift from Tin/Lead to lead-free solders paste, [Ekvael 2005] contributed to demonstrate

that RoHS compliance process is not likely to result on environmental improvement and that LCA helps to complete the knowledge on the consequences of such a shift through a life cycle approach. Finally, the environmental impact of a chip is far to from being negligible compared to the semi-conductor component. According [Higgs 2009], the package substrate is the top supply chain material impacting on carbon emissions. The package manufacturing part is such a big consumer of metals, plastics and organic compounds that its impact on the environment is absolutely not negligible.

## 2. Eco-design tool description

Usually, concerns of package designer are driven by different constraints and must reach a compromise. The reasons for change usually come from standard industrial values: cost, quality and efficiency. At designer-level, they are materialized by electrical performances, volume, weight, testability, reliability, choice of materials (avoid banned substances) and cost. The environmental criterion is not measured and so cannot weigh in decision-making processes. Eco-design for package is a conceptual approach in which the designer can consider the environmental impacts of the package he designs. The constraints linked to environmental impacts become a decisive factor to be systematically integrated in the earlier stages of packaging technology development.

#### 2.1 Properties of the eco-design tool

#### Methodology for the development

There have been several previous approaches [Krishnan 2004], [Griese 2004], [Somani 2006], [Harland 2007] to develop environmental design and evaluation tools for the microelectronic industry. The direct duplication of such methods for a specific industrial context poses several problems because of their theoretical complexity, the nature of the necessary information or the in-house organization of work in the company. So the deployment of an original tool for eco-design of packaging technologies has been preferred: it has been built directly from the collaboration with concerned design teams.

A user-centred methodology was applied regarding designers' specificities, and mainly the data they can provide in the earlier stages of development. Several working groups have been organized to understand designers' expectations. An opinion survey helped to define the outline of the results they judge to be useful and easy-to-use. There was so a deliberate choice to exclude any other considerations than environment (economic, technical, or quality) for a better legibility of the results for this pilot project.

It gives a tool admittedly using non-original concepts but really in line with STMicroelectronics designer's expectations and adapted to packages specificities. The next section describes the tool which is an interface for simulating design options during development of a packaging technology.

#### *Functionalities*

Eco-design tool for package designers is applied on new packages under development that are not yet real materialized. It tends to consider the impact generated by a package through its life cycle by:

- 1. Measuring it: estimate if there is benefit or loss when a change occurs in the process flow that means weighing the environmental footprint of a design decision

- 2. Controlling it: ensure that the impact is not getting worse compared to previous generations

- 3. Improving the impact: underline weak points. If there are several likely options, they are compared and the best option available is promoted.

In order to fulfil the 3 goals, the first stage consists of acquiring a better knowledge of the effect on the environment of the process change. Life cycle assessment methodology (LCA) was selected as the support for marking design option regarding a large spectrum of environmental impacts [Bhander 2004]. LCA is acknowledged worldwide as a powerful technique which aims at presenting a global view of the potential impacts derived from the product under consideration, over its full life cycle. Since the last decade, environmental analysis of chips [Williams 2004], [Boyd 2010] has been progressing toward life cycle LCA. However, it is important to keep in mind that main challenges still remain in developing LCA tools to improve data modelling, keep pace with technology changes and

handle uncertainty [Plepys 2004]. Seven indicators, called  $\mu$ -KEPIs for "Key Environmental Performances Indicators for microelectronic industry", related to the main concerns of microelectronic industrial sector have been recently developed by STMicroelectronics and are listed in table 1.

| Indicators                                                             | Unit                                | Sources      |  |

|------------------------------------------------------------------------|-------------------------------------|--------------|--|

| Water consumption during package manufacturing (tape and pure water)   | cubic meters                        | Х            |  |

| Electricity consumption by the equipments during package manufacturing | mega Joules                         | Х            |  |

| Abiotic depletion                                                      | kg Sb eq.                           | CML          |  |

| Eutrophication                                                         | Kg PO <sub>4</sub> eq               |              |  |

| Greenhouse effect                                                      | kg CO <sub>2</sub> eq.              |              |  |

| Photochemical oxidation                                                | kg C <sub>2</sub> H <sub>2</sub> eq |              |  |

| Water eco-toxicity                                                     | kg TEG eq                           | IMPACT 2002+ |  |

Table 1. Indicators considered in the tool - μ-KEPIs

The main contributions to impact categories (emissions, raw materials, chemical substances, water or electricity) are computable. In the results display screen, Pareto graphs are available for each  $\mu$ -KEPI: the ten most damaging areas, the ten most damaging elementary steps, the sources which together count for more than 90% of the damage. When a new process step is inspired from an existing one, the designer can also compare to this parent step.

#### 2.2 LCA implementation

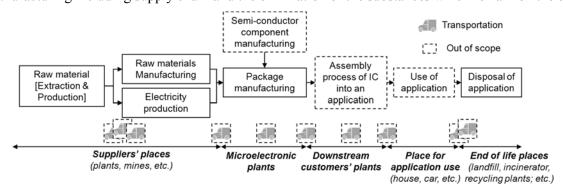

The environmental evaluation is applied separately to the process steps used in package manufacturing. The impact of the package is the sum of the impact of each step. However, to tackle the difficulty to model a complex system such as a microelectronic product, a specific scope for the LCA is required. [Williams 2002] developed the concept of the secondary materialization. He proposed that "increasingly complex products require additional secondary materials and energy to realize their lower entropy form". Contrarily to conventional products, the model of the chip must focus on the secondary raw materials used by the manufacturing processes rather than on its material structure. For package manufacturing, the two levels, direct and indirect, are likely to be modelled with a bottom-up approach. Practically, material and energetic flows, in-coming or out-coming, were inventoried and the environmental analysis is assessed with SimaPro, a LCA-dedicated software. Chip life cycle starts when raw materials and energetic resources are extracted from the soil and ends with the disposal of the chip. As illustrated in the figure 1, the scope of LCA is limited to manufacturing including supply chain and the elimination of the substances which remain on the chip.

Data related to recipes used to run the process are collected either by the R&D Process Engineer who has created the recipe or by the Production Process Engineer who manages industrialization of this recipe. Raw materials properties (density and composition) are collected with suppliers' help via the Material Declaration process or the Material Safety Datasheet. Some suppliers were able to give the impacts of their activity per kilogram or per production unit. Every raw material used during manufacturing is modelled into SimaPro.

A basic average end of life scenario has been created for chips eliminated in 2011 with different destinations (incineration, landfill or recycling channels). The end of life phase of the package is considered in a fragmented way by considering individually each material which composes the chip. So effects of end of life are allocated to the process step where the material is added. For instance, effect of gold recycling are attributed to wire bonding and effects of polymers incineration are attributed to moulding process.

#### 2.3 Environmental evaluation of a manufacturing process by R&D process engineering

#### LCA of a new process

The case presented in this section studies a modification of the manufacturing conditions in wire bonding that seeks to largely decrease the cost of the operation: gold wire is replaced by similar copper-made wire (length and thickness). The benefits or losses in terms of environmental performances are not a priori obvious. Due to heavier extraction processes, the environmental impact of gold is largely higher than copper one: the environmental footprint of the two metals are extracted from Eco-Invent database [Ecoinvent DB 2009] and summarized in Table 2.

| Indicators        | Unit                   | Gold wire | Copper wire |

|-------------------|------------------------|-----------|-------------|

| Abiotic depletion | kg Sb eq.              | 9.82E-04  | 4.81E-08    |

| Eutrophication    | Kg PO <sub>4</sub> eq  | 1.12E-04  | 1.31E-08    |

| Greenhouse effect | kg CO <sub>2</sub> eq. | 8.00E-02  | 6.29E-06    |

kg C<sub>2</sub>H<sub>2</sub> eq

kg TEG eq

Photochemical oxidation

Water eco-toxicity

2.08E-05

2.34E+02

1.65E-08

1.75E-02

Table 2. Environmental footprint of 1 meter-long wires made of gold and copper

Nevertheless, copper has different physical properties which have led to intrinsic process modifications: to avoid oxidation of the copper wire, a tool, called "copper kit" is stacked on the equipment to create a neutral ambiance. This kit induces extra consumption of electricity and N2/H2 gaseous mix is injected in the chamber during the process. The throughput in equipment is decreased, meaning extra equipment occupation and so an augmentation of electricity consumption.

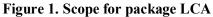

In this case, the relative comparison with the seven indicators highlighted that the increase of electricity and chemicals consumptions is offset by the selection of a greener metal. The Figure 2 presents on the 7  $\mu$ -KEPIs the comparative results of the two techniques of bonding.

Figure 2. Comparison of the environmental footprints of the two wire bonding techniques

Four environmental aspects are improved against only one which is getting worse: copper wire is preferable than a gold one. In selecting a more eco-friendly material, changing the package composition and modifying its processes, LCA stressed that the environmental pressure of a device is reduced. This result is all the more true that yield of copper process is going to be improved.

In some cases, LCA results are equivocal regarding the seven indicators: the designer, who is not an environmental expert, is unable to choose the best option available. In that case the analysis is coupled with specific data treatment to compare it with in-house environmental tolerance thresholds. These

thresholds, fixed in function of in-house strategic issues, allow normalization of the scores and then highlighting the most important aspects.

#### Quick-LCA for processes

In some cases, the recipe has already been elaborated but needs some updates to match the new package specificities. To do this, an option for assessing "Quick-LCA" has been specifically developed for each process. The  $\mu$ -KEPIs can be deduced from referent package by integrating parametric models on process units [Murphy 2003]. The key parameters of the process step are identified and the functions which make vary the flows are defined. The engineer must just specify the modifications compared to a referent package.

| WIRE_BONDING QUICK INTERFACE |     |                |             |  |  |

|------------------------------|-----|----------------|-------------|--|--|

| Parent package               | β   |                |             |  |  |

|                              |     | Value          |             |  |  |

| Is it the same value?        |     | Parent package | New package |  |  |

| material(wire)               | yes | -              |             |  |  |

| diameter(wire) (mils)        | yes | -              |             |  |  |

| length(wire)(m)              | no  | 1.9            | 2.5         |  |  |

| pitch (µm)                   | yes |                |             |  |  |

| Yield (units / hour)         | no  | 45             | 50          |  |  |

Figure 3. Quick-LCA interface for wire bonding

In the wire bonding case (figure 3), if the parameter "wire length" is modified, in-coming and outcoming flows can be deduced from a similar recipe at the condition that other parameters are unchanged. Indeed, the length of wire to be bonded is directly proportional to both the mass of metal consumed and the duration of the process: the quantities needed for LCA (mass of metal, volume of gas N2/H2 and electricity) are easily calculated.

## **3. Experimentation of the eco-design tool**

The functionalities of the tool are tested by a R&D design team during a design review. A design review is a punctual meeting for evaluating the progress of a project. The team is constituted with 8 process engineers and the project leader. The package  $\zeta$  is under development: no prototype has been yet tested. The experimentation aims at measuring, by means of the eco-design tool, the future environmental impact of the package  $\zeta$  once it will be manufactured and integrated in its final electronic application.

#### **3.1 Preliminary studies to prepare the design review**

The package  $\zeta$  is designed in order to answer new technical specifications in terms of functionalities, and dimensions. It is requested for innovative complex integrated-circuits needing an extra-thin protection. Five packages ( $\alpha$ ,  $\beta$ ,  $\gamma$ ,  $\delta$  and  $\varepsilon$ ) have been identified by the product manager as potential former or parent technologies. The five packages have the same body size (12x12 mm) but different thickness, number of connections, balls diameter and connecting options (wire bonding or flip chip pads). The package  $\zeta$  has mixed characteristics coming from these five pre-existing packages but its process assembly is more complex because of a thicker substrate, a more important number of electric connections and so a high density of electrical connections per square millimetre.

## **3.2 During the design review**

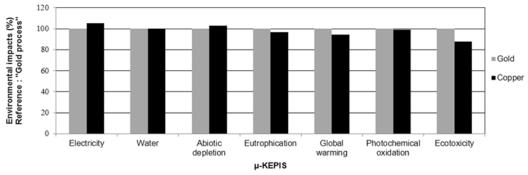

Once the LCAs of the five packages and theirs recipes are recorded, the environmental evaluation of the package  $\zeta$  can be easily assessed with R&D team help. First, the manufacturing process flow of the package is captured. The figure 4 describes the theoretical path of the questions asked in turn to the process engineer during the design review.

Figure 4. Theoretical path of the questions used to fill the interface

The table 3 summarizes the data collected during the meeting according a theoretical path of questioning: the more likely flow, the maturity status of each process step (already existing, modified from a pre-existing recipe, new) and in the two first cases which are the parent packages. It appears that only three packages ( $\alpha$ ,  $\beta$  and  $\delta$ ) are indeed necessary to conduct the analysis on the package  $\zeta$ .

| More likely manufacturing flow $\zeta$ | Status           | Interface | Parent package(s)                                            |

|----------------------------------------|------------------|-----------|--------------------------------------------------------------|

| Substrate manufacturing                | Modified         | Quick-LCA | β and δ                                                      |

| Wafer bumping                          | New              | New LCA   | Х                                                            |

| Wafer back grinding                    | Modified         | Quick-LCA | β or δ                                                       |

| Wafer sawing                           | Modified         | Quick-LCA | α or β or δ                                                  |

| Top ball attach                        | Modified         | Quick-LCA | α orβorγorδ                                                  |

| Cleaning                               | Already existing | Download  | β or δ                                                       |

| Substrate baking                       | Already existing | Download  | $\alpha$ or $\beta$ or $\gamma$ or $\delta$                  |

| Flip chip and reflow                   | Modified         | Quick-LCA | β or δ                                                       |

| Substrate baking                       | Already existing | Download  | α orβorγorδ                                                  |

| Plasma                                 | Already existing | Download  | β or δ                                                       |

| Underfill dispensing and curing        | Modified         | Quick-LCA | β or δ                                                       |

| Plasma                                 | Already existing | Download  | $\alpha$ or $\beta$ or $\gamma$ or $\delta$                  |

| Injection moulding and curing          | Modified         | Quick-LCA | α                                                            |

| Laser treatment opening                | New              | New LCA   | Х                                                            |

| Ball attach                            | Modified         | Quick-LCA | δ                                                            |

| Laser marking                          | Already existing | Download  | $\alpha$ or $\beta$ or $\gamma$ or $\delta$ or $\varepsilon$ |

| Package singulation                    | Already existing | Download  | $\alpha$ or $\beta$ or $\gamma$ or $\delta$ or $\varepsilon$ |

Table 3. Data collected during design review (reproduction of the interface)

For the processes which have never been tested before, in this case laser opening of interconnections through organic resin, the process engineer in charge of the development is asked to estimate the parameters of the future recipe. All inputs and by-products in terms of fluids, materials, energy and emitted substances must be evaluated. An uncertainty warning is associated to this step and the scores are noted as temporary and will be re-evaluated once the recipe parameters will be better-known. For already existing processes,  $\mu$ -KEPIs are either directly downloaded from parent package or "Quick-LCA" interface is used if there are different.

## 3.3 After the design review

Thanks to the tool, projected environmental footprint of a package was known several months before industrialization. Results are presented to the design team: the environmental footprint of the package

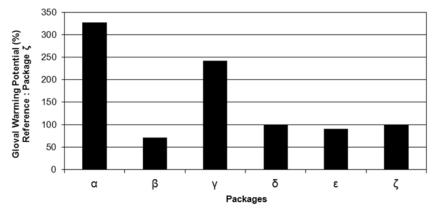

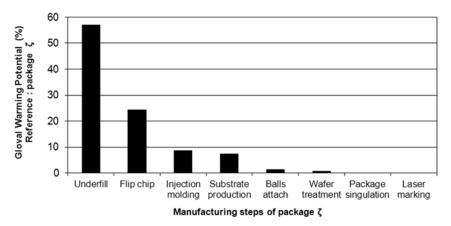

$\zeta$  compared to the previous generations and a Pareto with the relative environmental footprint of each manufacturing process step of the package  $\zeta$ . Figures 5 and 6 show the type of results obtained in the case of the global warming indicator and with a relative scale taking package  $\zeta$  as reference.

Figure 5. Global Warming Potential for package  $\zeta$  and its parent packages

Figure 6. Global Warming Potential for manufacturing processes of package  $\boldsymbol{\zeta}$

# 4. Conclusion and perspectives

The environmental evaluation of a packaging technology under-development has been successfully assessed thanks to the collaboration with a design team. It was part of the elaboration and test of a prototype tool presented in this paper. It is expected that this prototype tool will incline designers to systematically include environmental criteria into their decision-making process. This experiment was a first step of eco-design in the company and gave several perspectives before being systematically used by package designers. First of all, it has proven that environmental assessment of new package is possible. Mainly, the use of a simplifying hypothesis that design is mostly made by analogy has been confirmed.

In such an eco-design process, the collaboration and active participation of all the design team is required. To ensure viability and potential duplication at company-scale, the time allocated to this new task should be minor. That is why designers' constraints are carefully evaluated to be in line with their day-to-day tasks. First, it is advisable to further simplify process modelling in the tool: it will be possible both by asking for less data for the life cycle inventory and by reducing the number of key parameters in Quick-LCA. Secondly, the data to be collected for LCA of process recipes, except input quantities of raw materials and fluids, are not easily available for a R&D engineer because they have rather never been considered so far. To tackle this difficult, a full collaboration between R&D centres and production areas is required and should be established.

Even if the results have not been directly used and integrated for the design, for the first time, the designers were aware about environmental impact of their activities and that any design decisions is

likely to modify the environmental footprint of the future chip. The interpretation of the results allows the whole design team to define trends and find axes for improvement. In a process of continuous improvement, each time a LCA of a package or a process step is assessed, the seven indicators will be recorded in a database. The more this database will grow, the more the range of processes used in the company will be covered and so faster will be the LCA of new package. This experience gave encouraging results and has validated a method able to arouse designers' interest about environmental aspects without any unreasonable constraints.

#### Acknowledgments

This research is funded by STMicroelectronics. The authors wish to thank all the members of the pilot design team, CPA Grenoble of STMicroelectronics, who takes an active part in the eco-design project for package designers.

#### References

Andrae, A., Andersen, O., "Life cycle assessment of integrated circuit packaging technologies", The International Journal of Life Cycle Assessment, Vol.16, No.3, 2011, pp 258-267.

Bhander, G.S, Hauschild, M., McAloone, T., "Implementing life cycle assessment in product development", Environmental Progress, Vol.22, No.4, 2003, pp. 255-267.

Boyd, S.B, Horvath, A., Dornfeld, D.A., "Life-cycle assessment of computational logic produced from 1995 through 2010", Environmental Research Letters Vol.5, No.1, 2010, 014011.

Ecoinvent DB (2009) Gold, at regional storage/RER U; Copper, at regional storage/RER U

*Ekvael T., Andrae, A., "Attributional and Consequential Environmental Assessment of the Shift to Lead-Free Solders", The International Journal of Life Cycle Assessment Vol.11., 2005, pp 344-353.*

Griese, H., Schischke, K., Reichl, H., Stobbe, L., "Sustainable development of microelectronic technology processes integration of ecodesign", Proceeding of the Sixth IEEE CPMT Conference on High Density Microsystem Design and Packaging and Component Failure Analysis, 2004, pp 154-159.

Harland J., Harman D., Drago L. "Design for Environment in New Semiconductor Manufacturing Technologies" International Symposium on Electronics and the Environment, IEEE Computer Society, Los Alamitos, CA, USA, 2007, pp. 91–96.

Higgs, T., Cullen, M., Yao, M., Stewart, S., "Developing an overall CO2 footprint for semiconductor products", Proceedings of the 2009 IEEE International Symposium on Sustainable Systems and Technology, IEEE Computer Sociey, Washington, DC, USA, 2009, pp 1-6.

Krishnan, N., Raoux, S., Dornfeld, D., "Quantifying the Environmental Footprint of Semiconductor Equipment Using the Environmental Value Systems Analysis (EnV-S)", IEEE Transactions on Semiconductor Manufacturing, Vol.17, No.4, 2004, pp 554-561.

Murphy, C. F., Kenig, G. A., Allen, D. T., Laurent J-P., Dyer D. E. "Development of Parametric Material, Energy, and Emission Inventories for Wafer Fabrication in the Semiconductor Industry" Environ. Sci. Technol. 37, no. 23, 2003, pp. 5373–5382.

Plepys, A., "The environmental impacts of electronics. Going beyond the walls of semiconductor fabs", Proceedings of the International Symposium on Electronics and the Environment, IEEE Computer Society, location Washington, DC, USA, 2004, pp 159-165.

Somani A., Gschwend P., White S.J., Boning D., Reif R. "Environmental Impact Evaluation Methodology for Emerging Silicon-Based Technologies", IEEE International Symposium on Electronics and the Environment, IEEE Computer Society, 2006, pp. 258–263.

*Williams, E.D., "Environmental impacts of microchip manufacture", Thin Solid Films 461, No.1., 2004, pp 2-6. Williams,E.D., Ayres, R.U., Heller, M. "The 1.7 Kilogram Microchip: Energy and Material Use in the Production of Semiconductor Devices", Environ. Sci. Technol., Vol.36, No.24, 2002, pp 5504-5510.*

Ms. Aurélie Villard Ph.D. Student G-SCOP Grenoble 46 avenue Félix Viallet 38031 Grenoble, France Telephone: 0033442685260 Email: aurelie.villard@g-scop.inpg.fr