# Proceedings of the 6th Many-core Applications Research Community (MARC) Symposium

Eric Noulard

# ▶ To cite this version:

Eric Noulard. Proceedings of the 6th Many-core Applications Research Community (MARC) Symposium. Eric Noulard and Simon Vernhes. ONERA, The French Aerospace Lab, pp.1-71, 2012, 978-2-7257-0016-8. hal-00719042

HAL Id: hal-00719042

https://hal.science/hal-00719042

Submitted on 18 Jul 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

http://sites.onera.fr/scc/marconera2012

July  $19^{\text{th}} - 20^{\text{th}} 2012$

$\begin{array}{c} ISBN \\ 978 \hbox{-} 2 \hbox{-} 7257 \hbox{-} 0016 \hbox{-} 8 \end{array}$

ONERA

THE FRENCH AEROSPACE LAB

The leading aerospace and defense research organization in France

To maintain our scientific and technical leadership, ONERA invests in fundamental research and spurs innovation. We are developing the defense technologies that will underpin tomorrow's strategic and tactical systems. We are also working on the enabling technologies for tomorrow's commercial aircraft, to reduce fuel consumption and noise, while further improving safety.

ONERA is a multidisciplinary organization that brings together the talents of 2,000 top experts in energetics, aerodynamics, materials, structures, electromagnetism, optics, instrumentation, atmospheric environment and space physics, complex and onboard systems, information processing and long-term design, Europe's leading center for aeronautical wind tunnels.

Results-oriented, ONERA conducts research in true project mode, based on professionalism, scientific excellence, impartial expertise and confidentiality. Fully two-thirds of our business comes from commercial contracts with firm deadlines, awarded under competitive conditions. Our annual budget is 244 million euros, including 26 million euros to keep our plant and equipment in perfect shape. ONERA works for both governments and industry.

# **Table of Contents**

| Keynote speaker for MARC'ONERA'2012  Parallelisation of Hard Real-time Applications for Embedded Multi- and Many-cores  Prof. Dr. Theo Ungerer                      | 1  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Go's Concurrency Constructs on the SCC                                                                                                                              | 2  |

| Performance of RDF Query Processing on the Intel SCC                                                                                                                | 7  |

| Data Sharing Mechanisms for Parallel Graph Algorithms on the Intel SCC                                                                                              | 13 |

| One-Sided Communication in RCKMPI for the Single-Chip Cloud Computer                                                                                                | 19 |

| Asynchronous Broadcast on the Intel SCC using Interrupts                                                                                                            | 24 |

| Work in Progress: Malleable Software Pipelines for Efficient Many-core System Utilization                                                                           | 30 |

| Enabling Computation Intensive Applications in Battery-Operated Cyber-Physical Systems                                                                              | 34 |

| Interactive Visual Task Management on the 48-core Intel SCC                                                                                                         | 40 |

| Modelling Power Consumption of the Intel SCC                                                                                                                        | 46 |

| Transparent Programming of Many/Multi Cores with OpenComRTOS  Comparing Intel 48-core SCC and TI 8-core TMS320C6678  Bernhard Sputh, Andrew Lukin and Eric Verhulst | 52 |

| Efficient Implementation of the bare-metal hypervisor MetalSVM for the SCC                                                                                          | 59 |

| BareMichael: A Minimalistic Bare-metal Framework for the Intel SCC                                                                                                  | 66 |

Table of Contents

# MESSAGE FROM THE PROGRAM CHAIR

In continuation of a successful series of events, the  $6^{th}$  symposium of the Many-core Applications Research Community (MARC) took place at ONERA research center in Toulouse. On July  $19^{th}$  and  $20^{th}$  2012, researchers from different fields presented their current and future work on many-core hardware architectures, their programming models, and the resulting research questions for the upcoming generation of heterogeneous parallel systems.

These proceedings include 12 papers from 4 symposium sessions. Every paper was reviewed by at least three reviewers from the program committee, consisting of:

Pr. Frédéric Boniol ONERA

Dr. Ulrich Bretthauer Intel Labs

Dr. Marc Boyer ONERA

Dr. Carsten Clauss RWTH Aachen University

Dr. Madeleine Faugère THALES

Dr. Sylvain Girbal THALES

Dr. Diana Göhringer Karlsruhe Institute of Technology (KIT)

Dr. Matthias Gries Intel Labs

Werner Haas Intel Labs

Jason M. Howard Intel Labs

Dr. Michael Hübner Ruhr University of Bochum (RUB)

Michael Konow Intel Labs

Dr. Stefan Lankes RWTH Aachen University

Jean-Claude Laperche Airbus

Timothy G. Mattson Intel Labs

Pr. Dr. Jörg Nolte BTU Cottbus

Dr. Eric Noulard ONERA

Dr. Claire Pagetti ONERA

Patrick Pelgrims ESAT K.U.Leuven

Pr. Dr. Andreas Polze Hasso-Plattner-Institute

Dr. Philippe Queinnec IRIT

Michael Riepen Intel Labs

Dr. Matthieu Roy LAAS-CNRS

Pr. Pascal Sainrat IRIT

Pr. Dr. Bettina Schnor University of Potsdam

Pr. Dr. Theo Ungerer Universität Augsburg

Dr. Peter Tröger Hasso-Plattner-Institute

Benoit Triquet Airbus

Dr. Vincent Vidal ONERA

Rob F. Van Der Wijngaart Intel Corp.

We would like to thank our program committee members for their hard work and for their suggestions in the selection of papers. We would like to thank all those who submitted papers for their efforts and for the quality of their submissions. We also would like to thank Nadine Barriety, Marine Bergouts and all members of ONERA/DTIM and ONERA/DCSD for their assistance and support. Special thank to Simon Vernhes for the preparation of the proceedings. Thank you for your active participation in the 6<sup>th</sup> MARC Symposium.

Eric Noulard, ONERA, Toulouse Research Center, France. Toulouse, July 2012.

Program Committee ii

#### ISBN: 978-2-7257-0016-8

# Parallelisation of Hard Real-time Applications for Embedded Multi- and Many-cores

Keynote speaker for MARC'ONERA'2012

Prof. Dr. Theo Ungerer Chair of Systems and Networking Dept. of Computer Science, University of Augsburg ungerer@informatik.uni-augsburg.de

Providing higher performance than state-of-the-art embedded processors can deliver today will increase safety, comfort, number and quality of services, while also lowering emissions as well as fuel demands for automotive, avionic and automation applications. Engineers who design hard real-time embedded systems in such embedded domains express a need for several times the performance available today while keeping safety as major criterion. A breakthrough in performance is expected by parallelising hard real-time applications and running them on an embedded multi-core processor, which enables combining the requirements for high-performance with time-predictable execution.

The talk will present research approaches and results of the parallelisation and WCET (Worst-case Execution Time) analysis of industrial hard real-time applications. It shows how a WCET analysis of the communication and synchronization patterns can be performed and how a WCET speedup can be reached for parallelised programs based on parallel design patterns. Research approaches and results of the EC FP-7 projects MERASA (Multi-Core Execution of Hard Real-Time Applications Supporting Analysability, 2007-2011) and parMERASA (2011-2014) are presented. Both projects target timing analysable systems of parallel hard real-time applications running on a embedded multi-core processor. parMERASA investigates time predictable parallelisation for future embedded many-core systems with up to 64 cores.

# Go's Concurrency Constructs on the SCC

Andreas Prell and Thomas Rauber

Department of Computer Science

University of Bayreuth, Germany

{andreas.prell,thomas.rauber}@uni-bayreuth.de

Abstract—We present an implementation of goroutines and channels on the SCC. Goroutines and channels are the building blocks for writing concurrent programs in the Go programming language. Both Go and the SCC share the same basic idea—the use of messages for communication and synchronization. Our implementation of goroutines on top of tasks reuses existing runtime support for scheduling and load balancing. Channels, which permit goroutines to communicate by sending and receiving messages, can be implemented efficiently using the on-die message passing buffers. We demonstrate the use of goroutines and channels with a parallel genetic algorithm that can utilize all cores of the SCC.

#### I. Introduction

Go is a general-purpose programming language intended for systems programming [1]. We leave out a general description of Go, and rather focus on its support for concurrent programming, which is not the usual "threads and locks", even if threads and locks are still used under the covers. Programmers are encouraged to "share memory by communicating", instead of to "communicate by sharing memory". This style of programming is reminiscent of message passing, where messages are used to exchange data between and coordinate execution of concurrently executing processes. Instead of using locks to guard access to shared data, programmers are encouraged to pass around references and thereby transfer ownership so that only one thread is allowed to access the data at any one time.

Go's way of thinking is also useful when programming Intel's Single-Chip Cloud Computer (SCC) research processor. The SCC is intended to foster manycore software research, using a platform that's more like a "cluster-on-a-chip" than a traditional shared-memory multiprocessor. As such, the SCC is tuned for message passing rather than for "threads and locks". Or as Intel Fellow Jim Held commented on the lack of atomic operations: "In SCC we imagined messaging instead of shared memory or shared memory access coordinated by messages. [...] Use a message to synchronize, not a memory location." [2], [3] So, we think it's reasonable to ask, "Isn't Go's concurrency model a perfect fit for a processor like the SCC?" To find out, we start by implementing the necessary runtime support on the SCC.

# II. CONCURRENCY IN THE GO PROGRAMMING LANGUAGE

Go's approach to concurrency was inspired by previous languages that came before it, namely Newsqueak, Alef, and Limbo. All these languages have in common that they built on Hoare's Communicating Sequential Processes (CSP), a formal

language for writing concurrent programs [4]. CSP introduced the concept of channels for interprocess communication (not in the original paper but in a later book on CSP, also by Hoare [5]). Channels in CSP are synchronous, meaning that sender and receiver synchronize at the point of message exchange. Channels thus serve the dual purpose of communication *and* synchronization. Synchronous or unbuffered channels are still the default in Go (when no buffer size is specified), although the implementation has evolved quite a bit from the original formulation and also allows asynchronous (non-synchronizing) operations on channels.

Go's support for concurrent programming is based on two fundamental constructs, goroutines and channels, which we describe in the following sections.

# A. Goroutines

Think of goroutines as lightweight threads that run concurrently with other goroutines as well as the calling code. Whether goroutines run in separate OS threads or whether they are multiplexed onto OS threads is an implementation detail and something the user should not have to worry about. A goroutine is started by prefixing a function call or an anonymous function call with the keyword go. The language specification says: "A go statement starts the execution of a function or method call as an independent concurrent thread of control, or goroutine, within the same address space." [6] In other words, a go statement marks an asynchronous function call that creates a goroutine and returns without waiting for the goroutine to complete. So, from the point of view of the programmer, goroutines are a way to specify concurrently executing activities; whether they are allocated to run in parallel is determined by the system.

# B. Channels

In a broader sense, channels are used for interprocess communication. Processes can send or receive messages over channels or synchronize execution using blocking operations. In Go, "a channel provides a mechanism for two concurrently executing functions to synchronize execution and communicate by passing a value of a specified element type." [6] Go provides both unbuffered and buffered channels. Channels are first-class objects (a distinguishing feature of the Go branch of languages, starting with Newsqueak): they can be stored in variables, passed as arguments to functions, returned from functions, and sent themselves over channels. Channels are also typed, allowing the type system to catch programming errors, like trying to send a pointer over a channel for integers.

| L2\$ 1 | IA-32<br>Core 1 |  |  |

|--------|-----------------|--|--|

| Router | МРВ             |  |  |

| L2\$ 0 | IA-32<br>Core 0 |  |  |

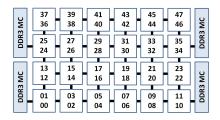

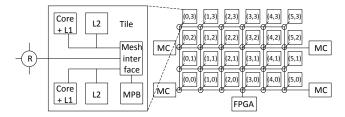

Fig. 1. The 48-core SCC processor: 6x4 tile array (left), 2-core tile (right)

# III. A GLIMPSE OF THE FUTURE? THE SCC PROCESSOR

The Single-Chip Cloud Computer (SCC) is the second processor developed as part of Intel's Tera-scale Computing Research Program, which seeks to explore scalable manycore architectures along with effective programming techniques. At a high level, the SCC is a 48-core processor with a noticeable lack of cache coherence between cores. It does support shared memory, both on-chip and off-chip, but it's entirely the (low-level) programmer's responsibility to avoid working on stale data from the caches—if caching is enabled at all. In the default configuration, most system memory is mapped as private, turning the SCC into a "cluster-on-a-chip", programmed in much the same way as an ordinary cluster.

Message passing between cores is enabled by the inclusion of 16 KB shared SRAM per tile, called Message Passing Buffer (MPB). Programmers can either use MPI or RCCE, a lightweight message passing library tuned to the features of the SCC [7], [8]. RCCE has two layers: a high-level interface, which provides send and receive routines without exposing the underlying communication, and a low-level interface, which allows complete control over the MPBs in the form of one-sided put and get operations—the basic primitives to move data around the chip. RCCE also includes an API to vary voltage and frequency within domains of the SCC, but we won't go into power management issues here.

# IV. Go's Concurrency Constructs on the SCC

RCCE's low-level interface allows us to manage MPB memory, but with an important restriction. RCCE uses what it calls a "symmetric name space" model of allocation, which was adopted to facilitate message passing. MPB memory is managed through collective calls, meaning that every worker must perform the same allocations/deallocations and in the same order with respect to other allocations/deallocations. Thus, the same buffers exist in every MPB, hence symmetric name space. If we want to make efficient use of channels, we must break with the symmetric name space model to allow every worker to allocate/deallocate MPB memory at any time.

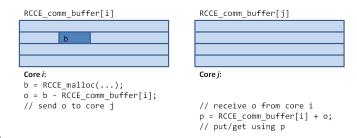

Suppose worker i has allocated a block b from its MPB and wants other workers to access it (see also Figure 2). How can we do this? RCCE tells us the starting address of each worker's portion of MPB memory via the global variable RCCE\_comm\_buffer. Thus, worker j can access any location in i's MPB by reading from or writing to addresses

<sup>1</sup>Worker means process or thread in this context. RCCE uses yet another term—unit of execution (UE). On the SCC, we assume one worker per core.

Fig. 2. Accessing buffers in remote MPBs without requiring collective allocations. Because buffer b is not replicated in other cores' MPBs, offset o can't be determined implicitly (as in RCCE\_put/RCCE\_get), but must be passed between cores.

RCCE\_comm\_buffer[i] through RCCE\_comm\_buffer[i] + 8191. Note that in the default usage model, the 16 KB shared SRAM on a tile is equally divided between the two cores. Worker j then needs to know the offset of b within i's MPB. This offset is easily determined on i's side, and after communicating it to worker j, j can get a pointer to b and use this pointer to access whatever is stored at this address. To summarize, any buffer can be described by a pair of integers (ID, offset), which allows us to abandon collective allocations and to use the MPBs more like local stores.

# A. Goroutines as Tasks

We have previously implemented a tasking environment to support dynamic task parallelism on the SCC [9]. Specifically, we have implemented runtime systems based on work-sharing and work-stealing to schedule tasks across the cores of the chip. If we map a goroutine to a task, we can leave the scheduling to the runtime system, load balancing included. Scheduling details aside, what **go** func(a,b,c); then does is create a task to run function func using arguments a, b, and c, and enqueue the task for asynchronous execution. Tasks are picked up and executed by worker threads. Every worker thread runs a scheduling loop where it searches for tasks (the details depend on which runtime is used). One thread, which we call the master thread, say, thread 0, is designated to run the main program between the initializing and finalizing calls to the tasking environment. This thread can call goroutines, but it cannot itself schedule goroutines for execution. In addition to the master thread, we need one or more worker threads to be able to run goroutines. This is currently a restriction of our implementation.

Figure 3 shows a pictorial representation of workers running goroutines. Assume we start a program on three cores—say, core 0, core 1, and core 2—there will be a master thread and two worker threads, each running in a separate process. Worker threads run goroutines as coroutines to be able to yield control from one goroutine to another [10]. While a goroutine shares the address space with other goroutines on the same worker, goroutines on different workers also run in different address spaces (sharing memory is possible). This is a deviation from the Go language specification, which states that goroutines run concurrently with other goroutines, within the same address space. What we need is a mechanism to allow goroutines

Fig. 3. An example execution of a program with goroutines on three cores of the SCC processor. In this example, worker 1 is running three goroutines, while worker 2 is running two goroutines. The master thread can call goroutines but not run them. Worker threads switch goroutines as needed, whenever a goroutine blocks on a channel.

to communicate, regardless on which core they are running. Channels in shared memory provide such a mechanism.

#### B. Channels

Our channel implementation takes advantage of the SCC's on-chip memory for inter-core communication. A channel is basically a blocking FIFO queue. Data items are stored in a circular array, which acts as the channel's internal buffer. Channel access must be lock-protected because the SCC lacks atomic operations and only provides one test-and-set register per core for the purpose of mutual exclusion.

A buffered channel of size n has an internal buffer to store n data items (the internal buffer has actually n+1 slots to make it easier to distinguish between an empty and a full buffer). If the buffer is full and another item is sent to the channel, the sender blocks until an item has been received from the channel. An unbuffered channel, which is the default in Go when no size is given, is implemented as a buffered channel with an internal buffer to store exactly one data item. Unlike a send to a buffered channel, however, a send to an unbuffered channel blocks the sender until a receive has happened.

A channel (unbuffered) takes up at least 160 bytes—four cache lines to hold the data structure, plus a cache line of internal channel buffer. When we try to write a concurrent program such as the prime sieve presented in the Go language specification [6] and in the Go tutorial [11], we must be aware of channel related memory leaks that can quickly exhaust the MPBs. Go on the other hand, is backed by a garbage collector, which reclaims memory behind the scenes, and which, according to Rob Pike, is in fact "essential to easy concurrent programming" [12]. What the current implementation doesn't include are functions to close a channel and to peek at a set of channels simultaneously (Go's **select** statement, which is like a **switch** statement for channel operations).

# C. Channel API

The basic channel API consists of four functions:

# Channel \*channel\_alloc(size\_t sz, size\_t n);

Allocates a channel for elements of sz bytes in MPB memory. If the number of elements n is greater than zero, the channel is buffered. Otherwise, if n is zero, the channel is unbuffered. Note that, unlike in Go, channels are untyped. It would be

perfectly okay to pass values of different types over a single channel, as long as they fit into sz bytes. Also note that the current implementation does not allow all combinations of sz and n. This is because the underlying allocator (part of RCCE) works with cache line granularity, so we have to make sure that channel buffers occupy multiples of 32 bytes ((n+1)\*sz must be a multiple of 32).

void channel\_free (Channel \*ch);

Frees the MPB memory associated with channel ch.

**bool** channel\_send(Channel \*ch, **void** \*data, **size\_t** sz); Sends an element of sz bytes at address data to channel ch. The call blocks until the element has been stored in the channel buffer (buffered channel) or until the element has been received from the channel (unbuffered channel).

**bool** channel\_receive (Channel \*ch, **void** \*data, **size\_t** sz); Receives an element of sz bytes from channel ch. The element is stored at address data. The call blocks if the channel is empty.

Additionally, we find the following functions useful:

int channel owner(Channel \*ch);

Returns the ID of the worker that allocated and thus "owns" channel ch.

bool channel\_buffered(Channel \*ch);

Returns true if ch points to a buffered channel, otherwise returns false.

**bool** channel unbuffered (Channel \*ch);

Returns true if ch points to an unbuffered channel, otherwise returns false.

# unsigned int channel\_peek(Channel \*ch);

Returns the number of buffered items in channel ch. When called with an unbuffered channel, a return value of 1 indicates that a sender is blocked on the channel waiting for a receiver.

unsigned int channel\_capacity (Channel \*ch);

Returns the capacity (buffer size) of channel ch (0 for unbuffered channels).

# D. Go Statements

Go statements must be translated into standard C code that interfaces with our runtime library. Listing 1 gives an idea of the translation process. Suppose we start a goroutine running function f(in, out), which operates on two channels in and out. For every function that is started as a goroutine, we generate two wrapper functions, one for creating and enqueuing the goroutine (task), the other for running it after scheduling. Listing 1 shows the corresponding code in slightly abbreviated form. Function go\_f creates a task saving all the goroutine's arguments and enqueues the task for asynchronous

```

void f(Channel *in, Channel *out);

// The go statement

go f(in, out):

// is rewritten into

go_f(in, out);

with the following definition

// (some details are left out for brevity)

void go_f(Channel *in, Channel *out)

Task task:

f\_task\_data \ *td;

task.fn = (void (*)(void *)f_task_func;

td = (f_task_data *)task.data;

td->in_owner = channel_owner(in);

td->in_offset = MPB_data_offset(td->in_owner, in);

td->out_owner = channel_owner(out);

td->out_offset = MPB_data_offset(td->out_owner, out);

// The data structure to hold the goroutine's arguments

typedef struct f_task_data {

int in_owner, in_offset;

int out_owner, out_offset;

} f_task_data;

// is passed to the task function that wraps the call to f

void f_task_func(f_task_data *args)

Channel *in, *out;

in = MPB_data_ptr(args->in_owner, args->in_offset);

out = MPB_data_ptr(args->out_owner, args->out_offset);

```

Listing 1: A go statement and the translation into tasking code.

execution. Channel references are constructed from channel owner and MPB offset pairs (required to break with the collective allocations model of RCCE, described above), so each channel is internally represented by two integers. The helper functions MPB\_data\_offset and MPB\_data\_ptr calculate offsets and pointers based on the MPB starting addresses in RCCE\_comm\_buffer. The task function f\_task\_func is called by the runtime when the task is scheduled for execution, after which the goroutine is up and running.

# V. EXAMPLE: PARALLEL GENETIC ALGORITHM

To demonstrate the use of goroutines and channels, we have written a parallel genetic algorithm (PGA) that can utilize all the cores of the SCC. We follow the island model and evolve a number of populations in parallel, with occasional migration of individuals between neighboring islands [13].

We choose a simple toy problem: evolving a string from random garbage in the ASCII character range between 32 and 126. More precisely, we want to match the following string that represents a simple "Hello World!" program:

```

"#include <stdio.h> int main(void) { printf("Hello SCC!\n"); return 0; }"

```

The fitness of a string is calculated based on a character by character comparison with the target string, according to  $f = \sum_{i=0}^{n} (\operatorname{target}[i] - \operatorname{indiv}[i])^2$ , where n is the length of both strings. Thus, higher fitness values correspond to less optimal

```

void evolve(Channel *chan, Channel *prev_in,

Channel *prev_out, int n, int num_islands)

{

GA_pop *island;

Channel *in, *out;

if (n < num_islands - 1) {

in = channel_alloc(sizeof(GA_indv), 0);

out = channel_alloc(sizeof(GA_indv), 0);

go evolve(chan, in, out, n + 1, num_islands);

}

island = GA_create(island_size, target);

while (GA_evolve(island, migration_rate))

migrate(island, n, prev_in, prev_out, in, out);

channel_send(chan, &island->indvs[0], sizeof(GA_indv));

GA_destroy(island);

}

```

Listing 2: Populations evolve concurrently in goroutines.

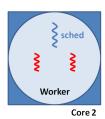

Fig. 4. An example of migration between four islands of a parallel genetic algorithm. Individuals are exchanged over channels in two steps: (1) odd numbered islands send to even numbered neighbors, and (2) even numbered islands send to odd numbered neighbors.

solutions, and our goal is to find the string with the fitness value 0.

Listing 2 shows the code to evolve an island. The GA\_\* procedures to create, evolve, and destroy a population are not specific to the SCC but part of our generic GA implementation.<sup>2</sup> Islands are created one after another, each in a new goroutine. The main thread of the program starts the evolution by allocating a channel chan, on which the solution will be delivered, and creating the first goroutine with

```

go evolve(chan, NULL, NULL, 0, num_islands);

```

Because the main thread cannot run goroutines, it will block until the evolution has finished when it attempts to receive from chan.

After every migration\_rate generations, we migrate two individuals that we pick at random from the current population to neighboring islands. To exchange individuals between two islands a and b, we need two channels: one for sending individuals from a to b, the other vice versa for sending individuals from b to a. Every island other than the first and last has two neighbors and, thus, four channel references to communicate with its neighbors.

<sup>2</sup>The core of the GA uses tournament selection, one-point crossover of selected individuals, and random one-point mutation of offspring individuals.

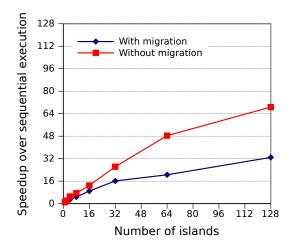

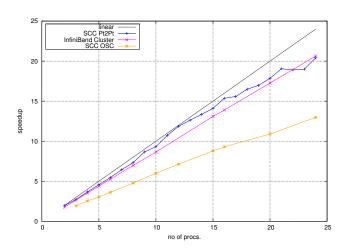

Fig. 5. Speedup with multiple islands over the sequential execution with one island. The total population across all islands has a size of 1280 (island size = 1280 / number of islands). The migration rate is two individuals every ten generations.

Figure 4 illustrates what happens during migration. The example shows four islands numbered from 0 to 3 and the channels between them. Migration is a two-step process. We use unbuffered, synchronizing channels, which require a rendezvous between sender and receiver. First, odd numbered islands send their individuals, while even numbered islands receive in the matching order. Then the process of sending and receiving is reversed.

Figure 5 shows the speedups we have measured for a fixed population size of 1280.<sup>3</sup> Sequential execution refers to the case where we evolve only one island, so everything runs inside a single goroutine. When the number of goroutines exceeds the number of available worker threads, goroutines are multiplexed onto worker threads. Up to the total number of cores (48), we make sure that every new goroutine runs on a separate core, so that goroutines actually run in parallel (though the runtime doesn't allow us to control on which core a goroutine starts execution). Creating more goroutines than we have cores is no problem; the runtime scheduler switches between goroutines whenever active goroutines block on channels during migration.

The toy problem is simple enough that we don't actually need a sophisticated GA that migrates individuals between islands in order to maintain genetic diversity. The same algorithm leaving out migration and instead just switching between goroutines after every migration\_rate generations achieves even higher speedups.

# VI. CONCLUSION

We have presented an implementation of goroutines and channels, the building blocks for concurrent programs in the Go programming language. Both Go and the SCC share the basic idea of communicating and synchronizing over messages rather than shared memory. The Go slogan "Do

<sup>3</sup>SCC in default configuration: cores running at 533 MHz, mesh and DDR memory at 800 MHz (Tile533\_Mesh800\_DDR800).

not communicate by sharing memory; instead, share memory by communicating" is a good one to keep in mind when programming the SCC. Communication over channels is akin to message passing, but channels are much more flexible in the way they serve to synchronize concurrently executing activities.

Channels can be implemented efficiently using the available hardware support for low-latency messaging. However, problems are likely the small size of the on-chip memory and the small number of test-and-set registers. The size of the MPB (basically 8 KB per core) limits the number of channels that can be used simultaneously, as well as the size and number of data items that can be buffered on-chip. With only 48 test-and-set registers at disposal, allocating many channels can increase false contention because the same test-and-set locks are used for several unrelated channels. As a result, communication latency can suffer. We could support a much larger number of channels in shared off-chip memory, trading off communication latency, but frequent access to shared off-chip DRAM could turn into a bottleneck by itself.

### ACKNOWLEDGMENT

We thank Intel for granting us access to the SCC as part of the MARC program. Our work is supported by the Deutsche Forschungsgemeinschaft (DFG).

#### REFERENCES

- [1] "The Go Programming Language," http://golang.org. [Online]. Available: http://golang.org

- [2] "Many-core Applications Research Community," http://communities. intel.com/message/113676#113676. [Online]. Available: http://communities.intel.com/message/113676#113676

- [3] "Many-core Applications Research Community," http://communities. intel.com/message/115657#115657. [Online]. Available: http://communities.intel.com/message/115657#115657

- [4] C. A. R. Hoare, "Communicating Sequential Processes," Commun. ACM, vol. 21, pp. 666–677, August 1978. [Online]. Available: http://doi.acm.org/10.1145/359576.359585

- [5] —, Communicating Sequential Processes. Upper Saddle River, NJ, USA: Prentice-Hall, Inc., 1985.

- [6] "The Go Programming Language Specification," http://golang.org/doc/go\_spec.html. [Online]. Available: http://golang.org/doc/go\_spec.html

- [7] T. G. Mattson, R. F. van der Wijngaart, M. Riepen, T. Lehnig, P. Brett, W. Haas, P. Kennedy, J. Howard, S. Vangal, N. Borkar, G. Ruhl, and S. Dighe, "The 48-core SCC Processor: the Programmer's View," in Proceedings of the 2010 ACM/IEEE International Conference for High Performance Computing, Networking, Storage and Analysis, ser. SC '10. Washington, DC, USA: IEEE Computer Society, 2010, pp. 1–11. [Online]. Available: http://dx.doi.org/10.1109/SC.2010.53

- [8] R. F. van der Wijngaart, T. G. Mattson, and W. Haas, "Light-weight Communications on Intel's Single-Chip Cloud Computer Processor," SIGOPS Oper. Syst. Rev., vol. 45, pp. 73–83, February 2011.

- [9] A. Prell and T. Rauber, "Task Parallelism on the SCC," in *Proceedings of the 3rd Many-core Applications Research Community (MARC) Symposium*, ser. MARC 3. KIT Scientific Publishing, 2011, pp. 65–67.

- [10] R. S. Engelschall, "Portable Multithreading: The Signal Stack Trick for User-Space Thread Creation," in *Proceedings of the annual conference* on USENIX Annual Technical Conference, ser. ATEC '00. Berkeley, CA, USA: USENIX Association, 2000, pp. 20–20. [Online]. Available: http://dl.acm.org/citation.cfm?id=1267724.1267744

- [11] "A Tutorial for the Go Programming Language," http://golang.org/doc/go\_tutorial.html. [Online]. Available: http://golang.org/doc/go\_tutorial.html

- [12] "Go Emerging Languages Conference Talk," http://www.oscon.com/ oscon2010/public/schedule/detail/15299, July 2010. [Online]. Available: http://www.oscon.com/oscon2010/public/schedule/detail/15299

- [13] E. Cantú-Paz, "A Survey of Parallel Genetic Algorithms," Calculateurs Paralleles, Reseaux et Systems Repartis, vol. 10, 1998.

# Performance of RDF Query Processing on the Intel SCC

Vasil Slavov, Praveen Rao, Dinesh Barenkala, and Srivenu Paturi

Abstract—Chip makers are envisioning hundreds of cores in future processors for throughput oriented computing. These processors, called manycore processors, require new architectural innovations for scaling to a large number of cores as compared with today's multicore processors. We report an early study on the performance of RDF query processing on a manycore processor. In our study, we use the Intel SCC, an experimental manycore processor from Intel Labs. This processor has new architectural features, namely, 48 Pentium cores, a high speed, on-chip mesh network to communicate between cores and access memory controllers, on-chip message passing buffers for high speed message passing, and software controlled fine-grained power management. We classify queries based on their I/O footprint and study the impact of two standard models, namely, task and data parallel programming models. Based on our experiments with synthetic and real RDF datasets on the SCC, we conclude that the task parallelism model provides an immediate way to boost the performance of RDF query processing.

# I. INTRODUCTION

Chip makers are envisioning hundreds of cores in future processors for throughput oriented computing. In throughput oriented computing, we expect abundant parallelism opportunities in the workload, and aim to achieve high throughput using a large number of simple cores, while compromising the latency on individual cores [1]. A processor with such large number of cores is called a manycore processor. The cores may be homogeneous or heterogeneous. New architectural innovations for faster on-chip communication and efficient power management are necessary to scale to a large number of cores as compared with today's multicore processors.

In recent years, a few manycore prototypes have emerged (e.g., 80 core processor called Polaris [2], Larrabee [3], Intel Single-chip Cloud Computer (SCC) [4]). Of particular interest to us is the Intel SCC, an experimental manycore processor from Intel Labs. This processor has new architectural features, namely, 48 Pentium cores, a high speed, on-chip mesh network to communicate between cores and access memory controllers, on-chip message passing buffers for high speed message passing, and software controlled fine-grained power management.

In this work, we attempt to understand the benefits and limitations of the SCC for parallel RDF query processing. RDF

- V. Slavov is with the Department of Computer Science and Electrical Engineering, University of Missouri-Kansas City. E-mail: vgslavov@mail.umkc.edu

- P. Rao is with the Department of Computer Science and Electrical Engineering, University of Missouri-Kansas City. E-mail: raopr@umkc.edu

- D. Barenkala is with the Department of Computer Science and Electrical Engineering, University of Missouri-Kansas City. E-mail: db985@mail.umkc.edu

- S. Paturi is with the Department of Computer Science and Electrical Engineering, University of Missouri-Kansas City. E-mail: sp895@mail.umkc.edu

(Resource Description Framework) is a popular language for representing data on the Web [5]. It enables the interchange and machine processing of data by considering its semantics. The essence of RDF lies in the notion of representing any fact as *subject*, *predicate*, and *object*. Formally, RDF represents resources as a directed, labeled graph where a pair of adjacent nodes denotes two things and the directed, labeled edge represents their relationship. The source node denotes the subject; the sink node denotes the object; and the edge label is the predicate (or property). This "subject-predicate-object" relationship is commonly referred to as an RDF triple. SPARQL is a popular query language for RDF graphs [6]. Using SPARQL, complex graph pattern queries can be expressed on individual RDF graphs as well as across multiple RDF graphs.

In recent years, the RDF data model has become increasingly important in domain-specific applications and the WWW. Through RDF technologies, one can reason over semantic data, which is highly appealing in domains such as healthcare, defense and intelligence, biopharmaceuticals, and so forth. With the rapidly growing size of RDF datasets (e.g., DBPedia [7], Billion Triples Challenge [8]), there is a pressing need for high performance RDF processing tools. With the emergence of manycore processors, it is natural and timely to ask whether a manycore processor can boost the performance of RDF query processing - through parallel processing. To the best of our knowledge, there is no published work in this area. Recent studies on the Intel SCC have focused on low level aspects such as on-chip message passing performance, memory access latency, and power and energy consumption on benchmarks from high performance computing [4], [9].

In our study, we adopt standard task parallel and data parallel programming models for parallel RDF query processing. We categorize RDF queries on real and synthetic RDF datasets into two different query workloads based on their I/O footprint – one with small I/O footprint queries and the other with large I/O footprint queries. We study the effect of inter-query parallelism via the task parallel programming model on these workloads. We also study the effect of intra-query parallelism via the data parallel programming model on these workloads.

The rest of the paper is organized as follows. We present background and related work in Section II; we present the methodology of our study in Section III; we present the empirical findings in Section IV; and we conclude in Section V with a note on future work.

# II. PRIOR WORK ON RDF QUERY PROCESSING

Today, there are a number of open-source and commercial tools for storing and querying RDF graphs. These tools either

store and process RDF in main-memory, use an RDBMS, or a native RDF database. The popular approach has been to use relational database systems for storing, indexing, and querying RDF [10], [11], [12], [13], [14], [15]. Abadi *et al.* proposed a vertical partitioning approach and leveraged a column-oriented DBMS for achieving an order of magnitude performance improvement over previous techniques [16].

RDF-3X [17] and Hexastore [18] demonstrated that storing RDF data in a single triples table and building exhaustive indexes on the six permutations of (s,p,o) triples can significantly outperform the vertical partitioning approach [16] and also support a larger class of RDF queries efficiently. Recently, BitMat [19] was proposed to overcome the overhead of large intermediate join results in RDF-3X and Hexastore when queries contain low selectivity triple patterns. (Low selectivity implies large result set size.)

There are some RDF stores that operate in shared-nothing clusters (e.g., YARS2 [20], 4store [21], Clustered TBD [22]) by hashing triples/quadruples and distributing them on different nodes in the cluster. Parallel query processing is performed. The scalability of these approaches has been demonstrated on small sized clusters. Weaver et al. [23] have studied RDF query processing on supercomputers. More recently, tools for data intensive computing such as Apache Hadoop and Pig have been used for query processing and analytics over RDF data [24], [25], [26]. These approaches are more suitable for batch processing of queries. A few researchers have focused on parallel RDF reasoning [27], [28]. More recently, Huang et al., developed parallel RDF query processing techniques for large RDF graphs [29].

On the Intel SCC, Vidal *et al.*, studied the parallelization of an AI automated planner using a hash-based distribution of tasks [30]. Petrides *et al.*, studied the performance of relational decision support queries on the SCC [31]. However, none of the previous work has studied the performance impact of parallel RDF query processing on the Intel SCC.

# III. OUR METHODOLOGY

In this section, we introduce our methodology for parallel RDF query processing on the SCC. Our first approach is to express inter-query parallelism via the task parallel programming model. Our second approach is to express intra-query parallelism via the data parallel programming model. While we adopt standard techniques for task and data parallelism, these techniques provide good insights into the benefits and limitations of the Intel SCC for RDF query processing. The query workloads we study are I/O bound in nature, unlike prior work on SCC [4], [9], which focused on high performance computing benchmarks. We consider two different types of query workloads: one that has relatively smaller I/O footprint and the other that has relatively larger I/O footprint.

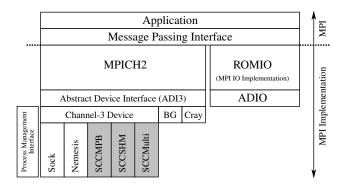

# A. Message Passing Interface

We use the popular Message Passing Interface (MPI) for writing parallel programs. MPI contains a standard library of routines for writing portable message-passing based programs. The MPI routines that we used for the task parallel and data parallel programming models are listed in Table I. MPI programs essentially create a collection of processes. MPI\_Send and MPI\_Recv allow a process to exchange messages with another process (point-to-point communication); MPI\_Barrier enables processes to synchronize at certain points during execution; and MPI\_Bcast, MPI\_Scatter, and MPI\_Gatherv are collective communication operations, which allow a process to communicate with a group of other processes.

## B. Impact of Granularity

In parallel computing, granularity denotes the ratio between the amount of computation to the amount of communication. In fine-grained parallelism, we break a problem into relatively smaller sized computation tasks and therefore, may require more frequent communication between processors. In coarsegrained parallelism, we break a problem into relatively larger sized computation tasks and therefore reduce the frequency of communication between processors. However, fine-grained parallelism enables better load balancing than coarse-grained parallelism. But it may increase communication cost and synchronization overhead. By design, Intel SCC provides a high speed, on-chip network to enable fast communication between cores. Therefore, we attempt to partition the tasks as fine-grained as possible in our experiments. Because the query workloads we study are I/O bound, we use the I/O footprint to characterize the granularity of a task.

| MPI routines | Usage                                          |

|--------------|------------------------------------------------|

| MPI_Send     | Is called when a process wants to send a       |

|              | message in its local buffer to another process |

| MPI_Recv     | Is called when a process wants to receive a    |

|              | message from another process                   |

| MPI_Barrier  | Is called by a process to enter a barrier      |

| MPI_Bcast    | Is called by a process to broadcast the        |

|              | message to all processes in the group          |

| MPI_Scatter  | Is called by a process to scatter an array of  |

|              | data items to other processes                  |

| MPI_Gatherv  | Is called by all processes in the group        |

|              | (one receiver, multiple senders) so that       |

|              | the receiver can collect different sized       |

|              | messages from the senders synchronously        |

TABLE I MPI ROUTINES USED

# C. Task Parallel Programming Model

We express inter-query parallelism via a straightforward task parallel programming model. Each query is regarded as a task. Our model is as follows. On one core, we run the master and on the other cores, we run workers. Algorithm 1 describes the set of actions performed by the master and workers. Lines 1-1 denote the actions taken by the master. Lines 1-1 denote the actions taken by a worker. The master maintains a single task pool. Once the master and workers have started (as MPI processes), each worker sends a message to the master. The master responds to a worker with a query from the task pool. The worker then executes the query locally on the index. (The index is constructed over the entire dataset and is shared by the workers.) Once completed, the worker

# Algorithm 1: Task parallel programming model

```

proc @Master()

1: Create a query pool from a list of SPARQL queries to

while query pool is not empty do

3:

MPI_Recv(workerid)

4:

Remove a SPARQL query q from the pool

MPI_Send(workerid, q)

5:

6: execute MPI_Barrier

end

proc @Worker()

7: while true do

MPI_Send(master) to request a query

8:

9:

q \leftarrow \text{MPI\_Recv(master)}

10:

if q == EOF then

break

11:

else

Execute q locally using the index

12:

13: execute MPI Barrier

end

```

repeats the process of requesting and executing queries from the master until the master informs that there are no more queries to execute. Once the master and workers reach the barrier, the task pool has been completely processed.

# D. Data Parallel Programming Model

We express intra-query parallelism via a straightforward data parallel programming model. The task of processing a query on the entire dataset is broken down into subtasks, where each subtask consists of executing the query on a different partition of the dataset. Our model for data parallelism is as follows. First, we partition the underlying RDF graph into smaller graphs. We do this by extracting weakly connected directed subgraphs and applying standard graph partitioning techniques if necessary (e.g., METIS [32]). If graph partitioning is applied, then we aim to minimize the number of cut edges. We replicate the cut edges in the partitions. (We ignore the directionality of the edges in the graph while partitioning and assume each edge has unit weight.) In our approach, we may miss results. While overcoming this is a non-trivial research challenge, our goal here is to test whether using partitioned indexes on multiple cores during query processing can provide good speedup for the best case scenario.

Similar to the task parallelism approach described earlier, on one core we run the master, and on the others we run workers. The master selects a query and broadcasts it to the workers and also provides each worker with a bucket id to use during query processing. Each worker executes the query locally on the data in the specified bucket. The partial results are returned to the master. Collecting the results can be done either by sending multiple messages one at a time to the master or using the collective operation MPI\_Gatherv. Algorithm 2 describes the steps involved. The master and the workers reach a barrier before the next query is processed.

# IV. PERFORMANCE EVALUATION

We used RDF-3X [17], a state-of-the-art RDF query processing engine in our evaluation. RDF-3X was implemented in

Algorithm 2: Data parallel programming model

```

proc @Master()

1: foreach SPARQL query q do

Let Bid[] denote an array of bucket ids

2:

MPI_Scatter(Bid[]) /* Send a different bucket id to

3:

each worker */

MPI_Bcast(q) /* Send the same query to each worker

4:

MergeResults()

5:

end

proc @ Worker()

6: while true do

p \leftarrow \text{MPI\_Scatter}() /* A \text{ worker receives one bucket}

id */

q \leftarrow \text{MPI\_Bcast}() /* Every worker receives the same

8:

query */

9:

Execute q locally on the index for bucket p

MergeResults()

10:

end

proc MergeResults()

11: if Master then

Collect results from workers using multiple

MPI_Recv or single MPI_Gatherv

else

Send results to master using multiple MPI_Send or

13:

single MPI_Gatherv

14: execute MPI_Barrier

end

```

C++ and was compiled to run on the SCC using a 32 bit GCC compiler. The SCC cores ran Linux and had a NFS mounted file system where the indexes were stored. We did not modify the memory organization/configuration of the SCC and used the default setting.

We implemented the task and data parallel programming models described in Algorithms 1 and 2 using RCKMPI, a modified MPICH2 for the Intel SCC [33]. RCKMPI uses the message passing buffers (MPBs) in the SCC to allow low latency high bandwidth message passing. The SCC platform was initialized to run with tile frequency of 800 MHz, mesh frequency of 800 MHz, and memory controller frequency of 800 MHz.

# A. Dataset and Queries

We used two real datasets, namely, YAGO2 [34] and Uniprot [35]. YAGO2 is a semantic knowledge base derived from Wikipedia, WordNet, and Geonames. Uniprot is a comprehensive resource for protein sequence and annotation data. We also generated a synthetic dataset using the Lehigh University Benchmark (LUBM) [36]. The ontology for this dataset is based on a university domain.

Note that the SCC cores generate 32 bit addresses. RDF-3X leverages memory mapping of index files and therefore, recommends 64 bit processors for indexing and querying large RDF datasets. To cope with the 32 bit addressing on the SCC, we indexed a set of triples in each dataset such that the index size was at most 2GB in size, a limit set by the underlying OS. This ensured that RDF-3X successfully ran the queries on the SCC. For YAGO, we indexed 27,331,797 triples; for Uniprot, we indexed 46,972,851 triples; and for LUBM, we

| Query  | Dataset | I/O        | Type  | %   | Serial      |

|--------|---------|------------|-------|-----|-------------|

|        |         | footprint  |       | CPU | time        |

| $QY_1$ | YAGO    | 14,756 KB  | small | 29  | 4.73 secs   |

| $QY_2$ | YAGO    | 15,004 KB  | small | 40  | 9.23 secs   |

| $QY_3$ | YAGO    | 22,832 KB  | small | 29  | 6.51 secs   |

| $QY_4$ | YAGO    | 33,492 KB  | small | 21  | 9.27 secs   |

| $QY_5$ | YAGO    | 216,564 KB | large | 22  | 82.65 secs  |

| $QY_6$ | YAGO    | 272,848 KB | large | 30  | 120.08 secs |

| $QY_7$ | YAGO    | 332,944 KB | large | 43  | 218.43 secs |

| $QL_1$ | LUBM    | 2,668 KB   | small | 25  | 1.4 secs    |

| $QL_2$ | LUBM    | 3,132 KB   | small | 35  | 1.47 secs   |

| $QL_3$ | LUBM    | 9,804 KB   | small | 19  | 3.5 secs    |

| $QL_4$ | LUBM    | 636,204 KB | large | 32  | 299.99 secs |

| $QL_5$ | LUBM    | 673,924 KB | large | 29  | 206.58 secs |

| $QU_1$ | Uniprot | 4,468 KB   | small | 39  | 2.08 secs   |

| $QU_2$ | Uniprot | 10,344 KB  | small | 39  | 6.46 secs   |

| $QU_3$ | Uniprot | 48,020 KB  | large | 31  | 19.39 secs  |

| $QU_4$ | Uniprot | 62,188 KB  | large | 19  | 15.48 secs  |

| $QU_5$ | Uniprot | 166,808 KB | large | 17  | 43.51 secs  |

TABLE II INITIAL EVALUATION OF QUERIES

indexed 35,612,176 triples. (The SPARQL queries used for the experiments are listed in a technical report [37].)

# B. Query Workload Classification

The queries used in our evaluation are I/O bound in nature. Using the iostat command, we measured the I/O footprint of each query. (We dropped the file system buffer cache before running each query by issuing echo 3 > /proc/sys/vm/drop\_caches.) Based on the I/O footprint, we classified the queries into two categories, small and large. Queries that were classified small had relatively smaller I/O footprint. Queries that were classified large had relatively larger I/O footprint. Table II shows the queries and their classification after running each query serially. (The block size used by the filesystem was 4096 bytes.) In addition, the serial time (on a single core) and the % CPU utilization for each query is shown. Queries that had higher CPU utilization (e.g.,  $QY_7$ ), typically returned more results. Note that internally RDF-3X stores long string literals in a mapping dictionary, and uses ids in the indexes. At the end of query processing, it maps back these ids to literals using the dictionary. For queries returning large number of results, this cost of mapping becomes non-negligible [17].

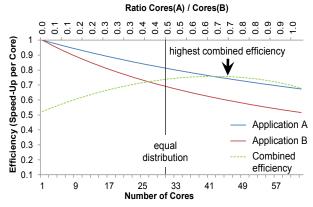

# C. Evaluation Metrics

We measured the effectiveness of parallel RDF query processing by computing the speedup and efficiency as the number of available cores was increased. Suppose  $T_s$  is the time taken to execute a workload of SPARQL queries on a single SCC core. Suppose  $T_p$  is the time taken to execute the queries in parallel (using either data or task parallel programming models) on n SCC cores. (On n cores, we run one master and n-1 workers.) The speedup on n cores is computed by the ratio  $\frac{T_s}{T_p}$ ; the efficiency on n cores is computed by the ratio  $\frac{speedup}{n}$ .

# D. Data Partitioning Approach

For the data parallel programming model, we partitioned a dataset depending on how many cores were available to run the workers. (Note that partitioning was done once before executing all the queries.) Each worker was assigned one partition and used the index for that partition during query processing. Different approaches were followed for each of the three datasets. The main goal was to assign the triples corresponding to weakly connected directed subgraphs in the RDF graph into buckets. For LUBM, as the generator produced separate RDF files, we grouped the triples from one file and placed it in a bucket. All the files were distributed across the buckets in a round-robin fashion. For Uniprot, we had one single XML/RDF file, and we created fragments of this XML file at points where a new protein was described. The triples from each fragment were stored together in a bucket. All the fragments were distributed across the buckets in a round-robin fashion.

The YAGO2 dataset was available in N-Triples format. First, we extracted graphs of a particular type from the dataset, which we call star-shaped graphs. A star-shaped graph is a weakly connected directed graph, where the degree of all vertices except one is exactly 1. All the triples from a star-shaped graph were put into a bucket. On the remaining non-star graphs, we ran the METIS [32] algorithm to partition the graphs. After obtaining n partitions, we assigned the triples for each partition into one bucket. (We replicated the cut edges in each partition.) As mentioned earlier, our approach may miss results.

# E. Results

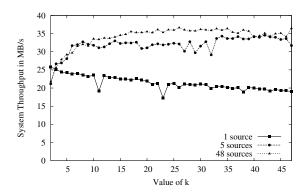

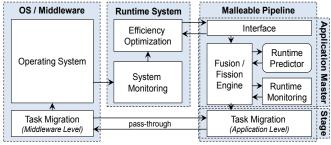

We focus on four possible combinations of workload and parallel programming models, namely, ST (small I/O footprint, task parallelism), LT (large I/O footprint, task parallelism), SD (small I/O footprint, data parallelism), and LD (large I/O footprint, data parallelism). We will refer to these as the ST, LT, SD, and LD models in subsequent discussions. Note that all I/O requests go through the MCPC connected to the SCC platform via the PCIe bus. We measured wall clock time by ensuring a cold cache scenario. (We dropped the file system buffer cache before a query was executed on a core.)

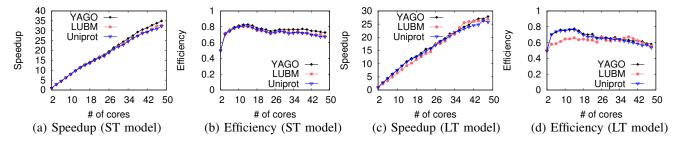

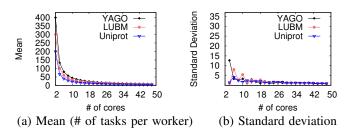

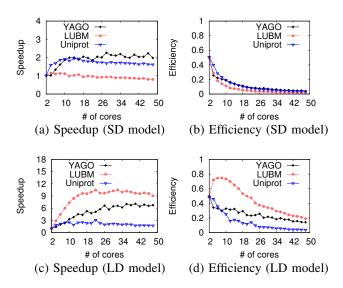

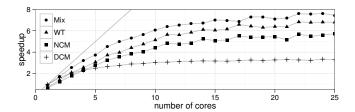

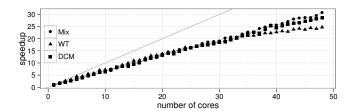

1) The ST Model: The query workload for each dataset consisted of queries marked small in Table II. The task pool consisted of these queries put in order and scaled by a factor of 100. (For example, the task pool for YAGO consisted of queries  $QY_1$ ,  $QY_2$ ,  $QY_3$ ,  $QY_4$ , ...,  $QY_1$ ,  $QY_2$ ,  $QY_3$ ,  $QY_4$ , ....) Figure 1(a) shows the speedup obtained for parallel RDF query processing using Algorithm 1. On 48 cores (1 master + 47 workers), a promising speedup of 34.92, 32.74, and 32.27 was obtained for YAGO, LUBM, and Uniprot, respectively. Figure 1(b) shows the efficiency. For all three datasets, the efficiency reached close to 70% on 48 cores. The tasks were relatively fine-grained due to their small I/O footprints and were well distributed across the workers. There was effective load balancing of tasks across the workers resulting in good speedup and efficiency. (This is evident from the mean and standard deviation of the number of tasks processed by each

Fig. 1. Results for the task parallel programming model

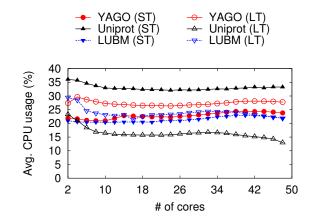

worker as shown in Figures 2(a) and 2(b).) As shown in Figure 4, the average CPU utilization varied marginally (from 2 to 48 cores), indicating negligible I/O contention in ST.

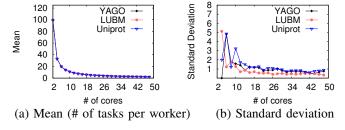

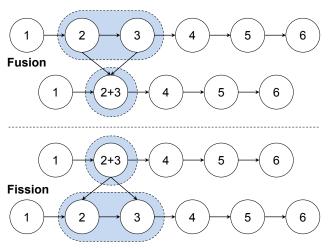

- 2) The LT Model: The query workload for each dataset consisted of queries marked large in Table II. Similar to ST, the task pool consisted of these queries put in order and scaled by a factor of 33, 50, and 33 for YAGO, LUBM, and Uniprot, respectively. Figures 1(c) and 1(d) show the speedup and efficiency for parallel RDF query processing using Algorithm 1. On 48 cores, the speedup ranged between 25 to 30 for the three datasets. This is promising given that the queries had larger I/O footprint than those used in the ST model. The load was fairly well distributed across the workers. (See Figures 3(a) and 3(b).) As shown in Figure 4, the drop in the average CPU utilization (from 2 to 48 cores) was higher for LUBM and Uniprot as compared to YAGO, indicating higher I/O contention for these datasets.

- 3) The SD Model: The query workload for each dataset consisted of queries marked small in Table II. Each query was run multiple times using Algorithm 2. Although the data parallel approach created fine-grained tasks for a query with increasing number of cores, there was load imbalance as many of the workers returned no results on their partitions. This resulted in poor speedup and efficiency as the number of cores was increased. We show the plots in Figures 5(a) and 5(b).

- 4) The LD Model: The query workload for each dataset consisted of queries marked large in Table II. Each query was run multiple times using Algorithm 2. As more cores were used to process a query, I/O contention became an issue. This is evident from the fact that the average CPU utilization for LD was lower than that for LT on all datasets. As a result, poor speedup and efficiency were obtained. We show the plots in Figures 5(c) and 5(d).

Fig. 2. Load distribution - ST model

Fig. 3. Load distribution - LT model

Fig. 4. Average CPU usage with increasing number of cores

# F. Summary of Results on the SCC

- The task parallel programming model yielded good speedup and efficiency for parallel RDF query processing. This was true for both small I/O and large I/O footprint queries. The ST model, however, gave better results than the LT model.

- Although the data parallel programming model created fine-grained tasks, the speedup and efficiency for both the SD and LD models were poor due to either load imbalance or I/O contention. Further research is necessary to address these issues.

# V. CONCLUSIONS AND FUTURE WORK

We have presented an early study of the performance of parallel RDF query processing on the Intel SCC, an experimental manycore processor. Using real and synthetic RDF datasets, we studied how inter-query parallelism (via

Fig. 5. SD and LD models

the task parallel programming model) and the intra-query parallelism (via the data parallel programming model) affected the performance of RDF query processing. We conclude that the task parallel model provides an immediate way to boost the query processing performance. In the future, we plan to develop new RDF query processing strategies to overcome the challenges posed by the data parallel programming model. We would also like to study the effect of dynamic voltage and frequency scaling of the SCC cores on the performance of RDF query processing.

# ACKNOWLEDGEMENTS

We are grateful to the MARC team at Intel Labs for granting us access to the SCC hardware and related software tools. Special thanks to Mark Aughenbaugh and Ted Kubaska for their prompt help. This work was supported in part by a grant from the National Science Foundation (IIS-1115871).

## REFERENCES

- [1] M. Garland and D. B. Kirk, "Understanding Throughput-Oriented Architectures," *Commun. of ACM*, vol. 53, pp. 58–66, November 2010.

- S. Vangal, J. Howard, G. Ruhl, S. Dighe, H. Wilson, J. Tschanz, D. Finan, P. Iyer, A. Singh, T. Jacob, S. Jain, S. Venkataraman, Y. Hoskote, and N. Borkar, "An 80-Tile 1.28TFLOPS Network-on-Chip in 65nm CMOS," in Solid-State Circuits Conference, 2007, pp. 98-589.

- L. Seiler, D. Carmean, E. Sprangle, T. Forsyth, M. Abrash, P. Dubey, S. Junkins, A. Lake, J. Sugerman, R. Cavin, R. Espasa, E. Grochowski, T. Juan, and P. Hanrahan, "Larrabee: A Many-Core x86 Architecture for Visual Computing," ACM Transactions on Graphics, vol. 27, pp. 18:1-18:15, August 2008.

- [4] T. Mattson, R. Van der Wijngaart, M. Riepen, T. Lehnig, P. Brett, W. Haas, P. Kennedy, J. Howard, S. Vangal, N. Borkar, G. Ruhl, and S. Dighe, "The 48-core SCC Processor: the Programmer's View," in *Proc. of Intl. Conf. for High Performance Computing, Networking, Storage and Analysis*, Nov 2010, pp. 1–11. "Resource Description Framework (RDF)," http://www.w3.org/RDF.

- "SPARQL Query Language for RDF," http://www.w3.org/TR/rdf-sparql-

- query/. C. Bizer, J. Lehmann, G. Kobilarov, S. Auer, C. Becker, R. Cyganiak, and S. Hellmann, "DBpedia - A crystallization point for the Web of Data," Journal of Web Semantics: Science, Services and Agents on the World Wide Web, vol. 7, no. 3, pp. 154–165, September 2009. "Semantic Web Challenge," http://challenge.semanticweb.org/.

- [9] P. Gschwandtner, T. Fahringer, and R. Prodan, "Performance Analysis and Benchmarking of the Intel SCC," in Proc. of Intl. Conf. on Cluster

- Computing, Sept. 2011, pp. 139–149.

K. Wilkinson, C. Sayers, H. A. Kuno, and D. Reynolds, "Efficient RDF Storage and Retrieval in Jena2," in Proc. of SWDB'03, 2003, pp. 131-

- [11] S. Harris and N. Gibbins, "3store: Efficient Bulk RDF Storage," in

- Practical and Scalable Semantic Systems, 2003.

[12] J. Broekstra, A. Kampman, and F. van Harmelen, "Sesame: A Generic

- Architecture for Storing and Querying RDF and RDF Schema," in *Proc. of ISWC '02*, pp. 54–68.

[13] E. I. Chong, S. Das, G. Eadon, and J. Srinivasan, "An Efficient SQL-Based RDF Querying Scheme," in *Proc. of the 31st VLDB Conference*, Trondheim, Norway, 2005, pp. 1216–1227.

- [14] L. Ma, Z. Su, Y. Pan, L. Zhang, and T. Liu, "RStar: an RDF storage and query system for enterprise resource management," in *Proc. of CIKM* '04, Washington, D.C., USA, 2004, pp. 484–491.

[15] J. J. Levandoski and M. F. Mokbel, "RDF Data-Centric Storage," in

- Proc. ICWS '09, Washington, DC, 2009, pp. 911–918

- [16] D. J. Abadi, A. Marcus, S. R. Madden, and K. Hollenbach, "Scalable Semantic Web Data Management Using Vertical Partitioning," in *Proc. of the 33rd VLDB Conference*, 2007, pp. 411–422.

[17] T. Neumann and G. Weikum, "The RDF-3X engine for scalable man-

- agement of RDF data," The VLDB Journal, vol. 19, no. 1, pp. 91-113,

- C. Weiss, P. Karras, and A. Bernstein, "Hexastore: Sextuple Indexing for Semantic Web Data Management," *Proc. VLDB Endow.*, vol. 1, no. 1,

- pp. 1008–1019, 2008.

[19] M. Atre, V. Chaoji, M. J. Zaki, and J. A. Hendler, "Matrix "Bit" Loaded: A Scalable Lightweight Join Query Processor for RDF Data," in Proc. of the 19th Intl. Conference on World Wide Web, Raleigh, North Carolina, USA, 2010, pp. 41–50. A. Harth, J. Umbrich, A. Hogan, and S. Decker, "YARS2: A Federated

- Repository for Querying Graph Structured Data From the Web," in *Proc. of ISWC'07/ASWC'07*, Busan, Korea, 2007, pp. 211–224.

[21] S. Harris, N. Lamb, and N. Shadbolt, "4store: The Design and Implementation of a Clustered RDF Store," in *Proc. of 5th Intl. Workshop on*

- Scalable Semantic Web Knowledge Base Systems, 2009, pp. 94-109

- [22] A. Owens, A. Seaborne, N. Gibbins, and M. Schraefel, "Clustered TDB: A Clustered Triple Store for Jena," in *Technical Report, Electronics and Computer Science, University of Southampton*, 2008.

[23] J. Weaver and G. T. Williams, "Scalable RDF Query Processing on Clus-

- [22] J. Weaver and G. I. Williams, Scalable RDF Query Flocessing on Clusters and Supercomputers," in *Proc. of the 5th International Workshop on Scalable Semantic Web Knowledge Base Systems*, 2009.

[24] P. Castagna, A. Seaborne, and C. Dollin, "A Parallel Processing Framework for RDF Design and Issues," HP Labs, Bristol, Tech. Rep., 2009, www.hpl.hp.com/techreports/2009/HPL-2009-346.pdf.

[25] P. Svidhor B. Design and W. America, "BASPIC Control of the con

- [25] R. Sridhar, P. Ravindra, and K. Anyanwu, "RAPID: Enabling Scalable Ad-Hoc Analytics on the Semantic Web," in *Proc. of ISWC '09*, 2009, 715-730

- pp. 715–730. [26] M. F. Husain, J. McGlothlin, M. M. Masud, L. R. Khan, and B. Thuraisingham, "Heuristics-Based Query Processing for Large RDF Graphs Using Cloud Computing," *IEEE Transactions on Knowledge and Data Engineering*, vol. 23, pp. 1312–1327, 2011.

- [27] J. Weaver and J. A. Hendler, "Parallel Materialization of the Finite RDFS Closure for Hundreds of Millions of Triples," in *Proc. of ISWC '09*,

- Chantilly, VA, 2009, pp. 682–697.

J. Urbani, S. Kotoulas, E. Oren, and F. Harmelen, "Scalable Distributed Reasoning Using MapReduce," in *Proc. of ISWC '09*, 2009, pp. 634–

- J. Huang, D. J. Abadi, and K. Ren, "Scalable SPARQL Querying of Large RDF Graphs," *PVLDB*, vol. 4, no. 11, pp. 1123–1134, 2011.

- V. Vidal, S. Vernhes, and G. Infantes, "Parallel AI Planning on the SCC," in 4rd Many-core Applications Research Community Symposium (MARC 2011), Potsdam, Germany, 2011, pp. 1–6. [31] P. Petrides, A. Diavastos, and P. Trancoso, "Exploring Database Work-

- loads on Future Clustered Many-Core Architectures," in 3rd Many-core Applications Research Community Symposium (MARC 2011), Ettlingen,

- Germany, 2011, pp. 81–84.

G. Karypis and V. Kumar, "A Fast and High Quality Multilevel Scheme for Partitioning Irregular Graphs," *SIAM Journal on Scientific Computing*, vol. 20, pp. 359–392, December 1998.

I. A. C. Urena, "RCKMPI User Manual," *Intel Braunschweig*, 2011.

- J. Hoffart, F. M. Suchanek, K. Berberich, E. Lewis-Kelham, G. de Melo, and G. Weikum, "YAGO2: Exploring and Querying World Knowledge in Time, Space, Context, and Many Languages," in *Proc. of WWW '11*, 2011, pp. 229–232.

- "Uniprot RDF Distribution," http://www.uniprot.org/downloads.

Y. Guo, Z. Pan, and J. Heflin, "LUBM: A benchmark for OWL knowledge base systems," Web Semantics: Science, Services and Agents

- on the World Wide Web, vol. 3, pp. 158–182, October 2005.

V. Slavov, P. Rao, D. Barenkala, and S. Paturi, "Towards RDF Query Processing on the Intel SCC," University of Missouri-Kansas City, Tech. Rep. TR-DB-2012-01, 2012, http://r.web.umkc.edu/raopr/TR-DB-2012-01. 01.pdf.

# Data Sharing Mechanisms for Parallel Graph Algorithms on the Intel SCC

Randolf Rotta, Thomas Prescher, Jana Traue, Jörg Nolte {rrotta, tpresche, jtraue, jon}@informatik.tu-cottbus.de

Abstract—On many-core processors that do not provide hardware cache coherence, using shared memory in parallel computations is challenging. Reverting to pure message passing would avoid consistency issues, but replicating large shared datasets by messages is less efficient than accessing them directly through shared memory. The TACO-MESH framework provides lightweight remote method calls and shared objects with software-managed consistency. This paper presents experience from porting a graph partitioning algorithm to the framework. A performance evaluation on the experimental Intel SCC processor, which has no hardware cache coherence, shows that parallelization can be efficient despite the overhead of software-level consistency management.

Index Terms—many-core, shared memory, cache coherence, graph partitioning

# I. INTRODUCTION

The number of cores in current many-core architectures is increasing while the performance of most cores decreases in favor of smaller cores [1]. Technically, many-cores are hybrids combining aspects of distributed as well as shared memory systems [2], because internal networks connect the cores to exchange messages between them and connect to memory modules that provide direct access to shared memory.

Many architectures employ data and instruction caches distributed over the network to reduce access latencies and memory traffic by exploiting locality. On cache coherent architectures (e.g. Intel MIC [3], and Tilera [4]), the caches implement a coherence protocol in hardware. However, coherence protocols face significant scaling issues compared to message passing [5], [6], [7], [8]. The SCC processor is an experimental concept vehicle created by Intel Labs as a platform for many-core software research. All of its cores have private caches, but these do, deliberately, not provide hardware-level coherence [9]. Instead, message passing between cores can be used to implement software-level coherence. At the other extreme end are architectures without caches that instead use large shared on-chip memories and a huge number of simpler cores (e.g. IBM Cyclops64 [10], Adapteva [11], and some stream processors in GPUs).

The SCC and other architectures without hardware cache coherence can be treated like distributed systems to work around this limitation. However, passing large messages inside shared memory systems is inefficient, because composing and receiving large messages evicts large portions of the sender's and receiver's caches. Finally, the message data is just copied from and to main memory and will also compete for space in shared caches (e.g. on Intel MIC). Consequently, parallel

programming models and frameworks for many-cores should avoid large unnecessary data copies. Instead, software layers that manage the cache coherence for actual shared data should be integrated into the programming models.

TACO [12] provides a partitioned global address space, remote method invocations, and collective operations; it features a highly efficient messaging backend on the SCC. [13]. On top of that, MESH [14], a framework for memory-efficient sharing, introduces direct access to shared data and a consistency layer for shared objects while using TACO for coordination.

This paper presents experience gained from porting central parts of a complex graph partitioning software for modularity clustering [15] to the SCC. The next section introduces the graph partitioning problem, the local search algorithm, and the employed graph data structures. We combined the graph data structures with the MESH consistency layer and extended MESH with SCC-specific software-level cache coherence, which are described in Section III. Section IV discusses results obtained from micro-benchmarks and the parallelized graph partitioning algorithm. Finally, we discuss related work and provide concluding remarks.

# II. MODULARITY GRAPH PARTITIONING

Graph partitioning can be applied in the analysis of social, biological and technical networks and is, in this context, also known as *graph clustering*. For example, persons in social networks can be modelled by graph vertices, edges connect pairs of related persons, and edge weights quantify how often both persons interacted in the past. Graph clustering is searching groups of highly related vertices and, in our particular application, a partitioning of the vertices with dense connections within groups and sparse connections in between.

The *modularity* by Newman and Girvan [16] is a popular quality measure that directs the search for interesting vertex partitions. It is based on the difference between the fraction of *observed* within-group edges and the *expected* fraction. The expected fraction is based on a stochastic model where the end-vertices of edges are chosen at random, and the probability that an end-vertex of an edge attaches to a particular vertex is proportional to the vertex weight [17]. Compared to other clustering quality measures, the modularity is still easy to calculate. Nevertheless, in contrast to the more traditional quality measures for load-balancing, modularity has data dependencies that disallow some well-known performance optimizations. Thus, the modularity is a good representative for a broader class of graph partitioning problems.

1: find best  $v,D,\Delta Q_{v,D}$  over all  $v\in V$  by collective operation over all workers 2: if  $\Delta Q_{v,D} \leq 0$  then exit loop // move vertex v from partition C to D: 3: if D is empty then create new partition D 4: set current partition of v to D 5: update partition weights w(C) and w(D) 6: increment partition size of D 7: decrement partition size of C 8: if size of C is 0 then delete partition C

Figure 1. A step of the globally greedy vertex moving algorithm.

The next subsection introduces a simple parallel graph partitioning algorithm that will be used for the evaluation of the software-level consistency management. The second subsection describes the data structures used by this algorithm.

# A. Globally Greedy Vertex Moving

The problem of finding a clustering with maximum modularity for a given graph is NP-hard [18], and existing exact algorithms are usable only up to a few hundred vertices. In practice, modularity is almost exclusively optimized with heuristic algorithms, and experimental results indicate that relatively simple algorithms based on local search can be highly efficient and effective (e.g. [15]).

One of the simplest local search algorithms is globally greedy vertex moving as summarized in Figure 1: In each step, the modularity improvement  $\Delta Q_{v,D}$  of moving vertex v to partition D is computed for all pairs of vertices and partitions (line 1) and the globally best move is applied by modifying the partitioning data (lines 3-8). This is repeated until the best move does not increase the modularity (line 2). Faster algorithms exist that are similarly effective but, unfortunately, also more complex. We chose the simplest algorithm to focus on the consistency management of the shared data. Our parallel algorithm uses a set of worker cores to parallelize the computation of  $\Delta Q$  by dividing the vertex set into equally sized subsets. In each step, the workers compute the improvements of their vertices and return v, D, and  $\Delta Q_{v,D}$ of their best move. Then, the master worker selects and applies the best of these moves.

Moving a vertex  $v \in V$  from its current partition  $C \subseteq V$  to another partition  $D \subseteq V$  increases the modularity by

$$\Delta Q_{v,D} = 2 \frac{f(v,D) - f(v,C \setminus v)}{f(V,V)}$$

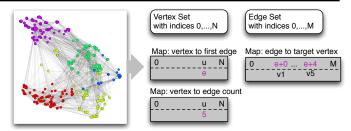

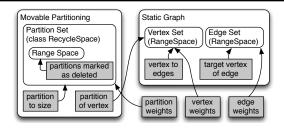

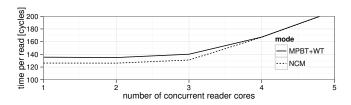

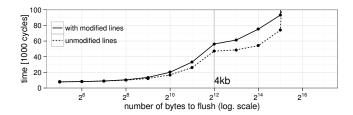

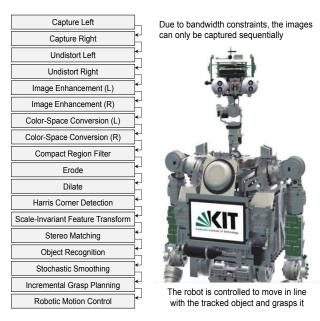

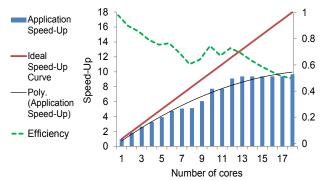

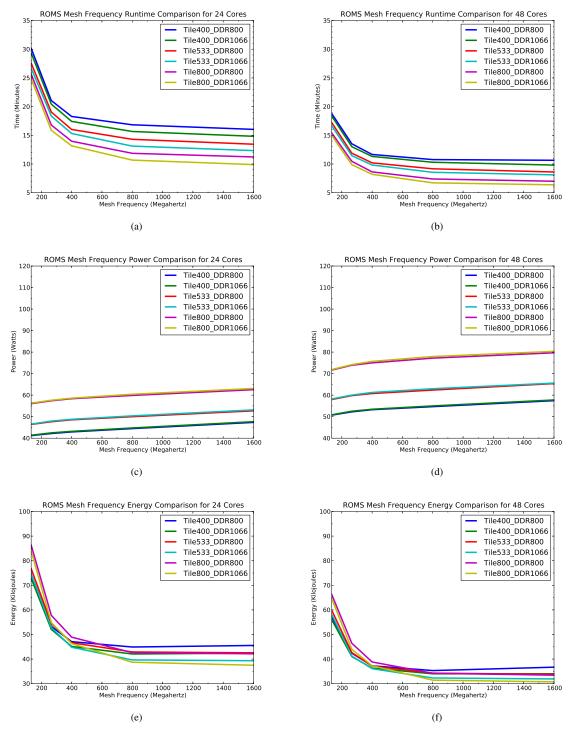

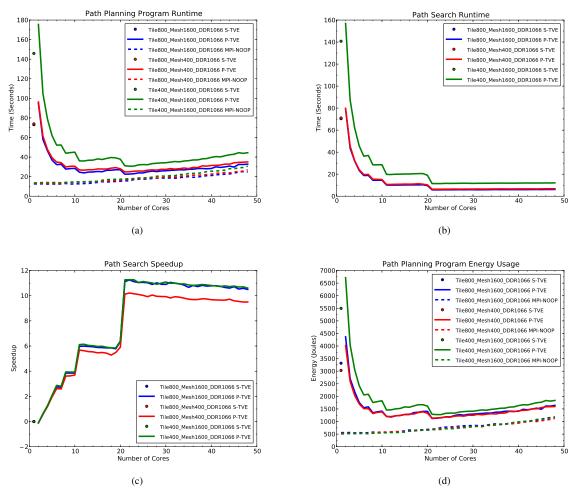

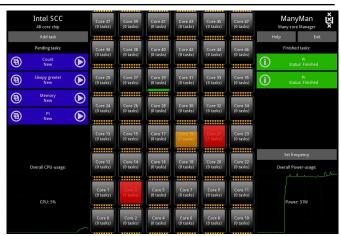

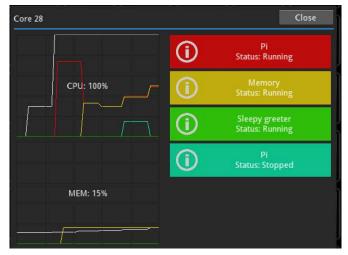

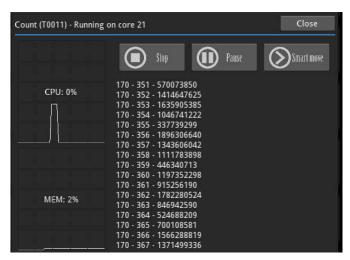

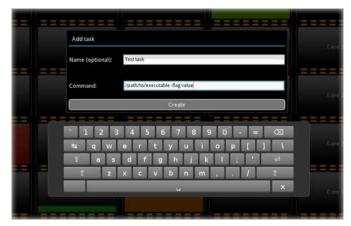

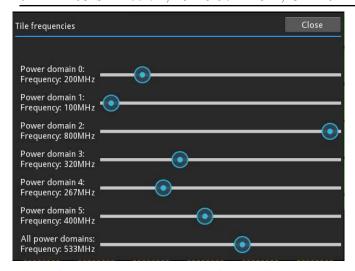

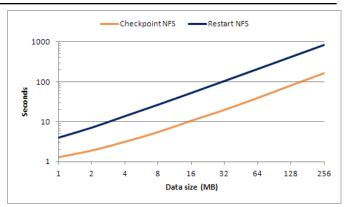

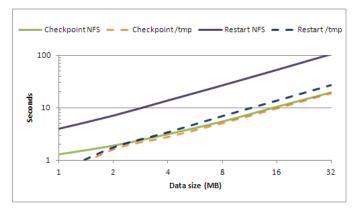

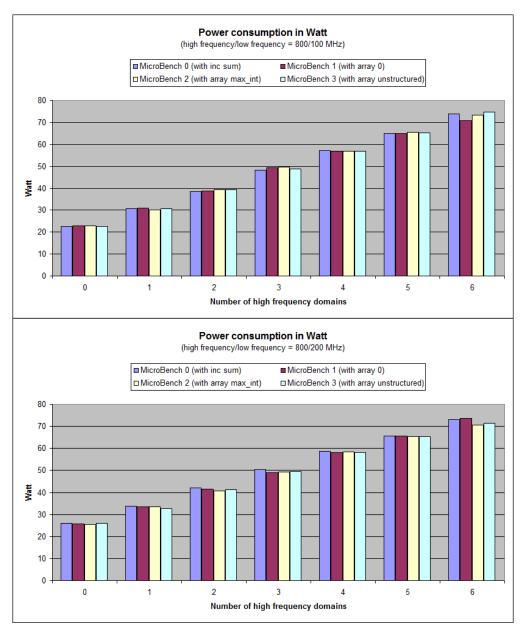

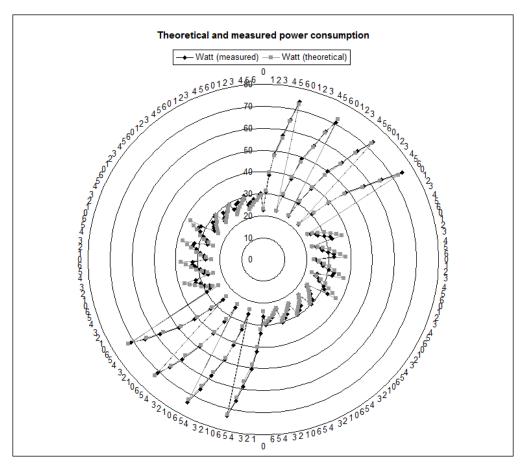

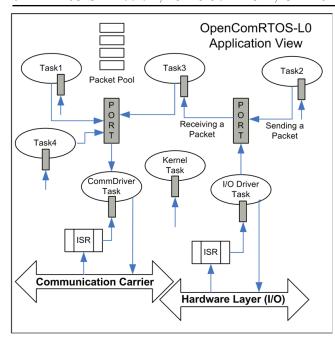

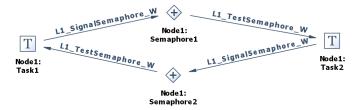

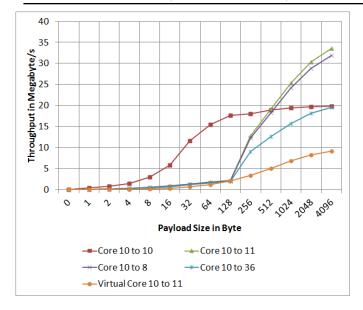

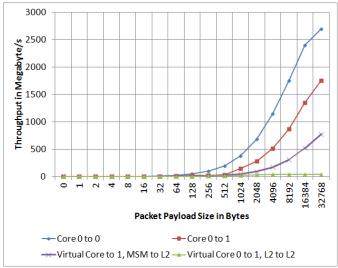

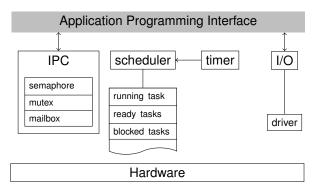

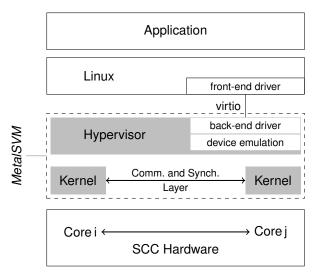

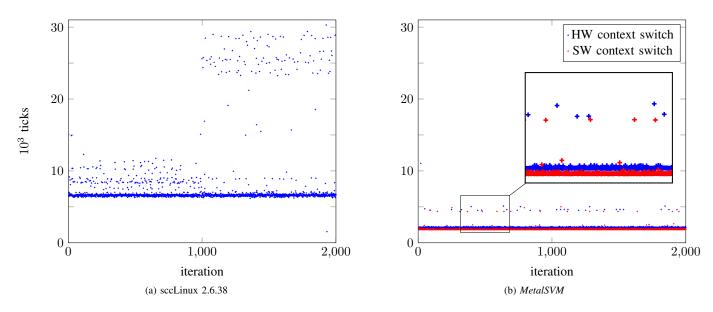

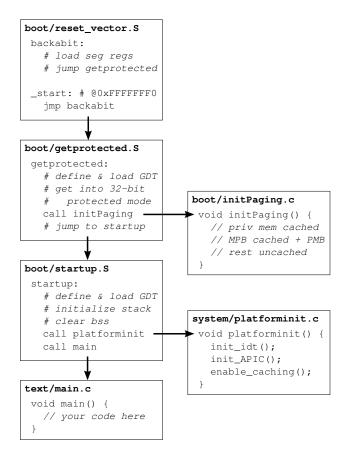

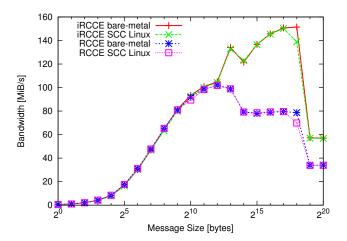

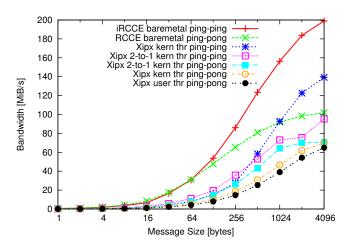

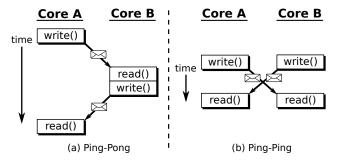

$$- 2 \frac{w(v)w(D) - w(v)w(C \setminus v)}{w(V)^2} ,$$