# Fabrication et caractérisation électrique de résistances à base de nanofils de silicium

Laurent Pichon, Fouad Demami, Régis Rogel, Tayeb Mohammed-Brahim

# ▶ To cite this version:

Laurent Pichon, Fouad Demami, Régis Rogel, Tayeb Mohammed-Brahim. Fabrication et caractérisation électrique de résistances à base de nanofils de silicium. Colloque sur l'Enseignement des Technologies et des Sciences de l'Information et des Systèmes, CETSIS-EEA 2011, 23 - 26 octobre 2011, Trois Rivières (Québec), CANADA., Oct 2011, Trois rivières, Canada. pp.11. hal-00671098

HAL Id: hal-00671098

https://hal.science/hal-00671098

Submitted on 16 Feb 2012

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Fabrication et caractérisation électrique de résistances à base de nanofils de silicium

L. Pichon, F. Demami, R. Rogel, T. Mohammed-Brahim lpichon@univ-rennes1.fr

Pôle CNFM de Rennes

Pôle CNFM de Rennes, Centre Commun de Microélectronique de l'Ouest, campus de beaulieu, bâtiment 11B, 263 avenue du général Leclerc, 35042 Rennes cedex, France

**RESUME**: Cet article présente des travaux pratiques sur la réalisation et la caractérisation électrique de résistances fabriquées à partir de nanofils de silicium polycristallin synthétisés à partir d'outils lithographiques conventionnels de la technologie silicium. Les résistances sont fabriquées en salle blanche puis caractérisées électriquement par mesures I-V.

Mots clés : technologies microélectroniques, salle blanche, nanofils de silicium, résistance, caractérisation électrique.

#### 1 INTRODUCTION

Face au besoin croissant en termes de performances des circuits électroniques, la miniaturisation des composants électroniques, liées au rythme d'intégration indiqué par l'ITRS (International Technology Roadmap for Semiconductors), conduit à d'autres approches architecturales des composants à l'échelle du nanomètre. Aussi, l'élaboration de nano-objets à base de silicium comme éléments de base de ces composants devient incontournable. En d'autres termes cela signifie que l'élaboration des circuits intégrés du futur repose sur des technologies de plus en plus sophistiquées (et donc onéreuses).

La réalisation de nano structures est possible suivant deux approches « Top down » ou « Bottom up ». Dans l'approche « Top down » on cherche à réduire les dimensions d'un objet jusqu'aux limites imposées par les lois de la physique. Cela nécessite l'utilisation d'outils lithographiques très sophistiqués, extrêmement couteux et le plus souvent incompatibles avec une production de masse. L'approche « Bottom up » consiste à assembler des composants élémentaires (atomes, molécules...) afin de former des structures plus complexes. Dans ce cas on réduit considérablement les moyens mis en œuvre, cependant la formation du composant intégrant les nano objets ne se forme que durant la croissance de ce dernier, et est incompatible avec la technologie silicium planaire. Ceci nécessite alors d'imaginer de nouveaux composants compatibles avec ce mode de fabrication.

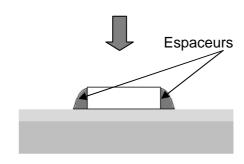

C'est dans ce contexte que nous proposons une formation pratique sous forme de TP qui consiste à fabriquer en salle blanche puis à caractériser électriquement des résistances à partir de nanofils de silicium. Ces nanofils sont synthétisés à partir de la méthode des espaceurs, technique couramment utilisée en technologie silicium submicronique, pour isoler les parties actives des composants [1,2]. Celle-ci est très intéressante car elle permet la réalisation de réseaux de nanofils parallèles à l'aide d'outils lithographiques UV usuellement utilisés en technologie silicium planaire, et donc compatible

avec les procédés de fabrication des circuits dans l'industrie microélectronique.

#### 2 ORGANISATION ET CONTEXTE

Cette proposition de TP est un complément aux formations sur les « Nanotechnologies » dispensées dans les masters ou filières d'écoles d'ingénieurs relevant des nanosciences. Aussi les points forts du programme pédagogique abordé au cours de ce stage pratique concernent les technologies de fabrication (photolithographies UV, gravure plasma,...) et les moyens de caractérisation structurale (microscopie électronique) et électriques associés à la fabrication de dispositifs nanoélectroniques en technologie silicium intégrée.

Lors du TP les étudiants sont répartis en sous groupes de 3 à 4 étudiants pour un encadrant. Le stage, prévu sur 2,5 jours, se déroule dans la salle blanche de la centrale de technologie du Groupe Microélectronique de l'Institut d'Electronique et des Télécommunications de Rennes (GM-IETR-UMR 6164). Une grande partie du TP (2 jours) est consacrée à la fabrication de résistances électriques, puis la dernière partie à la caractérisation électrique.

Les objectifs de cette formation sont multiples : sensibiliser les étudiants au travail en salle blanche, les initier à la manipulation d'un outil de caractérisation structurale et électrique pour l'observation d'objets nanométriques, et les former à la caractérisation électrique des composants.

De plus, le travail demandé s'inscrit pleinement dans le cadre des activités de recherche puisqu'il découle de travaux de thèse menés au GM-IETR sur la synthèse de nanofils de silicium par la méthode des espaceurs [3]. Ceci constitue un plus dans la formation d'étudiants se destinant à la recherche.

### 3 CONTENU DU TP

# 3.1 Formation des espaceurs : principe

Malgré les limites de la lithographie optique classique pour atteindre des échelles nanométriques, il est possi-

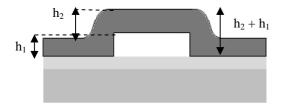

ble de combiner cette dernière avec des procédés technologiques classiques (dépôt CVD, gravure) de la microélectronique pour la réalisation d'objets nanométriques (nanofils). Ainsi, des nanofils de silicium peuvent être fabriqués en utilisant la méthode des espaceurs. Cette dernière consiste à obtenir, par gravure sèche (et anisotrope), un résidu sous forme nanofilaire (espaceur) à partir d'un matériau préalablement déposé (silicium) sur une marche (figure 1). Le résidu (ou espaceur) correspond à la différence d'épaisseur (h<sub>1</sub>+h<sub>2</sub>) du matériau déposé au niveau de la marche. Par ailleurs, notons que par ce procédé le rayon de courbure d'un tel espaceur est quasiment celui donné par l'épaisseur de la marche (h<sub>1</sub>). Ainsi grâce à un contrôle précis de fin de détection de gravure de la couche d'épaisseur h<sub>2</sub> on peut contrôler la formation de l'espa-

# Gravure anisotrope

fig 1 : principe de réalisation d'espaceurs (vue en coupe) : formation d'espaceurs après gravure (anisotrope) de la couche recouvrant la marche

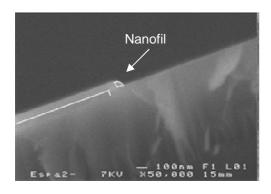

fig 2 : Cliché MEB (vue coupe) d'un espaceur en silicium polycristallin présentant un rayon de courbure de 50nm. D'après [3].

ceur-nanofil ainsi que son rayon de courbure. De tels nanofils ont été fabriqués à partir d'espaceurs constitués d'une couche mince de silicium polycristallin présentant un rayon de courbure de l'ordre de 50nm (fig. 2), et pouvant être utilisés comme élément de canal de TFT (Thin Film Transistor) [3].

La formation des nanofils étant de plus en plus délicate à mesure que le rayon de courbure est faible, le choix de la synthèse de nanofils avec un rayon de courbure de l'ordre de 100nm plutôt que 50nm est privilégié lors du TP.

#### 3.2 Procédé de fabrication de la résistance

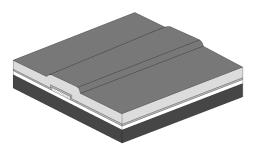

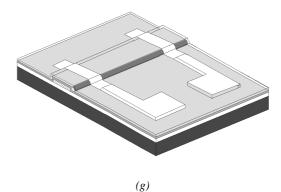

Les résistances à fabriquer sont constituées de 2 nanofils en parallèle reliés à deux contacts métalliques. Ce type de résistance a été conçu par un procédé comprenant 3 niveaux de masquages en lithographie classique UV. La figure 3 illustre les principales étapes technologiques pour réaliser les résistances.

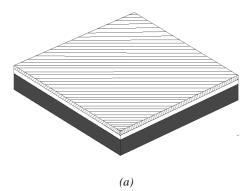

Celles-ci sont fabriquées à partir d'un substrat (verre ou silicium monocristallin) recouvert d'un film mince de nitrure (Si<sub>3</sub>N<sub>4</sub>) de protection préalablement déposé par procédé de décomposition chimique en phase vapeur à basse pression dit LPCVD (Low Pressure Chemical Vapor Deposition).

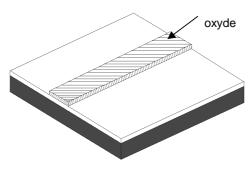

Ensuite, une couche de dioxyde de silicium (SiO<sub>2</sub>) de 100nm d'épaisseur est déposée par voie CVD à pression atmosphérique à 420°C (fig. 3 a). Une première étape de photolithographie suivie d'une gravure par plasma réactif (RIE – Reactive Ion Etching) permettent la formation de marches d'oxyde (fig. 3 b).

Une couche mince de silicium polycristallin dopé *insitu* au phosphore (type N) de 200nm d'épaisseur (fig. 3 c) est ensuite déposée par procédé LPCVD à partir d'un mélange gazeux contenant du silane (SiH<sub>4</sub>) et de la phosphine (PH<sub>3</sub>). Le rapport molaire PH<sub>3</sub>/SiH<sub>4</sub> est fixé de telle manière que le taux dopage soit 10<sup>18</sup> cm<sup>-3</sup>. Le silicium est d'abord déposé en phase amorphe à 550°C à la pression de 90 Pa, puis cristallisé par recuit thermique à 600°C sous vide pendant 12 heures. Pour des raisons à la fois pratiques et de gain de temps cette étape n'est pas réalisée par les étudiants.

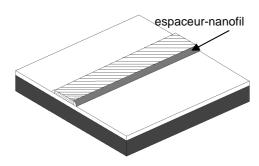

Une gravure de type RIE anisotrope permet ensuite la formation de nanofils-espaceurs, présentant un rayon de courbure d'environ 100nm (fig. 3 d) correspondant à l'épaisseur de la marche d'oxyde.

A ce stade du procédé de fabrication les nanofils subissent un nettoyage comprenant successivement : un bain dans une solution basique (NH<sub>4</sub>OH), un rinçage à l'eau désionisée, un bain dans une solution acide (HCl), un rinçage à l'eau désionisée, un bain dans une solution diluée d'acide fluorhydrique (HF), puis un rinçage à l'eau désionisée. Le rôle de ce nettoyage est de débarrasser la surface des nanofils d'éventuelles impuretés organiques et métalliques susceptibles d'altérer le comportement électrique des résistances.

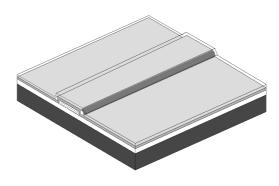

Ces nanofils sont ensuite encapsulés par un deuxième dépôt LPCVD de nitrure de silicium  $Si_3N_4$  à 600°C

Dépôt d'une couche d'oxyde (SiO<sub>2</sub>) de 100nm d'épaisseur sur substrat recouvert de nitrure silicium (Si<sub>3</sub> $N_4$ )

(b)

Photolithographie (masque I): Définition de la marche d'oxyde par gravure RIE (obtention d'un flanc vertical).

(c) Dépôt d'une couche de silicium polycristallin dopé in situ (type N) de 200nm d'épaisseur.

(d) Gravure sèche (RIE) de la couche de Si polycristallin : formation des nanofils (espaceurs)

(e)

Dépôt d'une couche de nitrure de silicium (Si<sub>3</sub>N<sub>4</sub>) d'épaisseur 100nm) : encapsulation des nanofils de silicium

Photolithographie (masque II) : ouvertures à travers le nitrure par gravure sèche RIE ( prise des contacts électriques)

*(f)*

Dépôt d'une couche d'aluminium puis photolithographie (masque III) : définition des contacts électriques.

fig 3 : Principales étapes du procédé de fabrication d'une résistance à base de nanofils de silicium

(épaisseur 100nm), puis des fenêtres d'ouvertures sont réalisées par gravure type RIE (fig. 3 e et f).

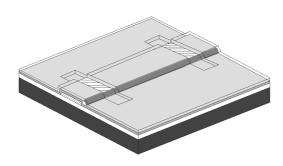

Une couche d'aluminium (épaisseur 400nm) est ensuite déposée par évaporation thermique par effet joule, lithographiée puis gravée par voie humide pour la formation des électrodes de contacts (fig. 3 g). Enfin, la structure finale subit un recuit sous atmosphère hydrogénée (H<sub>2</sub>/N<sub>2</sub>: 0,1) à 390°C afin d'optimiser la qualité électrique des contacts.

# 3.3 Caractérisation électrique

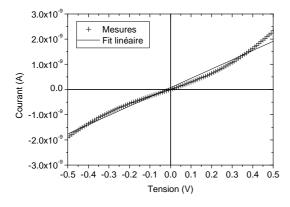

Les résistances ainsi réalisées sont testées électriquement par les étudiants grâce à des mesures I-V. Le dispositif de mesures à disposition est un analyseur de paramètres programmable HP 41556 A. La figure 4 représente la courbe I(V) de ce type de résistances constituées de 2 nanofils en parallèle. La caractéristique linéaire de la courbe I(V) traduit le comportement ohmique et donc résistif du dispositif ainsi fabriqué. Une estimation de la résistance électrique globale est alors extraite de la pente de la courbe I(V) au voisinage de l'origine. La valeur de la mesure donne  $R=250M\Omega$ .

Connaissant la section d'un nanofil (définie comme étant celle d'un quart de disque) une estimation de la résistivité,  $\rho$ , de chaque nanofil est alors possible à partir de la relation :

$$\rho = \frac{\pi r^2}{2L}R$$

où L et r représentent respectivement la longueur et le rayon de courbure des 2 nanofils en parallèle. La valeur obtenue est ~ $40\Omega$ cm, et est conforme à la résistivité d'une couche de silicium polycristallin dopé et déposé dans les conditions opératoires précisées précédemment [4]. Notons que cette valeur est beaucoup plus élevée que celle du silicium monocristallin (environ  $10^3$  fois) pour un niveau de dopage identique. Ceci est lié au caractère polycristallin de la couche de silicium à partir

fig 4 : Caractéristique I(V) de la résistance à base de nanofils de silicium

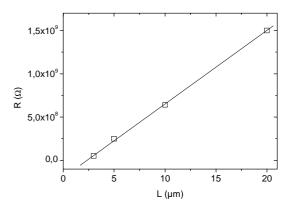

fig 5 : variation de la résistance électrique en fonction de la longueur des nanofils de silicium

de laquelle sont réalisés les nanofils. En effet, dans ce cas la structure cristalline est très perturbée avec une densité de défauts (joints de grains et défauts intragrains) très élevée. Ceux-ci sont responsables du piégeage des porteurs de charges [5], et donc altèrent de manière significative les propriétés de conduction électrique du silicium.

Ensuite, des mesures sont effectuées sur des résistances fabriquées à partir de nanofils de longueurs différentes. Le tracé de la courbe (fig. 5) obtenu montre la variation de la résistance électrique globale en fonction de la longueur des nanofils. La dépendance linéaire permet alors de valider le procédé de fabrication.

# 4 CONCLUSION

Cette formation est en adéquation avec les activités de recherche relevant du domaine des nanosciences et plus particulièrement en nanotechnologies silicium. Elle sensibilise les étudiants à la complexité des moyens mis en œuvre dans la réalisation d'objets et le développement de dispositifs électroniques nanométriques. De plus, elle permet aux étudiants de découvrir l'environnement d'une salle blanche et de les initier à l'utilisation de certaines technologies de fabrication (aligneur UV, gravure plasma...) et de moyens de caractérisations électriques nécessaires dans un processus de fabrication de dispositifs électroniques.

La spécificité rennaise de ce TP est de travailler avec des matériaux en couches minces à base de silicium synthétisés au GM-IETR, en rapport avec des thématiques de recherche actuelles.

Le contenu de cette formation est en pleine adéquation avec les évolutions actuelles de la microélectronique vers la nanoélectronique. Une telle formation est une bonne approche pour sensibiliser les étudiants aux défis technologiques majeurs auxquels doivent faire face à l'heure actuelle les technologues pour le développement de l'électronique intégrée de la prochaine décennie.

Notons que ce type de formation technologique couvre un large champ disciplinaire (chimie, matériaux, physique, micro- et nano-électronique) et qu'elle peut convenir à un public d'étudiants issus des filières correspondantes en rapport avec les nanotechnologies. Aussi ce TP peut être proposé aux étudiants de 2<sup>e</sup> année de Master ou de formations équivalentes dépendant des universités ou des écoles d'ingénieurs. Cette offre de formation vient étoffer la palette des formations proposées, dans le cadre de la formation initiale ou continue, aux établissements d'enseignement supérieur du grand ouest (Caen, Rennes, Brest, Nantes...) par le pôle rennais de la Coordination Nationale pour la Formation en Micro et nanotechnologies (CNFM).

## **Bibliographie**

- [1] D. Hyuk Ju, "CMOS processing employing removable sidewall spacers for independently optimized N- and P6 channel transistor performance, Adavnced Micro Devices, Appl N0 927, p 637 (1997)

- [2] H.-C. Lin, M.-H. Lee, C.-J. Su, T.-Y. Huang, C. C. Lee, and Y.-S. Yang, "A Simple and Low-Cost Method to Fabricate TFTs With Poly-Si Nanowire Channel" *IEEE Electron Device Letters*, vol. 26, No. 9, pp 643-645 (2005).

- [3] F. Demami, « Synthèse de nanofils de silicium par la méthode des espaceurs pour dispositifs électroniques », Thèse de doctorat de l'université de Rennes 1, Mars 2011

- [4] D. Briand, M. Sarret, F. Le-Bihan, O. Bonnaud, L. Pichon, «Polysilicon in-situ phosphorus doping control over large concentration range using low temperature, low chemical vapor deposition growth process, Materials Science and Technology, 11 pp 1207-1209 (1995)

- [5] J. W. Seto, "The electrical properties of the silicon films" Journal of Applied Physics, 46(12), pp 5247-5254 (1975)