# Experimental verification of the usefulness of the nth power law MOSFET model under hot carrier wearout

Nestor Berbel, Raul Fernandez-Garcia, Ignacio Gil, Binhong Li, Alexandre Boyer, Sonia Ben Dhia

# ▶ To cite this version:

Nestor Berbel, Raul Fernandez-Garcia, Ignacio Gil, Binhong Li, Alexandre Boyer, et al.. Experimental verification of the usefulness of the nth power law MOSFET model under hot carrier wearout. Microelectronics Reliability, 2011, 51 (9), pp.1564. hal-00669511

HAL Id: hal-00669511

https://hal.science/hal-00669511

Submitted on 13 Feb 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Experimental verification of the usefulness of the *n*th power law MOSFET model under hot carrier wearout

N. Berbel<sup>a</sup>, R. Fernández-García<sup>a</sup>, I. Gil<sup>a</sup>, B. Li<sup>b</sup>, A. Boyer<sup>b</sup>, S. BenDhia<sup>b</sup>

#### **Abstract**

In this paper the usefulness of the *n*th power law MOSFET model under Hot Carrier Injection (HCI) wearout has been experimentally demonstrated. In order to do that, three types of nFET transistors have been analyzed under different HCI conditions and the *n*th power law MOSFET model has been extracted for each sample. The results show that the model can reproduce the MOSFET behavior under HCI wearout mechanism. Therefore, the impact of HCI on circuits can be analyzed by using the *n*th power law MOSFET model.

## 1. Introduction

The *n*th power law MOSFET model, also namely Sakurai–Newton model, is a well-known analytical model, which can reproduce the MOSFET behavior with only six parameters [1]. The model is expressed in the following equation:

$$V_{\text{DSAT}} = K \cdot (V_{\text{GS}} - V_{\text{TH}})^{m}$$

$$I_{\text{DSAT}} = B \cdot (V_{\text{GS}} - V_{\text{TH}})^{n}$$

$$V_{\text{GS}} < V_{\text{TH}} \qquad I_{\text{D}} = 0 \text{ A}$$

$$V_{\text{GS}} \geqslant V_{\text{TH}} \begin{cases} V_{\text{DS}} < V_{\text{DSAT}} & I_{\text{D}} = I_{\text{DSAT}} \cdot (1 + \lambda_{\text{e}} \cdot V_{\text{DS}}) \cdot \left(2 - \frac{V_{\text{DS}}}{V_{\text{DSAT}}}\right) \cdot \frac{V_{\text{DS}}}{V_{\text{DSAT}}} \\ V_{\text{DS}} \geqslant V_{\text{BSAT}} & I_{\text{D}} = I_{\text{DSAT}} \cdot (1 + \lambda_{\text{e}} \cdot V_{\text{DS}}) \end{cases}$$

$$(1)$$

where  $V_{\rm GS}$  and  $V_{\rm DS}$  are the gate-to-source and the drain-to-source voltages, respectively.  $V_{\rm TH}$  denotes the threshold voltage,  $V_{\rm DSAT}$  the drain saturation voltage and  $I_{\rm DSAT}$  the drain saturation current. Parameters K and m control the linear region characteristics whereas B and n determine the saturated region characteristics.  $\lambda$  is related to the finite drain conductance in the saturated region. The simplicity of the model allows an analytical processing. The model (or models derived from it) has been extensively used in order to evaluate the behavior of several CMOS circuits [1], [2], [3] and [4] due to its simplicity. It should be pointed out that the nth power law MOSFET parameters correspond to an analytical non-physical model and it is only valid for voltage gates above the voltage threshold.

<sup>&</sup>lt;sup>a</sup> Electronic Engineering Department, UPC Barcelona Tech., Colom 1, 08222 Terrassa, Spain

<sup>&</sup>lt;sup>b</sup> Départment du Genie Electrique et Informatique, INSA de Toulouse, Avenue de Rangueil 135, 31077 Toulouse, France

Hot Carriers Injection (HCI) is the phenomenon in solid-state or semiconductor electronic devices where either an electron or a "hole" gains sufficient kinetic energy to overcome a potential barrier necessary to break an interface state [5]. HCl does not always lead to circuit failure [6], but provokes undesired effects such as the reduction of the speed at which the transistor can operate. Therefore, to determine how sensitive are the electronic circuits to HCI, some accurate models are required. In this sense, MOSFET models, which take into account the effects of HCI, and that could be implemented in circuit simulators are required. Equivalent electrical circuits for FETs under HCl have been already presented, which can be included in SPICE simulators. In this approach, additional components are needed [7]. An alternative approach is the description of the HCI MOSFET using models like, for example, BSIM, whose parameters are extracted after the HCI stress. This approach would be the most accurate, but a large number of parameters and a complex extraction process are required. In this work, and alternative approach has been followed, and the usefulness of nth power law MOSFET model under HCI effect has been demonstrated experimentally. Moreover, the impact of HCI wearout on each Sakurai-Newton model parameters has been experimentally obtained.

# 2. Experimental

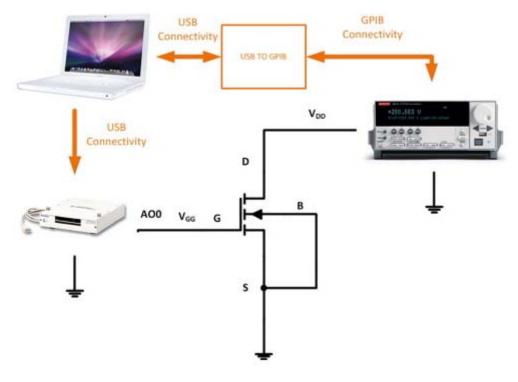

To analyze the impact of the HCI in the nMOS, a Keithley 2602A Source-meter, a digital multimeter and an acquisition board have been used, all of them controlled with a laptop (Fig. 1). First of all, it is necessary to obtain the stress conditions. The  $V_{\rm DS}$  stress voltage ( $V_{\rm STRESS}$ ) should be equal to the drain-to-source voltage breakdown minus 0.5 V. The  $V_{\rm GS}$  stress voltage is obtained by measuring the substrate current ( $I_{\rm SUB}$ ) whereas the  $V_{\rm GS}$  is swept with the  $V_{\rm DS}$  set to  $V_{\rm STRESS}$ . The  $V_{\rm GS}$  stress voltage is defined as the gate voltage corresponding to the maximum  $I_{\rm SUB}$  value on the  $I_{\rm SUB}$ – $V_{\rm GS}$  curve. Table 1 summarizes the different stress voltages applied to the different type of nMOS transistors.

Fig. 1. Set-up to obtain the impact of the HCI on nMOS.

Table 1. Type of transistor measured and stress voltages applied.

|                                                      | V <sub>DS</sub>   <sub>STRESS</sub> (V) | V <sub>GS</sub>   <sub>STRESS</sub> (V) |

|------------------------------------------------------|-----------------------------------------|-----------------------------------------|

| High voltage long ( $W = 10 \mu m L = 1.52 \mu m$ )  | 7                                       | 2.6                                     |

|                                                      | 5                                       | 1.9                                     |

| High voltage short ( $W = 10 \mu m L = 0.38 \mu m$ ) | 7                                       | 2.05                                    |

|                                                      | 5                                       | 1.6                                     |

| Low voltage long ( $W = 10 \mu m L = 0.4 \mu m$ )    | 3                                       | 0.97                                    |

|                                                      | 2.5                                     | 0.9                                     |

## 3. Results

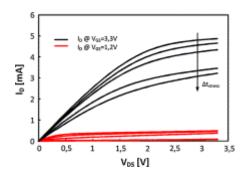

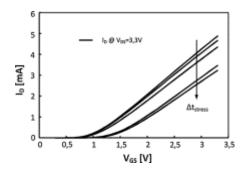

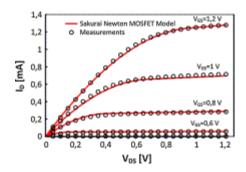

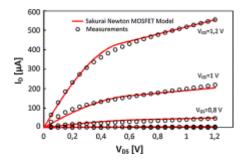

Fig. 2 and Fig. 3 show the ID–VDS and the ID–VGS curve characteristic, respectively, for several stress time. As it is observed, the drain saturation current is reduced due to the effect of the HCI. Fig. 4 and Fig. 5 plot the fitting of the measurements and the Sakurai–Newton MOSFET model for the fresh component and after 700 s of stress. A good correlation between the mathematical model and the measurements has been obtained. Therefore, the impact of HCI wearout on each *n*th power law MOSFET model has been evaluated and it is shown below.

Fig. 2.  $I_D$ – $V_{DS}$  for several stress time and several  $V_{GS}$ .

Fig. 3.  $I_D$ – $V_{GS}$  for several stress time.

Fig. 4. Comparison between the measurements and the Sakurai-Newton MOSFET model for the fresh component.

Fig. 5. Comparison between the measurements and the Sakurai–Newton MOSFET model for the  $t_{\text{STRESS}}$  = 700 s.

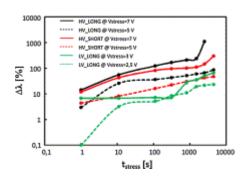

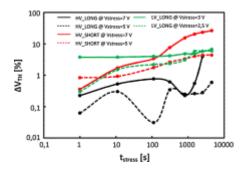

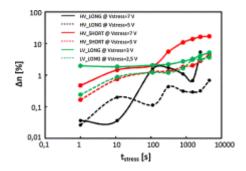

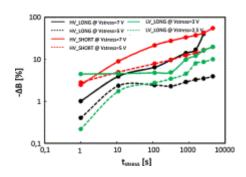

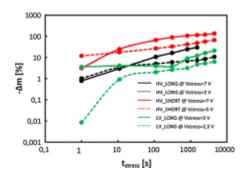

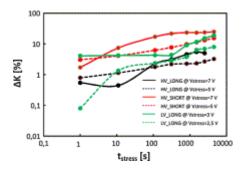

Fig. 6 depicts the increase of the finite drain conductance ( $\lambda$ ), which produces a change in the slope of the drain current (in the saturated region), as can be observed in Fig. 2. Fig. 7 plots the threshold voltage shift, which is more significant on the high voltage short transistor, rather than on the high voltage long and low voltage long. The VTH enhancement provokes a drain current decrease, as can be observed on Fig. 3. The n parameters shift is plotted in Fig. 8, which corresponds to a value less than 10% for the three types of nMOS transistors. On the other hand, B parameter shift is plotted in Fig. 9, which decreases as long as the stress time increases. This parameter is related with the transconductance of the device. Fig. 10 and Fig. 11 show the K and m parameters shift, related with control of the linear region. Both parameters are modified due to the change of the linear ID–VDS curve characteristic, as seen in Fig. 4 and Fig. 5.

Fig. 6. Variation of the finite drain conductance ( $\lambda$ ) versus the stress time.

Fig. 7. Variation of the threshold voltage versus the stress time.

Fig. 8. Variation of the *n* parameter versus the stress time.

Fig. 9. Variation of the transconductance (*B*) versus the stress time.

Fig. 10. Variation of the m parameter versus the stress time.

Fig. 11. Variation of the *K* parameter versus the stress time.

#### 4. Conclusions

In this paper, the usefulness of the Sakurai–Newton MOSFET model under HCl wearout has been experimentally demonstrated for different nFET transistors and different stress conditions. The impact of HCl on each parameter has been also analyzed. The results show that the models can be useful in order to fit the MOSFET behavior under HCl stress and it can be included in a circuit simulator to predict the impact of HCl on digital circuit behavior, where the sub-threshold behaviors are not so important.

# Acknowledgements

This work has been supported by the Spain-MICINN under Projects TEC2010-18550 and AGAUR 2009 SGR 1425. The authors want to thank to B. Vrignon from Freescale Semiconductors for sample provision.

#### References

- [1] T. Sakurai and A.R. Newton, A simple MOSFET model for circuit analysis. IEEE Trans Electr Dev, 38 April (1991), pp. 887–894

- [2] J.L. Rossello and J. Segura, An analytical charge-based compact delay model for submicrometer CMOS inverters. IEEE Trans Circuits Syst I: Regular Papers, 51 7 (2004), pp. 1301–1311

- [3] R. Fernandez, R. Rodriguez, M. Nafria and X. Aymerich, DC broken down MOSFET model for circuit reliability simulation. Electr Lett, 41 6 (2005), pp. 368–370

- [4] Chandra Nishant, Yati Apoorva Kumar, Bhattacharyya AB. Extended-Sakurai–Newton MOSFET Model for Ultra-Deep-Submicrometer CMOS Digital Design, vlsid. In: 2009 22nd international conference on VLSI design; 2009. p. 247–52...

- [5] A. Acovic, G. La Rosa and Y. Sun, A review of hot-carrier degradation mechanisms in MOSFETs. Microelectr Reliab, 36 8 (1996), pp. 845–869.

- [6] Xiaojun Li, Jin Qin, Bing Huang, Xiaohu Zhang and J.B. Bernstein, SRAM circuit-failure modeling and reliability simulation with SPICE. IEEE Trans Device Mater Reliab, 6 2 (2006), pp. 235–246.

- [7] Xiaojun Li, Jin Qin and J.B. Bernstein, Compact modeling of MOSFET wearout mechanisms for circuit-reliability simulation. IEEE Trans Device Mater Reliab, 8 1 (2008), pp. 98–121