## Stability oriented SRAM performance optimization in subthreshold operation

Adam Makosiej, Olivier Thomas, Andrei Vladimirescu, Amara Amara

## ▶ To cite this version:

Adam Makosiej, Olivier Thomas, Andrei Vladimirescu, Amara Amara. Stability oriented SRAM performance optimization in subthreshold operation. 2011 Subthreshold Microelectronics Conference, Sep 2011, Lexington, Massachussets, United States. pp.32. hal-00643918

HAL Id: hal-00643918

https://hal.science/hal-00643918

Submitted on 24 Nov 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Stability oriented SRAM performance optimization in subthreshold operation

Adam Makosiej<sup>1</sup>, Olivier Thomas<sup>3</sup>, Andrei Vladimirescu<sup>1,2</sup>, and Amara Amara<sup>1</sup>

<sup>1</sup>Institut Supérieur d'Electronique de Paris, France

<sup>2</sup> Berkeley Wireless Research Center, UC Berkeley

<sup>3</sup> CEA, LETI, MINATEC, F-38054, Grenoble

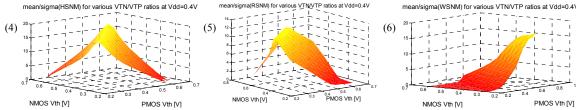

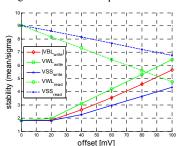

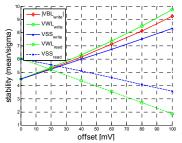

In this work we are analyzing the 6T SRAM cell operation in subthreshold using the 32nm UTBB-FDSOI [1] technology. As a first step an analytical model is developed allowing an accurate estimation of Static Noise Margin (SNM) [2] in all operation modes. The basic equations for retention and read were presented in [3]. Here, we include the DIBL, body factor and all cell voltages as parameters and demonstrate the equation for write SNM. Figs. 1-3, show an excellent correlation with SPICE simulation results, especially as compared to the simplified model as in [3]. Thus, it becomes possible to perform a complete static analysis of SRAM stability based only on a few technology parameters (DIBL, subthreshold slope, threshold voltages, body factor), which are easily extractible either from the model or silicon measurements. The optimum tradeoffs between cell transistors V<sub>T</sub>s for best stability in subthreshold for read and retention are presented in Fig.4,5 and are consistent with [4]. Fig.6 extends the analysis to write SNM. Due to the high steepness of write stability plot, ensuring proper operation in this mode becomes the main limitation for aggressive V<sub>DD</sub> scaling (Fig.6). It should be mentioned however, that as the analysis is based on subthreshold equations, the write stability in Fig.6 for V<sub>TN</sub><0.4V is underestimated. Fig.7 depicts the influence of typical write assist techniques (under driving the bitline, modifying wordline voltage and increasing  $V_{SS}$ ) on the read and write stability (for  $A_{VT}=1.1 \text{mV} \mu \text{m}$ ) for  $V_{TS}$  optimized for top retention stability ( $V_{TN}$ =451mV,  $V_{TP}$ =412mV). It can be noted, that setting  $V_{BL}$ =-0.1V (write bitline voltage) gives the write  $\mu/\sigma=5.66$ , while maintaining read  $\mu/\sigma>9$ . As presented in Fig.7, the balance between these values can be further adjusted by increasing either V<sub>SS</sub> or V<sub>WL</sub>.Fig.8 depicts results of the same analysis for another  $V_T$  set, for which the read  $\mu/\sigma=6$  ( $V_{TN}=451 \text{mV}$ ,  $V_{TP}=528 \text{mV}$ ).

$$V_{1} = -\frac{S_{D1}}{\ln 10} \left( \ln \frac{I_{D1}}{I_{A1}} + \ln \left( \frac{1 - \exp\left(\frac{V_{SS} - V_{2}}{V_{th}}\right)}{1 - \exp\left(\frac{V_{2} - V_{BL}}{V_{th}}\right)} \right) - V_{2} \frac{S_{D1} + S_{A1} \eta_{D1} + S_{D1} \eta_{A1} + \gamma_{A1} \eta_{D1}}{S_{A1}} + V_{WL} \frac{S_{D1}}{S_{A1}} + V_{BL} \frac{S_{D1}}{S_{A1}} \eta_{A1} + V_{SS} (1 + \eta_{D1} + \gamma_{D1}) + Eq. 1 \text{ Read mode equation (D,A,L- Driver, Acces and Load transistors respectively; indexes 1 and 2 correspond to left and right half cells;  $\eta$ - DIBL;  $\gamma$ - body factor; I-transistor current for  $V_{CS} = V_{T}$  indexes 1 and 2 correspond to left and right half cells;  $\eta$ - DIBL;  $\gamma$ - body factor; I-transistor current for  $V_{CS} = V_{T}$  indexes 1 and 2 correspond to left and right half cells;  $\gamma$ - DIBL;  $\gamma$ - body factor; I-transistor current for  $V_{CS} = V_{T}$  indexes 1 and 2 correspond to left and right half cells;  $\gamma$ - DIBL;  $\gamma$ - body factor; I-transistor current for  $V_{CS} = V_{T}$  indexes 1 and 2 correspond to left and right half cells;  $\gamma$ - DIBL;  $\gamma$ - body factor; I-transistor current for  $V_{CS} = V_{T}$  indexes 1 and 2 correspond to left and right half cells;  $\gamma$ - DIBL;  $\gamma$ - body factor; I-transistor current for  $V_{CS} = V_{T}$  indexes 1 and 2 correspond to left and right half cells;  $\gamma$ - DIBL;  $\gamma$ - body factor; I-transistor current for  $V_{CS} = V_{T}$  indexes 1 and 2 correspond to left and right half cells;  $\gamma$ - DIBL;  $\gamma$ - body factor; I-transistor current for  $V_{CS} = V_{T}$  indexes 1 and 2 correspond to left and right half cells;  $\gamma$ - DIBL;  $\gamma$ - body factor; I-transistor current for  $V_{CS} = V_{T}$  indexes 1 and 2 correspond to left and right half cells;  $\gamma$ - body factor; I-transistor current for  $V_{CS} = V_{T}$  indexes 1 and 2 correspond to left and right half cells;  $\gamma$ - body factor; I-transistor current for  $V_{CS} = V_{T}$  indexes 1 and 2 correspond to left and right half cells;  $\gamma$ - body factor; I-transistor current for  $V_{CS} = V_{T}$  indexes 1 and 2 correspond to left and right half cells;  $\gamma$ - body factor; I-transistor current for  $V_{CS} = V_{T}$  indexes 1 and 2 correspond to left and$$

Figs. 1-3 Comparison of equation (dashed), simple equation (dotted) and SPICE (solid) butterfly curves for retention, read and write at  $V_{DD}$ =0.4

Figs.4-6 Evaluation of  $\mu/\sigma$  for retention, read and write in function of  $V_{TN}/V_{TP}$  ratio at  $V_{DD}$ =0.4V

Fig.7 Assessment of write assist techniques on read and write  $\mu/\sigma$  (from ELDO simulations) for  $V_T s$  adjusted for top retention stability

Fig.8 Assessment of write assist techniques on read and write  $\mu/\sigma$  (from ELDO simulations) for  $V_Ts$  adjusted for initial read  $\mu/\sigma=6$

## REFERENCES:

- J-P. Noel, et al., "UT2B-FDSOI Device Architecture Dedicated to Low Power Design Techniques," ESSDERC 2010

- "Static-Noise Margin Analysis of MOS SRAM Cells" E. Seevinck et al., JSSC 1987

- "Static noise margin variation for subthreshold SRAM in 65-nm CMOS", Calhoun, B.H.; Chandrakasan, A.P, JSSC 2006

- "An SNM Estimation and Optimization Model for ULP sub-45nm CMOS SRAM in the Presence of Variability", A. Makosiej, et al., NEWCAS 2010