# Contact etch stop a-SixNy:H layer: A key factor for single polysilicon flash memory data retention

G. Beylier, D. Benoit, P. Mora, S. Bruyère, G. Ghibaudo

#### ▶ To cite this version:

G. Beylier, D. Benoit, P. Mora, S. Bruyère, G. Ghibaudo. Contact etch stop a-SixNy:H layer: A key factor for single polysilicon flash memory data retention. Journal of Vacuum Science and Technology, 2009, 27 (1), pp.486-489. 10.1116/1.3071846 . hal-00596103

### HAL Id: hal-00596103

https://hal.science/hal-00596103

Submitted on 2 May 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Contact etch stop a-Si<sub>x</sub>N<sub>y</sub>:H layer: A key factor for single polysilicon flash memory data retention

G. Bevlier<sup>a)</sup>

STMicroelectronics, F-38920 Crolles, France and IMEP, Minatec, 38016 Grenoble, France

D. Benoit, P. Mora, and S. Bruyère STMicroelectronics, F-38920 Crolles, France

G. Ghibaudo

IMEP, Minatec, 38016 Grenoble, France

(Received 30 May 2008; accepted 15 December 2008; published 9 February 2009)

The silicon nitride (a-Si<sub>r</sub>N<sub>v</sub>:H) contact etch stop layer strongly affects data retention performances in single polysilicon nonvolatile memories by acting on the initial charge loss phenomenon. Its improvement has required an analysis of influent plasma enhanced chemical vapor deposition process parameters through a design of experiment approach. The a-Si<sub>x</sub>N<sub>y</sub>:H physico-electrical analysis points out that silicon rich compositions especially of its interfacial layer must be avoided to reduce a-Si, N<sub>y</sub>: H charge amount and as a result to improve the data retention. Indeed, the a-Si<sub>v</sub>N<sub>v</sub>:H being near the floating gate, its charges modulation could act as a parasitic memory screening charges stored in the floating gate by capacitive effects. © 2009 American Vacuum Society. [DOI: 10.1116/1.3071846]

#### I. INTRODUCTION

Data retention (DR) is one of the main reliability concerns affecting nonvolatile memory (NVM). It must be guaranteed over ten years at quite high temperature (85 °C). However, when considering low cost (no added process step) single polysilicon (SP) flash cells, this requirement become even more critical. Indeed, the floating gate (FG) being no longer encapsulated by the control gate, its sensitivity to various process steps increases, increasing charge loss mechanisms. Recently, two charge loss phases have been distinguished for such a cell during accelerated 250 °C DR bake. During the first seconds of the experiment, a fast initial threshold voltage  $(V_{th})$  shift appears and is followed by the standard long term charge loss from the FG.<sup>2,3</sup> A Mielke cycle analysis has demonstrated that this abnormal initial shift is not induced by the traditional ionic contamination.<sup>3</sup> In this context, after having observed a data loss reduction by taking away the amorphous silicon nitride (a-Si<sub>x</sub>N<sub>y</sub>:H) contact etch stop layer (CESL) from the FG,<sup>3</sup> we have suspected this layer. The CESL, integrating in the premetal dielectric (PMD) stack, is deposited by plasma enhanced chemical vapor deposition<sup>4</sup> (PECVD) and previous electrical characterizations have highlighted a high defect amount in this dielectric.<sup>5</sup> Thus, the most probable hypothesis is that charges contained in the a-Si<sub>x</sub>N<sub>y</sub>:H induced capacitive effects on the FG one.<sup>3,5</sup> In this context, the aim of this study is to understand how physico-electrical a-Si<sub>x</sub>N<sub>y</sub>:H properties impact the SP NVM DR by a design of experiment (DOE) on PECVD process conditions.

486

#### II. DOE CONSTRUCTION AND RESULTS

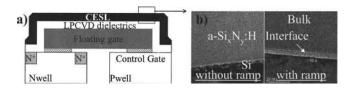

The analysis is performed on a 0.13  $\mu$ m complementary metal oxide semiconductor technology SP NVM with a 85 Å gate oxide.<sup>3</sup> The cell under consideration is defined by two areas: one corresponds to the control gate, with a high coupling coefficient to modulate the FG potential, and another used to program, erase, or select the bit [Fig. 1(a)]. Programing sequence is a two step operation, using a bipolar and an NMOS transistor, respectively, used to generate hot electron and to inject them into the FG. The cell is erasing by Fowler-Nordheim conduction. The 500 Å a-Si<sub>x</sub>N<sub>y</sub>:H CESL is deposited by PECVD process and separated from the FG by LPCVD dielectrics used for silicide protection. Due to process deposition condition, the a-Si<sub>x</sub>N<sub>y</sub>: H layer composition is not uniform and consists of an "interfacial" layer at the bottom, whose composition differs from the "bulk" [Fig. 1(b)]. Taking this into account, film deposition conditions were varied in accordance with a DOE plan, composed of four factors of three levels each and defined by a D optimal matrix (23 recipes with three centers points). Thus, the CESL "bulk" composition is defined by a first set of parameters: the silane (SiH<sub>4</sub>) flow, the ammoniac (NH<sub>3</sub>) one, and the radio frequency (rf) power. They were selected from a preliminary study, performed on a metal insulation semiconductor structure, where an increase of defect with silicon rich (Si-rich) film has been observed.<sup>6</sup> The last parameter is the rf power ramp up speed, since it modifies the bottom "interface." Indeed, as the SiH<sub>4</sub> is more easily dissociated than the NH<sub>3</sub>, the low power at the beginning of the power ramp up gives a more Si-rich interfacial layer, suspected to act as a charge sink.

The DOE responses focus on physico-electrical properties involving numerous analysis tools, as described in the Table I. Some of them were determined as well as for the bulk than

486

No corrections received from author prior to publication.

a)Electronic mail: gaelle\_beylier@st.com

Table I. DOE responses with method and variation range (b and i indices were for bulk and interface, respectively).

| DOE response                             | S               | Methods                                 | Minimum               | Maximum               |

|------------------------------------------|-----------------|-----------------------------------------|-----------------------|-----------------------|

| $Si-H_b$ (cm <sup>-3</sup> )             |                 | Fourier transform infrared spectroscopy | $3.34 \times 10^{20}$ | $1.05 \times 10^{22}$ |

| $N-H_b$ (cm <sup>-3</sup> )              |                 | Fourier transform infrared spectroscopy | $4.9 \times 10^{20}$  | $2.2 \times 10^{22}$  |

| $Stress_b$ (MPa)                         |                 | Wafer curvature                         | -1013                 | 783                   |

| Density (g cm <sup>-3</sup> )            |                 | Weighing                                | 2.28                  | 2.66                  |

| Refractive index                         | $RI_b$          | Spectroscopic ellipsometry (630 nm)     | 1.88                  | 2.36                  |

|                                          | $\mathrm{RI}_i$ |                                         | 1.88                  | 2.93                  |

| Growth rate (Å/s)                        | $GR_b$          |                                         | 10.8                  | 45.6                  |

|                                          | $GR_i$          |                                         | 10                    | 47                    |

| $V_{\rm th1h}~(\%)$                      |                 | Constant current $V_{\rm th}$           | 4.7                   | 42.45                 |

| $V_{\text{th}24h} - V_{\text{th}1h}$ (%) |                 | <del></del>                             | 2.02                  | 19.21                 |

| J (A/cm <sup>2</sup> ) at -75 V          |                 | HP4156                                  | $8.3 \times 10^{-9}$  | $3.2 \times 10^{-6}$  |

for the interface and distinguished respectively by b or i indices. Note that to determine the interfacial properties, the film is deposited by applying a rf power corresponding to the rf power ramp up at 1 s deposition time. Concerning electrical properties, leakage current in the PMD stack and DR of programed cell after 1 and 24 h bake at 250 °C were analyzed.

A large composition domain is investigated as illustrated by the large bulk index  $1.88 < RI_b < 2.36$  and an even larger interface one  $1.88 < RI_i < 2.93$  (Table I). Table II summarizes all Pareto and variation analysis and shows, by arrow or nonmonotone dependence, each significant response variation when factors increase. A cell blackening illustrates their importance. For example, Si–H bond concentration is first controlled by the rf power and second parameter is the SiH<sub>4</sub> flow. It decreases when the rf power increases and it increases when the SiH<sub>4</sub> flow increases.

# III. PHYSICAL A-SI<sub>X</sub>N<sub>Y</sub>: H PROPERTIES ACCORDING TO PECVD PROCESS PARAMETERS

Overall, the rf power and SiH<sub>4</sub> flow appear of huge importance. For the hydrogen bonds and RI<sub>b</sub>, this dependence is clearly understood by the bonding decomposition effects. Indeed, at low rf power and high SiH<sub>4</sub> flow, the SiH<sub>4</sub> decomposition is predominant. It results in an increase of the silicon rate contained in the film, as displays by the RI increase. RI<sub>i</sub> could be interpreted by the same way by reasoning with the power ramp up instead of rf power. Concerning the hydrogen bonds, the dependence with precursor gas ratio and rf power is well known: high SiH<sub>4</sub>/NH<sub>3</sub> ratio and low rf power make Si–H predominant than N–H and inversely for N–H one. Then, tensile stress and low density value are obtained at low rf power because of lower electronic bombardment

Fig. 1. (a) Schematic SP NVM and (b) a-Si<sub>x</sub>N<sub>y</sub>:H CESL transmission electron microscope images without or with rf power ramp up.

during the process. Film physical properties knowledge will be used to understand how they impact the DR in the following part.

#### IV. IMPACT OF A-SIXNY: H PROPERTIES ON DR

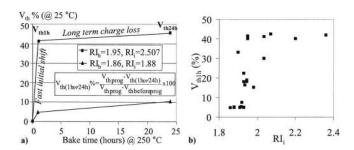

DR experiments have been performed at 250 °C on programed cells. Figure 2(a) depicts the normalized  $V_{\rm th}$  variation. This is represented according to bake time for the best and the worst cases of the DOE recipes. If the long term charge loss follows a similar dynamics (similar slope between  $V_{\text{th1h}}$  and  $V_{\text{th24h}}$ ), the fast initial one varies from few percent up to 40%. It highlights how much the initial shift is a a-Si<sub>r</sub>N<sub>v</sub>: H composition matter contrary to the intrinsic one. Thus, two DR DOE responses were defined to make the distinction between both mechanisms. The initial charge loss is monitored after 1 h bake time  $(V_{th1h})$  and the intrinsic one at 24 h through  $V_{\text{th}24\text{h}} - V_{\text{th}1\text{h}}$ . This last is confirmed to be independent of deposition parameters, contrary to  $V_{\rm th1h}$ (Table II). Precisely, it is shown that the SiH<sub>4</sub> flow mainly drives the  $V_{th1h}$  shifts. Putting this flow in its high level or increasing the SiH<sub>4</sub>/NH<sub>3</sub> precursor gas ratio accelerates the initial charge loss. Consequently, degradation is increased with Si-rich CESL film. In addition,  $V_{\text{th1h}}$  increases when the rf power ramp up decreases, i.e., when interfacial layer is thick. This interfacial layer, being more Si-rich than the bulk, confirms the previous conclusion and explains the strong quasilinear relationship between the initial charge loss and  $RI_i$  [Fig. 2(b)]. On the other hand, stress and density do not play a role on the DR degradation—even on the intrinsic long term one, which is of importance for silicon nitride

TABLE II. DOE analysis responses vs factors (interactions not presented).

|                         | $\{Si-H\}_b$ | [N-H] <sub>b</sub> | Stress <sub>b</sub> | Density <sub>b</sub> | $RI_b$ | $RI_i$ | $GR_b$ | $GR_i$ | Vthus        | Vth <sub>24h</sub> -  | r   |

|-------------------------|--------------|--------------------|---------------------|----------------------|--------|--------|--------|--------|--------------|-----------------------|-----|

| A:SiH <sub>4</sub> flow | -2           | - Nr.              | 1                   |                      | 2      | 2      | 2      |        | 2            | tor                   | - 2 |

| B:NH <sub>3</sub> flow  |              | ^                  | 7                   |                      | N      | 7      | 125    | 7      | 100          | unt fac               |     |

| C:Ramp RF               |              |                    |                     |                      |        | 7      |        | ^      | 8            | No significant factor | 1   |

| D:RF Power              | . Y          | 7                  | 7                   | 7                    | S      |        | ¥      |        | O COLUMN TWO | No sig                | 7   |

Fig. 2. (a)  $V_{th}$  for the worst and the better data retention  $a\text{-Si}_xN_y$ :H recipe and (b) link between  $V_{th1h}$  and composition illustrated by the RI<sub>i</sub>.

strained technologies, but in contradiction with stress reported results on double poly Flash cell. In conclusion, to minimize the initial charge loss, Si-rich film and thick interfacial layer must be avoided.

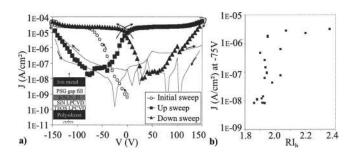

Why such a a-Si<sub>x</sub>N<sub>y</sub>:H composition is degrading? First assumptions are based on a larger defect amount. To confirm it, leakage current (J) has been measured in the complete PMD stack, between the polysilicon gate and the metal 1 electrodes at room temperature [Fig. 3(a)]. Hysteresis method is used with scanning voltage between ±150 V after an initial sweep from 0 V. Different defect contributions can be distinguished in the I-V characteristic represented with symbols. First of all, the more defect amount, the more leakage current. Then, a leakage current plateau appears, while voltage increases. It reduces the a-Si<sub>x</sub>N<sub>y</sub>:H ability to store charge and is correlated to the large hysteresis opening observed between up and down sweeps. These different defect contributions are strongly dependent on the a-Si<sub>x</sub>N<sub>v</sub>:H recipes and seem to be particularly linked with DR response. Indeed, the I-V of Fig. 3(a), in which the largest leakage and widest plateau are observed, corresponds to the worst DR case presented in Fig. 2(a). Note that almost no hysteresis opening and lower leakage are observed on the best recipe (curve without symbol). To be interpreted in the DOE analysis, the J parameter has been extracted at -75 V on the initial sweep. It ensures to characterize an initial defect state without trapped charge during previous cycle, which is not realistic during flash DR measurements. The bias is chosen to be sufficiently high to be outside the noise level and low to not enter in the trapping plateau. Results reported in Fig. 3(b)

Fig. 3. (a) J-V on PMD stack. Curve with symbols refers to the worst a- $Si_xN_y$ :H data retention case ( $RI_i$ := 2.507 and  $RI_b$ =1.95). Curve without symbol refers to the best a- $Si_xN_y$ :H data retention case ( $RI_i$ := 1.88 and  $RI_b$ =1.86) and (b) leakage current measured at -75 V on the initial I-V sweep according to  $RI_b$ .

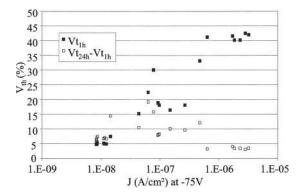

Fig. 4. Correlation between data retention degradation and defect amount contained in a-Si<sub>x</sub>N<sub>y</sub>:H  $V_{th}$  as monitored by leakage current.

reveal an increase of leakage current, i.e., defect amount, with Si-rich a-Si $_x$ N $_y$ :H film composition. Moreover, the quasilogarithmic dependence between  $V_{th1h}$  and J (Fig. 4) indicates the strong relationship between DR and the CESL defect monitored through J. It is necessary to remind that J is only used to give information about defects amount in CESL. Indeed, it is not realistic to correlate directly the CESL leakage to DR due to the good quality thick LPCVD dielectric that encapsulates the memory and keep the CESL separated from the floating gate.

#### V. DR DEGRADATION MODEL

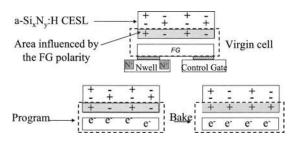

In Ref. 6, we have identified unexpected a-Si<sub>x</sub>N<sub>y</sub>:H charge behaviors from electrical measurements performed on MIS structures. These charges have the ability to exist under two states: positive and negative, leading us to suspect a K center origin. 10 UV erase enables us to neutralize this charge transforming K center in its neutral configuration  $K^{o}$ . Moreover, under thermal activation, an electrical field leads to a charge displacement or more probably a carrier exchange between trap centers. It is supposed that during the DR bake, the FG polarity, under its programed or erased states, creates an electrical field that can displace CESL charges from one interface to the other very similarly than during ionic contamination issue. An illustration is proposed on Fig. 5. At the beginning, the memory is in its virgin state and a-Si<sub>x</sub>N<sub>y</sub>:H charges are uniformly distributed. This simplification gives a layer globally neutral and has ever been suggested by Warren

Fig. 5. Illustration of initial shift during data retention experiment of a programed SP NVM cell. Gray area is influenced by polarity of the FG, which under its programed states and under thermal activation attracts positive  $a\text{-Si}_xN_y$ : H charges that screen those of the FG.

et al. for K centers. 11 Then, memory is programed, giving a negative polarity in the FG. This negative "electrode" induces an electrical field in the a-Si<sub>x</sub>N<sub>y</sub>:H. This FG field influence is, of course, higher close to the FG and explains the strong influence of the CESL bottom interfacial layer schematized by the gray filling. It was only during the high temperature bake that the a-Si<sub>x</sub>N<sub>y</sub>:H charges can be displaced by the electrical field. It leads to a positive charge sheet at the bottom of the CESL due to hole attraction or electron repulsion between traps centers. Thus, these CESL charges screen the ones stored in the FG. This capacitive effect has been well modeled by Mora et al.<sup>3</sup> The only way to distinguish this mechanism with classical ionic contamination effect is based on the Mielke cycle: During program and bake sequence, the behavior is similar and correction to charge motion. During UV erase step, in ionic contamination case, only memory is erased and the ionic charge are still present; on the contrary, in the case of CESL impact DR, the memory is erased and the K centers become neutral. This leads to completely different state and different response to the following bake. Note that such a difference is not visible when electrical erase is performed.

#### VI. CONCLUSION

The a-Si<sub>x</sub>N<sub>y</sub>:H CESL influence on DR mechanism is clearly identified here. We have demonstrated, on a large

*a*-Si<sub>x</sub>N<sub>y</sub>:H composition range, that Si-rich film and "interfacial" layer must be avoided to minimize memory charge loss. On the other hand, stress and density do not play a role. To optimize process deposition, it is particularly important to lower the SiH<sub>4</sub> flow and the rf power ramp up parameters. Indeed, they promote Si-rich films that were suspected to contain larger charge amount that screen charges stored in the FG.

- <sup>1</sup>R. Bottini, A. Cascella, E. Pio, and B. Vajana, IEEE IIRW, 1995 (unpublished), p. 18.

- <sup>2</sup>P. Mora, S. Renard, G. Bossu, P. Waltz, G. Pananakakis, and G. Ghibaudo, Proceedings of the Sixth Symposium on SiO<sub>2</sub> Advanced Dielectrics and Related Devices, 2006 (unpublished), pp. 34–36.

- <sup>3</sup>P. Mora, S. Renard, G. Bossu, P. Waltz, G. Pananakakis, and G. Ghibaudo, Proceedings of the IEEE IRW, 2006 (unpublished), p. 68.

- <sup>4</sup>M. Quirk and J. Serda, *Semiconductor Manufacturing Technology*, (Prentice Hall Editors, Upper Saddle River, NJ, 1995), p. 214.

- <sup>5</sup>G. Beylier, S. Bruyère, and G. Ghibaudo, Microelectron. Eng. **84**, 1990 (2007).

- <sup>6</sup>G. Beylier, S. Bruyère, D. Benoit, and G. Ghibaudo, Microelectron. Reliab. **47**, 743 (2007).

- <sup>7</sup>C. Y. Wang *et al.*, Symp. Proc. Mat. Res. Soc., 2001 (unpublished), p. 66.

- <sup>8</sup>H. S. Yang et al., IEEE IEDM, 2004 (unpublished), p. 1075.

- <sup>9</sup>R. Arghavani *et al.*, IEEE Trans. Electron Devices **54**, 362 (2007).

- <sup>10</sup>J. Robertson, Philos. Mag. B **69**, 307 (1994).

- <sup>11</sup>W. L. Warren, J. Kanicki, J. Robertson, E. H. Poindexter, and P. J. McWhorter, J. Appl. Phys. **74**, 4034 (1993).