### Design of Parallel LDPC Interleaver Architecture: A Bipartite Edge Coloring Approach

Awais. H. SANI, P. Coussy, C Chavet, E. Martin University Bretagne-Sud / Lab-STICC awais-hussain.sani@univ-ubs.fr

December 14, 2010

### Outline

Problem Formulation

Modeling

Algorithm

Conclusion

2

ICECS 2010 December 14, Athens Greece

www.univ-uhs.fr

### Outline

- Problem Formulation

- Modeling

- Algorithm

- Conclusion

### **Problem Formulation**

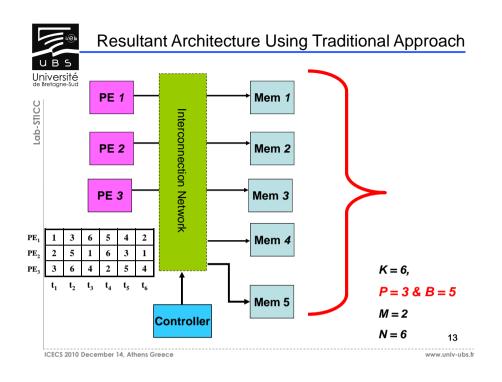

- Set of K data elements  $\{d_0, d_1, \dots, d_{K-1}\}$

- Set of *P* processing elements  $\{PE_{0}, PE_{1}, \dots, PE_{P-1}\}$

- Set of B = P memory banks  $\{b_0, b_1, \dots, b_{P-1}\}$

- Size of each memory bank M = K/P

- Set of N time instances  $\{t_1, t_2, \dots, t_N\}$  in which P processing elements process K data elements.

4

Lab-STICC

### **Problem Formulation**

• Set of K data elements  $\{d_0, d_1, \dots, d_{K-1}\}$

• Set of P processing elements  $\{PE_0, PE_1, \dots, PE_{P-1}\}$

- Set of B = P memory banks  $\{b_0, b_1, \dots, b_{P-1}\}$

- Size of each memory bank M = K/P

- Set of N time instances  $\{t_1, t_2, \dots, t_N\}$  in which P processing elements process K data elements.

**Mapping problem:** Store K data elements in B memory banks in such a manner that P processing element can access B memory banks in parallel at each time instance for first reading and then writing B data elements without any conflict.

5

ICECS 2010 December 14, Athens Greece

www.univ-ubs.fr

# U B S Université

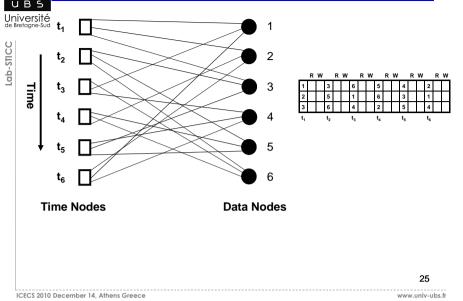

### Example

• Set of

- Set of *K* data elements  $\{d_0, d_1, \dots, d_{K-1}\}$

- Set of P processing elements  $\{PE_{0}, PE_{1}, \dots, PE_{P-1}\}$

- Set of B = P memory banks  $\{b_0, b_1, \dots, b_{P-1}\}$

- Size of each memory bank M = K/P

- Set of N time instances  $\{t_1, t_2, \dots, t_N\}$  in which P processing elements process K data elements.

**Data Access Matrix**

-

ICECS 2010 December 14, Athens Greece

www.univ-ubs.fr

# U B S Université

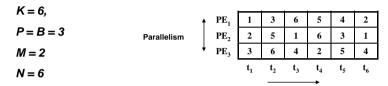

# Traditional Approach

K=6,

P=B=3,

M = 2

N = 6

ICECS 2010 December 14, Athens Greece

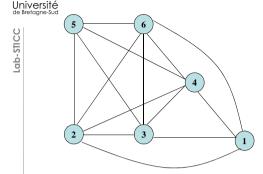

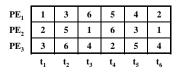

### **Conflict Access Graph**

| $PE_1$          | 1              | 3              | 6              | 5              | 4              | 2              |

|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| $PE_2$          | 2              | 5              | 1              | 6              | 3              | 1              |

| PE <sub>3</sub> | 3              | 6              | 4              | 2              | 5              | 4              |

|                 | t <sub>1</sub> | t <sub>2</sub> | t <sub>3</sub> | t <sub>4</sub> | t <sub>5</sub> | t <sub>6</sub> |

7

www.univ-ubs.fr

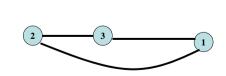

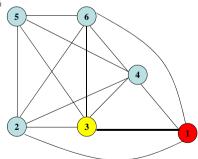

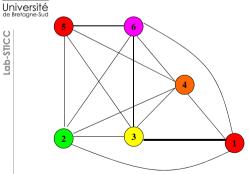

## Traditional Approach

**Conflict Access Graph**

K = 6,P = B = 3,

M=2

N = 6

8

ICECS 2010 December 14, Athens Greece

www.univ-ubs.fr

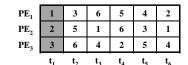

# Traditional Approach

**Conflict Access Graph**

P = B = 3.

M = 2

N = 6

| $PE_1$          | 1  | 3  | 6  | 5  | 4  | 2  |

|-----------------|----|----|----|----|----|----|

| $PE_2$          | 2  | 5  | 1  | 6  | 3  | 1  |

| PE <sub>3</sub> | 3  | 6  | 4  | 2  | 5  | 4  |

|                 | f. | f. | t. | t. | f. | t. |

ICECS 2010 December 14. Athens Greece

www.univ-ubs.fr

# Traditional Approach

**Conflict Access Graph**

K = 6.

P = B = 3.

M = 2

N = 6

| PE <sub>1</sub> | 1  | 3  | 6  | 5  | 4  | 2  |

|-----------------|----|----|----|----|----|----|

| $PE_2$          | 2  | 5  | 1  | 6  | 3  | 1  |

| PE <sub>3</sub> | 3  | 6  | 4  | 2  | 5  | 4  |

|                 | f. | t. | t. | t. | t. | t. |

ICECS 2010 December 14. Athens Greece

www.univ-ubs.fr

# Université

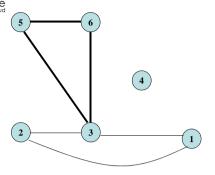

# Traditional Approach

$$K = 6$$

,

P = B = 3.

M = 2

N = 6

| (5) (6) |

|---------|

|         |

|         |

|         |

| (4)     |

|         |

|         |

| 2 3     |

|         |

|         |

### **Conflict Access Graph**

Nodes connected with the same edge should be of different color and each color represents memory bank.

www.univ-ubs.fr

## Traditional Approach

**Conflict Access Graph**

We need 5 memory banks to access 6 data elements.

$$P = B = 3$$

,

$$M = 2$$

| $PE_1$ | 1  | 3              | 6  | 5  | 4  | 2  |

|--------|----|----------------|----|----|----|----|

| $PE_2$ | 2  | 5              | 1  | 6  | 3  | 1  |

| $PE_3$ | 3  | 6              | 4  | 2  | 5  | 4  |

|        | t. | t <sub>2</sub> | t, | t. | t. | t. |

# New Approach

To tackle this problem, we introduce the concept of multiple read and multiple write access Concept.

14

ICECS 2010 December 14, Athens Greece

www.univ-uhs.fr

# Université

ICECS 2010 December 14, Athens Greece

# New Approach

**Mapping Matrix**

15

www.univ-ubs.fr

U B S Université

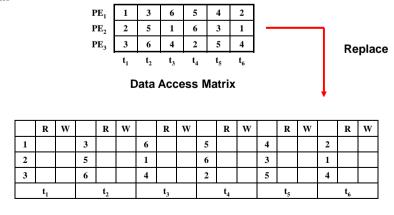

### **Constraints**

Mapping Constraints:

• At each time instance, all the memory banks in the read column (resp. in the write column) of the mapping matrix must be different.

**Mapping Matrix**

16

ICECS 2010 December 14, Athens Greece

, Athens Greece www.univ-ubs.fr

### Constraints

U B S Université

### Constraints

### **Mapping Constraints:**

- At each time instance, all the memory banks in the read column (resp. in the write column) of the mapping matrix must be different.

- The bank of the last write access to a data must be the same as the bank of its first read access.

|                               | R | W |    | R | W |                | R | W |                | R | W |                | R | W |   | R | W |

|-------------------------------|---|---|----|---|---|----------------|---|---|----------------|---|---|----------------|---|---|---|---|---|

| 1                             |   |   | 3  |   |   | 6              |   |   | 5              |   |   | 4              |   |   | 2 |   |   |

| 2                             |   |   | 5  |   |   | 1              |   |   | 6              |   |   | 3              |   |   | 1 |   |   |

| 3                             |   |   | 6  |   |   | 4              |   |   | 2              |   |   | 5              |   |   | 4 |   |   |

| t <sub>1</sub> t <sub>2</sub> |   |   | t, |   |   | t <sub>4</sub> |   |   | t <sub>s</sub> |   |   | t <sub>6</sub> |   |   |   |   |   |

**Mapping Matrix**

18

ICECS 2010 December 14, Athens Greece

www.univ-ubs.fr

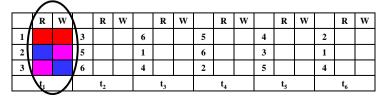

### **Mapping Constraints:**

- At each time instance, all the memory banks in the read column (resp. in the write column) of the mapping matrix must be different.

- The bank of the last write access to a data must be the same as the bank of its first read access.

|   | R                             | W |                | R | W |                | R | W |                | R | W |                | R | W |   | R | W |

|---|-------------------------------|---|----------------|---|---|----------------|---|---|----------------|---|---|----------------|---|---|---|---|---|

| 1 |                               |   | 3              |   |   | 6              |   |   | 5              |   |   | 4              |   |   | 2 |   |   |

| 2 |                               |   | 5              |   |   | 1              |   |   | 6              |   |   | 3              |   |   | 1 |   |   |

| 3 |                               |   | 6              |   |   | 4              |   |   | 2              |   |   | 5              |   |   | 4 |   |   |

|   | t <sub>1</sub> t <sub>2</sub> |   | t <sub>3</sub> |   |   | t <sub>4</sub> |   |   | t <sub>5</sub> |   |   | t <sub>6</sub> |   |   |   |   |   |

**Mapping Matrix**

17

ICECS 2010 December 14, Athens Greece

www.univ-ubs.fr

# U B S

## Outline

- Problem Formulation

- Modeling

- Preparing Bipartite Graph

- Algorithm

- Conclusion

U B S

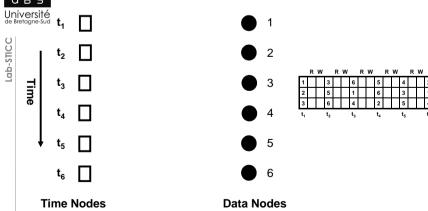

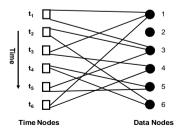

# **Preparing Bipartite Graph**

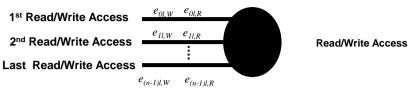

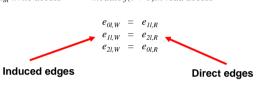

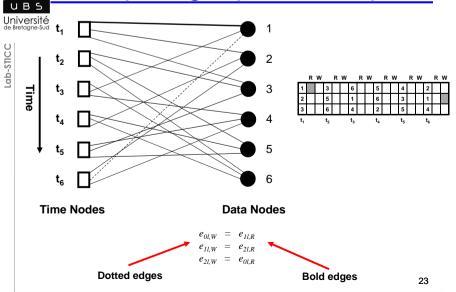

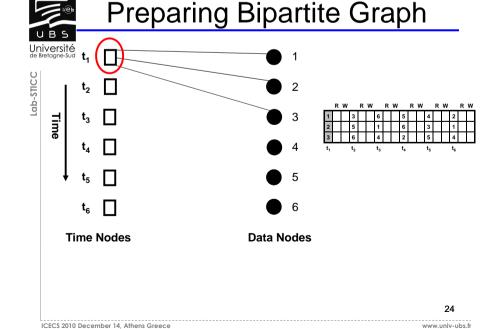

### **Preparing Bipartite Graph**

Lab-STICC

Data Node Representation

### Where

$e_{0l,R}$  and  $e_{(n-1)l,R}$  represent first and last read access of the data l respectively.  $e_{0l,W}$  and  $e_{(n-1)l,W}$  represent first and last write access of the data l respectively.

21

www.univ-ubs.fr

ICECS 2010 December 14, Athens Greece

ICECS 2010 December 14, Athens Greece

www.univ-ubs.fr

# u B S Université

### **Preparing Bipartite Graph**

Placement Property:

$i_{th}$  write access =  $modulo_{degree l}(i + 1)$  read access

This placement property is used to search edges during algorithm.

The read access of the  $i_{th}$  write access is called *direct edge* whereas the corresponding write access is called *induced edge* next in this presentation.

for  $(degree\ I) = 3$

$i_{th}$  write access =  $modulo_3(i+1)th$  read access

ICECS 2010 December 14. Athens Greece

www.univ-ubs.fr

# Preparing Bipartite Graph

# **Preparing Bipartite Graph**

# Université

Outline

Problem Formulation

Modeling

• Preparing Bipartite Graph

**Algorithm**

- Partitioning

- Coloring

- Conclusion

26

ICECS 2010 December 14. Athens Greece

www univ-ubs fr

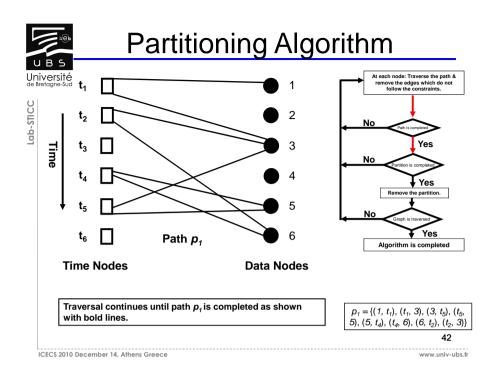

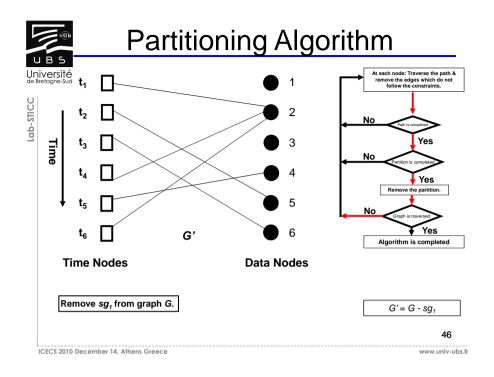

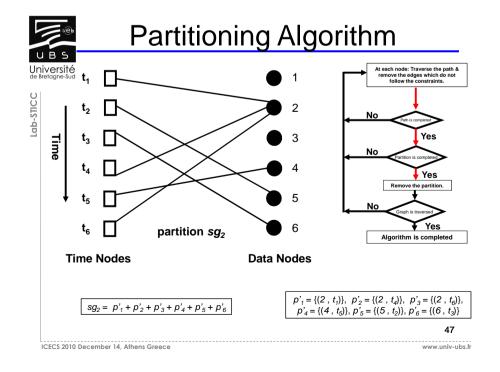

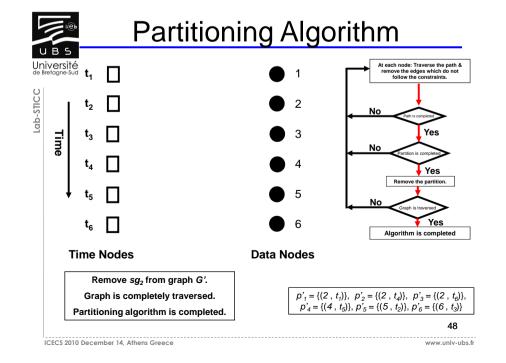

## Partitioning Algorithm

### **Proper Partition:**

Proper partition is the subgraph in which all the time vertices have degree 2.

Proper partitioning with each time vertex degree 2.

Proper partition is the subgraph in which all the time vertices have degree 1.

Regular partitioning with each time vertex degree 1.

www.univ-ubs.fr

Université

## Partitioning Algorithm

### **Partitioning Constraint:**

No more than 2 read or write accesses have to be done at each time instance in a proper partition.

Proper partitioning with each time vertex degree 2.

ICECS 2010 December 14, Athens Greece

### Partitioning Algorithm

### Partitioning Algorithm

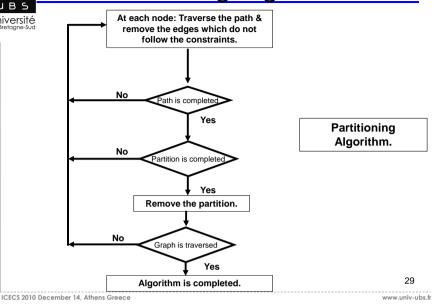

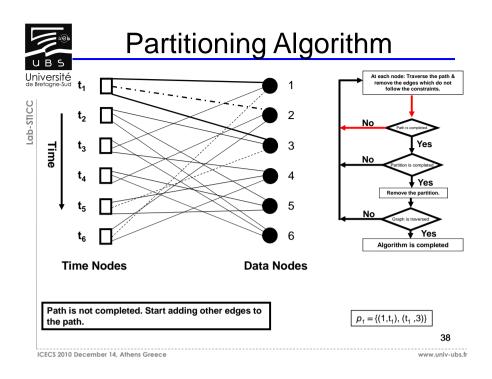

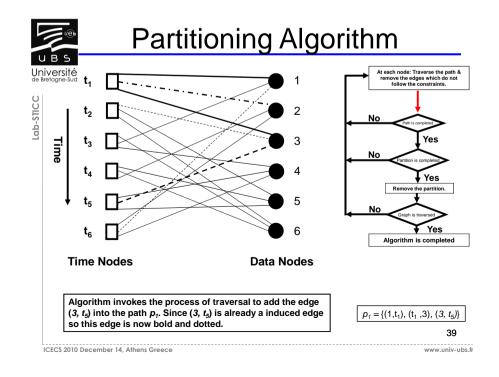

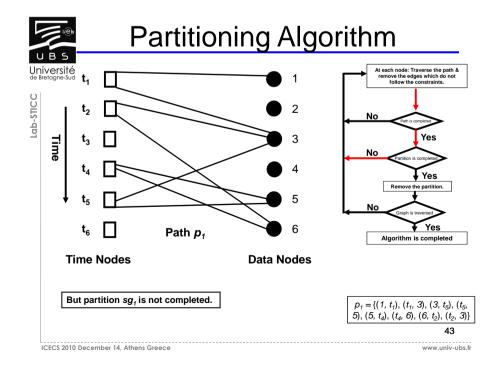

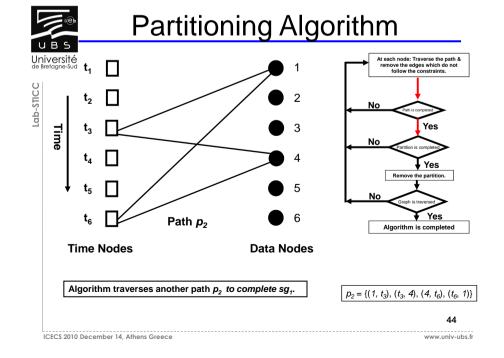

### **Partitioning Algorithm:**

- · Process of Traversal

- · Process of Elimination

30

ICECS 2010 December 14. Athens Greece

www.univ-uhs.fr

# Partitioning Algorithm

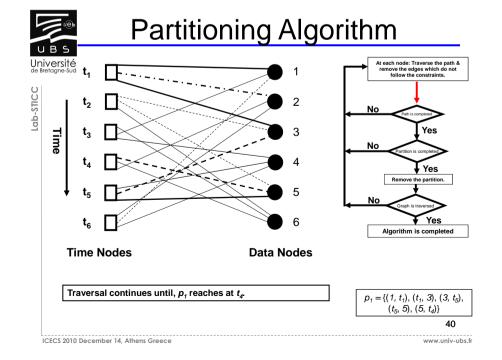

### Partitioning Algorithm:

- · Process of Traversal

- · Process of Elimination

### **Process of Traversal**

- 1. Randomly selects the edge available at the current data and time vertex.

- 2. Records the induced edge of the selected edge.

## Partitioning Algorithm

### Partitioning Algorithm:

- Process of Traversal

- · Process of Elimination

### **Process of Traversal**

- 1. Randomly selects the edge available at the current data and time vertex.

- 2. Records the induced edge of the selected edge.

### **Process of Elimination**

Removes the edges from current partition, the selection of which makes the construction of proper partition following "partitioning constraint" impossible.

31

3

ICECS 2010 December 14, Athens Greece www.univ-ubs.fr

ICECS 2010 December 14, Athens Greece www.univ-ubs

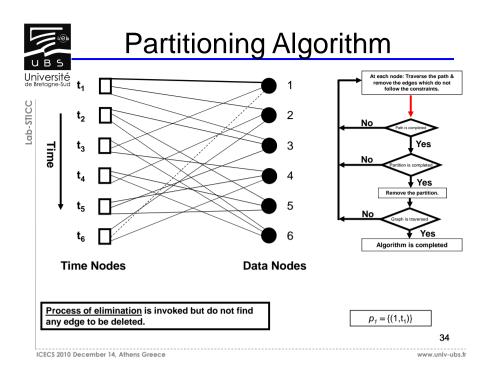

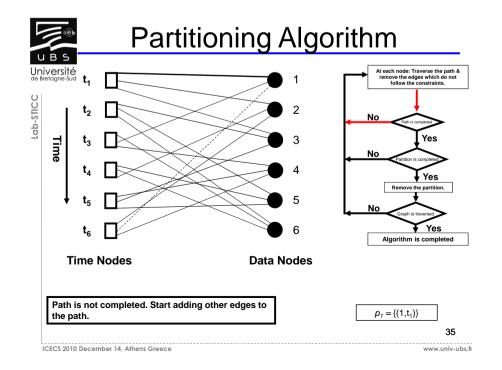

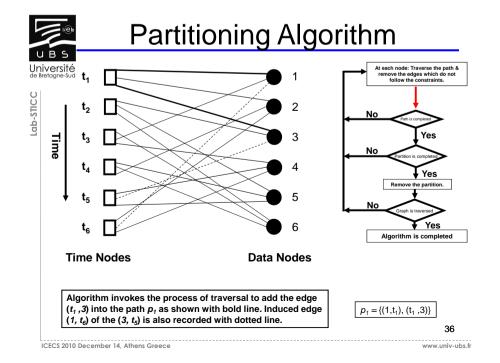

# Partitioning Algorithm UBS Université de Breitagne-Sud $t_1$ $t_2$ $t_3$ $t_4$ $t_5$ Time Nodes Data Nodes Algorithm invokes the process of traversal to add the edge $(1, t_1)$ into the path $\rho_1$ as shown with bold line. Induced edge $(1, t_2)$ into the path $\rho_2$ as shown with bold line. Induced edge $(1, t_3)$ of the $(1, t_4)$ is also recorded with dotted line.

www.univ-ubs.fr

# Partitioning Algorithm UBS Université de Bretogne-Sud $t_1$ $t_2$ $t_3$ $t_4$ $t_5$ Time Nodes Process of elimination is invoked and found that two read accesses are done at $t_n$ other read accesses at $t_r$ is deleted as shown with large and small dotted line. Process of elimination is invoked and found that two read accesses are done at $t_n$ other read accesses at $t_r$ is deleted as shown with large and small dotted line. Process of elimination is invoked and found that two read accesses are done at $t_n$ other read accesses at $t_r$ is deleted as shown with large and small dotted line.

www.univ-ubs.fr

# Partitioning Algorithm Université de Bretagne-Sud $t_1$ $t_2$ $t_3$ $t_4$ $t_5$ Time Nodes Process of elimination finds that 2 write accesses is done at $t_2$ as shown through induced edges. So other edges, $(t_3, 6)$ in this case, which have write accesses at $t_2$ is deleted. Process of elementation finds that $t_3$ write accesses at $t_4$ is deleted. $p_1 = \{(1, t_1), (t_1, 3), (3, t_5), (t_5, 5), (5, t_4)\}$

www.univ-ubs.fr

# Partitioning Algorithm Partitioning Algorithm At each node: Traverse the path & remove the edges which do not follow the constraints. Time Nodes Partition $sg_1$ is completed. Partition $sg_2$ is completed. Partition $sg_3$ is completed. $sg_1 = p_1 + p_2$

www.univ-ubs.fr

SIICC

### **Outline**

- Problem Formulation

- Modeling

- Preparing Bipartite Graph

- Algorithm

- Partitioning

- Coloring

- Conclusion

49

ICECS 2010 December 14, Athens Greece

www.univ-ubs.fr

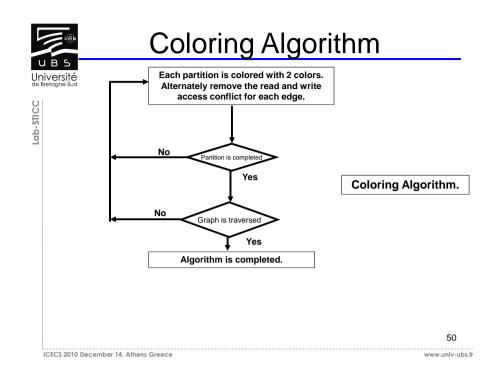

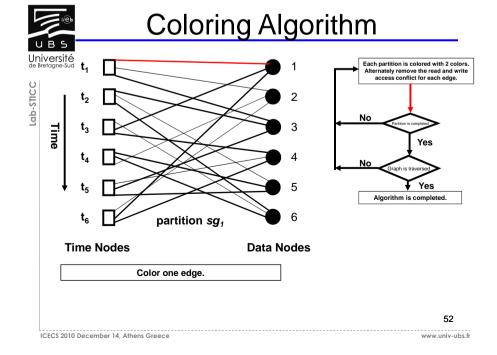

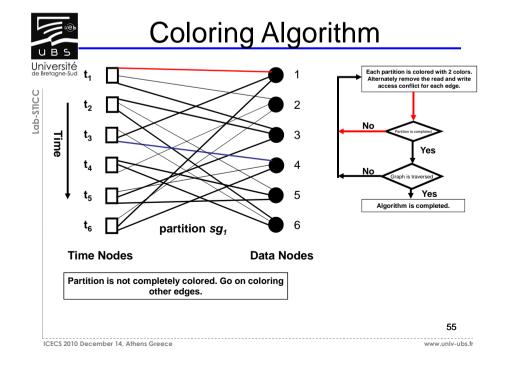

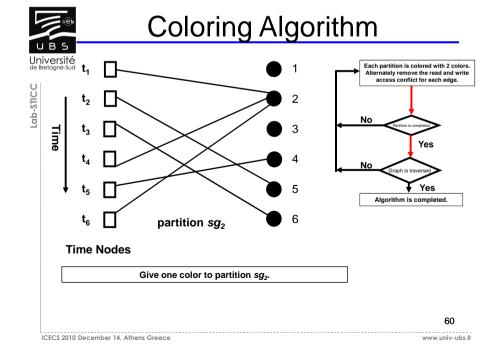

### Coloring Algorithm Université Each partition is colored with 2 colors. Alternately remove the read and write access conflict for each edge. Lab-STICC No Time Yes Algorithm is completed. partition sg<sub>1</sub> **Time Nodes Data Nodes** 51 ICECS 2010 December 14, Athens Greece www.univ-ubs.fr

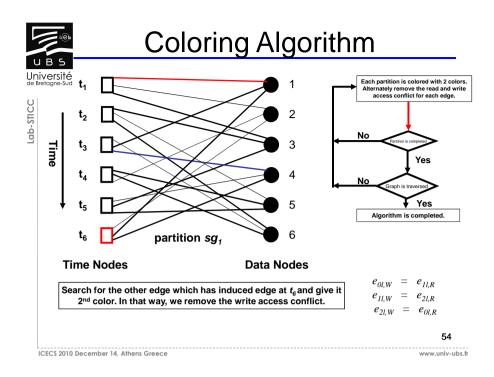

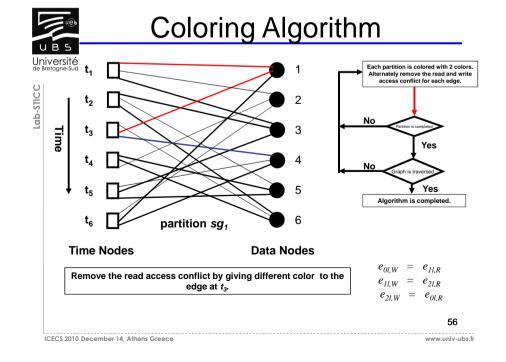

### **Coloring Algorithm** Université Each partition is colored with 2 colors. Alternately remove the read and write access conflict for each edge. No Time Yes Yes Algorithm is completed. partition sg **Data Nodes Time Nodes** $e_{0LW} = e_{1LR}$ Search for the time node in which induced edge of the current $e_{1LW} = e_{2LR}$ colored edge exits. $t_6$ is the required node. $e_{2l,W} = e_{0l,R}$ 53

www.univ-ubs.fr

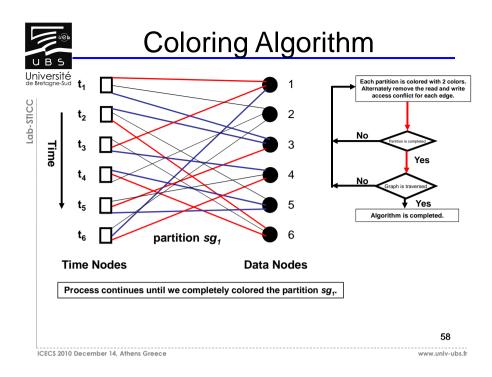

### **Coloring Algorithm** Université Each partition is colored with 2 colors. Alternately remove the read and write access conflict for each edge. No Time Yes Yes Algorithm is completed. partition sg **Data Nodes Time Nodes** $= e_{1l,R}$ Remove the write access conflict by searching for induced edges. $= e_{2l,R}$ $e_{1l,W}$ $e_{2l,W} = e_{0l,R}$ 57

www.univ-ubs.fr

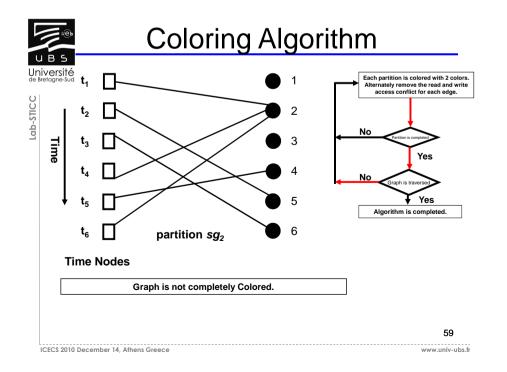

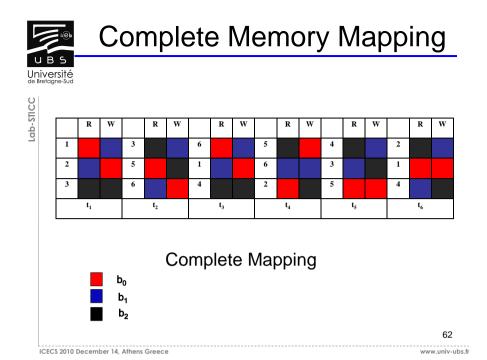

# Coloring Algorithm Université de Bretogne-Sud t<sub>1</sub> t<sub>2</sub> t<sub>3</sub> t<sub>4</sub> t<sub>5</sub> Graph G Data Nodes Graph is completely colored. Coloring algorithm is completed. Graph is completed.

ICECS 2010 December 14. Athens Greece

## Outline

- Problem Formulation

- Modeling

- Preparing Bipartite Graph

- Algorithm

- Partitioning

- Coloring

- Conclusion

### Conclusion

- · Concept of multiple read/write approach is presented.

- Modified bipartite edge coloring approach is introduced to find conflict free memory mapping for any type of parallel iterative decoding for LDPC.

www.univ-ubs.fr

04

www.univ-ubs.fr

63

ICECS 2010 December 14, Athens Greece

s.fr ICECS 2010 December 14, Athens Greece

www.univ-ubs.fr

## **Future Perspectives**

# • Additional constraints will be added in order to find

mapping following the targeted interconnection network.

• Complexity of the interconnection network is considered in the future development of the mapping algorithm.

65

ICECS 2010 December 14, Athens Greece www.univ-ubs.fr

### Questions

ab-STIC

66

ICECS 2010 December 14. Athens Greece www.univ-ubs.fr