## A Real-Time Predictive-Maintenance System of Aluminum Electrolytic Capacitors Used in Uninterrupted Power Supplies

Mohamed Karim Abdennadher, Pascal Venet, Gérard Rojat, Jean-Marie Rétif, Christophe Rosset

### ▶ To cite this version:

Mohamed Karim Abdennadher, Pascal Venet, Gérard Rojat, Jean-Marie Rétif, Christophe Rosset. A Real-Time Predictive-Maintenance System of Aluminum Electrolytic Capacitors Used in Uninterrupted Power Supplies. IEEE Transactions on Industry Applications, 2010, 46 (4), pp.1644 - 1652. 10.1109/TIA.2010.2049972. hal-00536644

HAL Id: hal-00536644

https://hal.science/hal-00536644

Submitted on 18 Nov 2010

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# A Real-Time Predictive-Maintenance System of Aluminum Electrolytic Capacitors Used in Uninterrupted Power Supplies

Karim Abdennadher, *Student Member, IEEE*, Pascal Venet, *Member, IEEE*, Gérard Rojat, Jean-Marie Rétif, and Christophe Rosset, *Member, IEEE*

Abstract—This paper presents a low-cost method to realize a real-time condition monitoring and a predictive-maintenance system of an electrolytic capacitor used in uninterruptible power supplies (UPSs). This method consists in detecting the changes in real time of the equivalent series resistance and the capacitance C values of the electrolytic capacitors. Simulation and experimental results are presented to illustrate the proposed monitoring technique. The proposed method can be used in UPS where waveforms are continuously varying in amplitude, frequency, and temperature. The proposed online failure prediction method has the merits of using only the existent resources in UPS and with the use of known algorithms.

*Index Terms*—Electrolytic capacitors, identification, Kalman filtering, predictive maintenance, real time.

#### I. INTRODUCTION

ELECTROLYTIC capacitors have been widely used in power-electronic systems because they can achieve high capacitance and voltage ratings with volumetric efficiency and low cost. This type of capacitors has been traditionally used for filtering, coupling, timing networks, bypass, and many other applications in power electronics requiring a cost-effective and volumetrically efficient component. It is known that the common faults in electrolytic capacitor include initial catastrophic failures due to manufacturing or misapplication defect and wear-out faults, which cannot be avoided. Unfortunately, electrolytic capacitors are one of the weakest components in power-electronic converter [1]–[13]. For example [1], [4], in uninterruptible power supplies (UPSs), they are responsible

Manuscript received March 25, 2009; revised December 14, 2009; accepted January 14, 2010. Date of current version July 21, 2010. Paper 2009-IACC-065.R2, presented at the 2008 Industry Applications Society Annual Meeting, Edmonton, AB, Canada, October 5–9, and approved for publication in the IEEE Transactions on Industry Applications by the Industrial Automation and Control Committee of the IEEE Industry Applications Society.

K. Abdennadher and C. Rosset are with the Emerging Technologies Department of IT Business, Schneider Electric, INOVALLEE, 38334 Saint Ismier, France (e-mail: karim.abdennadher@mgeups.com; christophe.rosset@mgeups.com).

P. Venet, G. Rojat, and J.-M. Rétif are with the Electrical Engineering Laboratory (Laboratoire Ampère), UMR CNRS 5005, Université de Lyon, Université Lyon 1, 69622 Villeurbanne Cedex, France (e-mail: pascal.venet@univ-lyon1.fr; gerard.rojat@univ-lyon1.fr; jean-marie.retif@insa-lyon.fr).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TIA.2010.2049972

for about 50% of the cases of power-electronic component failures. An electrolytic capacitor has a number of root causes and failure modes. Degradation of this component is due to a combined effect of electrical, thermal, mechanical, and environmental stresses. The main wear-out failure mechanism is the evaporation of the electrolyte solution which is accelerated with temperature rise during the operation and due to ripple currents. This causes a decrease in C and an increase of the equivalent series resistance (ESR) which further increase the temperature (losses). Standard [2] suggests that the capacitor should be considered as failed if there is an increase that is double the initial ESR value and a 20% decrease in the capacitance value. Hence, estimation of ESR and the capacitance by taking into account the temperature is important for condition monitoring of the electrolytic capacitor. The purpose of this paper is to propose a method to detect in real time the changes in the value of the ESR and also of the capacitance in order to create a realtime predictive system of electrolytic-capacitor failures. It is further shown in this paper that the proposed method can be applied even in the nonstationary system, such as UPS, where capacitor ripple voltage and current are continuously varying in amplitude and frequency. They also depend on the ambient temperature where the converter operates.

Many papers have proposed different methods or algorithms to determine the ESR and/or capacitance C of the electrolytic capacitor [2]–[13]. However, many parameters, such as offline additional measurements, and many computations are required, which makes it complicated, difficult, expensive, and impractical for actual application.

Modern UPS can utilize a variety of accurate sensors, numerical treatment systems, and powerful computation resources which are used to control and regulate the UPS in order to improve its performance and efficiency. The suggested method has the merits of making a real-time predictive-maintenance system of electrolytic capacitors by using existing resources in the UPS. This predictive-maintenance system works in background tasks and without disturbing the regulation and the operating system.

#### II. ELECTROLYTIC-CAPACITOR TECHNOLOGY

#### A. Electrolytic-Capacitor Modeling

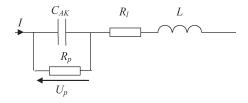

The structure of a screw-terminal electrolytic capacitor [16] is shown in Fig. 1.

Fig. 1. Structure of a screw-terminal electrolytic capacitor [16].

Fig. 2. Electrical equivalent circuit of an electrolytic capacitor.

Fig. 3. Normalized electrical equivalent circuit of an electrolytic capacitor.

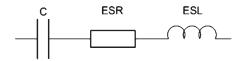

Due to physical design elements and construction, aluminum electrolytic capacitors are modeled by the electrical equivalent circuit [14], [17] shown in Fig. 2. This model, which is the most used one, is rather simple and gives a good frequency response.

In Fig. 2,  $C_{AK}$  is the ideal capacitance between anode and cathode,  $R_p$  is the parallel resistance which represents all the losses in the dielectric and the leakage between the two electrodes,  $R_l$  is the connection and electrode serial resistance, and L is connection and winding equivalent series inductance (ESL). This circuit can be simplified with the normalized representation given in Fig. 3. It is a series combination of an ESR which represents all the component losses, a capacitance C, and an ESL, which is due to the wound structure of the capacitor.

From the impedance equality between the circuit elements shown in Fig. 2 and those represented in Fig. 3, we can conclude the following equations, where  $\omega$  is the electrical pulsation:

$$C = C_{AK} \cdot \left(1 + \frac{1}{R_p^2 C_{AK}^2 \omega^2}\right) \tag{1}$$

$$ESR = R_l + \frac{R_p}{1 + R_p^2 C_{AK}^2 \omega^2} \tag{2}$$

$$ESL = L. (3)$$

This capacitor representation is important because it is directly given from the impedance frequency measurements. Therefore, the resonant frequency  $f_T$  of the capacitor is given by

$$f_r = \frac{1}{2 \cdot \pi \cdot \sqrt{ESL \cdot C}}. (4)$$

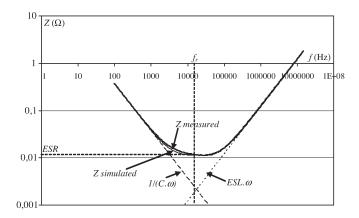

Fig. 4. Z(f) for aluminum electrolytic capacitor of 4700  $\mu$ F/500 V.

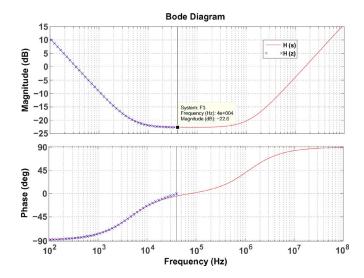

In addition, this simplified equivalent circuit can give a first approximation of the capacitor behavior without taking into account parameter variations of C, ESR, and ESL versus frequency. This theory can be demonstrated by the figure shown in Fig. 4, which represents the module Z of the complex impedance Z versus frequency, of an aluminum electrolytic capacitor of 4700  $\mu$ F/500 V. As can be observed from the bode plot, there exist three widely separated frequency bands. The capacitance of the capacitor is dominant in low-frequency band. ESL is dominant in high-frequency band, and ESR is dominant in the midfrequency one.

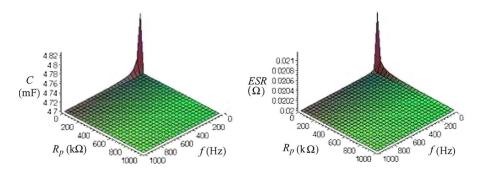

Equations (1) and (2) show that ESR and C can be considered separately from the frequency when the latter is not too low. Therefore, the resistance  $R_p$  has an effect only on very low frequencies (less than several tens of hertz). This is shown in Fig. 5, which represents the effect of  $R_p$  versus frequency f on the ESR and C parameters. It is an example of an electrolytic capacitor with a nominal capacitance value of 4700  $\mu \rm F$  and a nominal ESR of 20 m $\Omega$ .

#### B. Electrolytic-Capacitor Aging

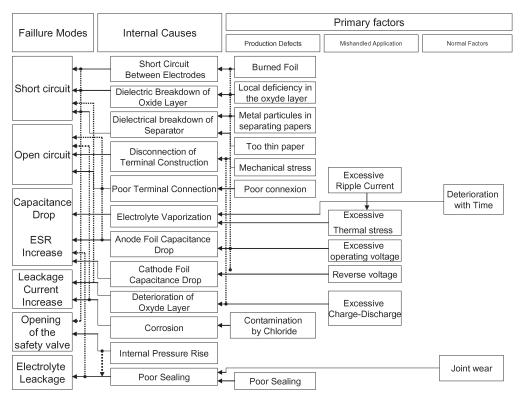

Fig. 6 [17] shows the majority of electrolytic-capacitor failure modes and their root causes. As can be seen, the estimation of ESR and  ${\cal C}$  can provide at least all the normal and use-failure defects. Therefore, the estimation of these two parameters is important to realize a real-time predictive-maintenance system of electrolytic capacitor.

#### III. ELECTROLYTIC-CAPACITOR MONITORING

#### A. Estimation of ESR and C

As we have just seen before, the electrolytic capacitors can be modeled as a serial combination of a capacitance, an ESL, and an ESR, as shown in Fig. 3. The bode plot of an electrolytic capacitor with  $ESR=74~\mathrm{m}\Omega$ ,  $ESL=10~\mathrm{nH}$ , and capacitance  $C=470~\mu\mathrm{F}$  is shown in Fig. 7. Therefore, the converters in the UPS works at a low-frequency band compared with the resonant-frequency one (4), so ESL is usually neglected, and the equivalent model of the capacitor is given by an ESR in series with a capacitance (C).

Fig. 5. Z(f) for aluminum electrolytic capacitor of 4700  $\mu$ F/500 V [17].

Fig. 6. Capacitor failures and their causes [17].

Fig. 7. Bode diagram of an electrolytic capacitor in continuous- and discrete-time domain.

The transfer function of this model is given by

$$H(s) = \frac{Uc(s)}{Ic(s)} = \frac{ESR \cdot C \cdot s + 1}{C \cdot s}.$$

(5)

However, converters are controlled by using digital treatments. We can consider the z-transform corresponding to (5) to represent the discrete-time domain by using the bilinear method of Tustin and which is given by (6), where Ts is the sampling period

$$H(z^{-1}) = \frac{b_0 + b_1 \cdot z^{-1}}{1 - z^{-1}}$$

$$= \frac{\left(ESR + \frac{T_s}{2 \cdot C}\right) + \left(\frac{T_s}{2 \cdot C} - ESR\right) \cdot z^{-1}}{1 - z^{-1}}.$$

(6)

The bode plot in Fig. 7 shows that the continuous- and discrete-time domain for a sampling period of  $Ts=12.5~\mu s$  are equivalent if we use the bilinear-method discrete time.

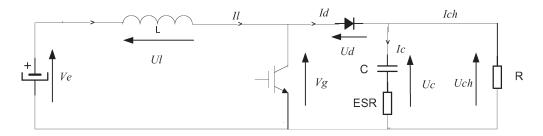

Fig. 8. Schematic of a boost-converter circuit with a dc capacitor circuit.

Fig. 9. Parameter identification using Kalman filter.

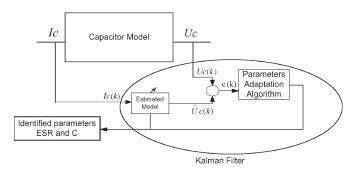

To identify  $b_0$  and  $b_1$  for the two parameters ESR and C, we use different forms of Kalman filter.

A Matlab simulation was performed using dynamic equation from the equivalent circuit shown in Fig. 8 of a boost-converter with a 50-V dc voltage input, with a switching frequency of 5 kHz and which is regulated to have a 200-V dc voltage output.

A recursive least square algorithm, which is a particular case of Kalman filter, was used as shown in Fig. 9.

In practice, we do not have a capacitor current sensor because it is difficult and expansive to implement in UPS. To perform and regulate the output voltage, we only dispose of one current sensor used to have the input current inductance L of the boost converter. However, we can identify the capacitor current using Kirchhoff's laws referring to the schematic of the boost converter shown in Fig. 8

$$Ic = Id - Ich. (7)$$

When the insulated-gate bipolar transistor is off (the pulsewidth modular PWM =0), we have Id=Il, so we can conclude the following:

$$Id = Il * \overline{PWM}. \tag{8}$$

In stationary process, the average capacitor current Ic is equal to zero, so, for one regulation period, we have the following:

$$Ic = Il * \overline{PWM} - \text{avg}(Il * \overline{PWM}).$$

(9)

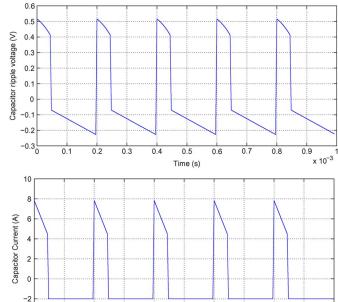

Respectively, the simulation results of the capacitor ripple voltage and capacitor current identified with the use of (9) are shown in Fig. 10.

The simulation results presented in this section are summarized in Table I.

Fig. 10. Matlab simulation results of capacitor ripple voltage  $\Delta Uc$  and capacitor current Ic.

0.5

Time (s)

0.7

0.8

0.9 x 10<sup>-3</sup>

0.6

0.4

TABLE I

SIMULATION RESULTS FOR ESTIMATED PARAMETERS

| $ESR_{fixed}$ | $ESR_{estimated}$ | % error |

|---------------|-------------------|---------|

| $74~m\Omega$  | 74.2 $m\Omega$    | 2.2     |

| $C_{actual}$  | $C_{estimated}$   | % error |

| $470~\mu F$   | $466~\mu F$       | 2.7     |

#### B. Aging Algorithm

0.1

0.2

0.3

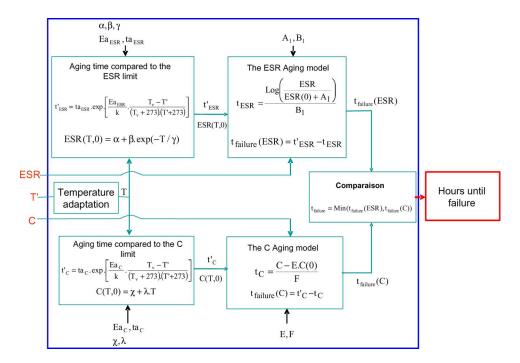

The aging algorithm, which takes into account the temperature, is given in the following.

The evolution of ESR and C versus ambient temperature  $T_a$  is given by the following equation [14] where  $\alpha$ ,  $\beta$ ,  $\gamma$ ,  $\chi$ ,  $\nu$ , and  $\lambda$  are experimental parameters and depend on the used capacitor:

$$ESR(T_a, t) = \alpha + \beta \cdot \exp\left(-\frac{T}{\gamma}\right) \tag{10}$$

$$C(T_a, t) = \chi + \lambda \cdot \exp\left(-\frac{T}{\nu}\right).$$

(11)

Fig. 11. Aging algorithm.

The time until failure compared with failure limits of ESR and C can be calculated by using the following [14]:

$$\frac{t'_{ESR}}{ta_{ESR}} = \exp\left[\frac{Ea_{ESR}}{k} \cdot \frac{T' - T_a}{(T' + 273) \cdot (T_a + 273)}\right] \quad (12)$$

$$\frac{t_C'}{ta_C} = \exp\left[\frac{Ea_C}{k} \cdot \frac{T' - T_a}{(T' + 273) \cdot (T_a + 273)}\right]$$

(13)

$$ESR(t_{ESR}) = (ESR(0) + A_1) \cdot \exp(B_1 \cdot t_{ESR}) \tag{14}$$

$$C(t_C) = E \cdot C(0) + F \cdot t_C \tag{15}$$

where

$T_a$ Ambient temperature (25 °C for example). T'Aging temperature (85 °C for example). Aging time for the ESR limit at  $T_a$ .  $ta_{ESR}$ Aging time for the C limit at  $T_a$ .  $ta_C$  $t_{ESR}^{\prime}\\t_{C}^{\prime}$ Lifetime limit at T' with ESR aging indicator. Lifetime limit at T' with C aging indicator. Time until failure with ESR aging indicator.  $t_{ESR}$ Time until failure with C aging indicator.  $t_C$ Boltzmann constant (8.617 times  $10^{-5}$  eV/°K). k $Ea_{ESR}$ Activation energy with ESR aging indicator.  $Ea_C$ Activation energy with C aging indicator.

$A_1$ ,  $B_1$ , E, and F are experimental parameters and also depend on the used capacitor.

From (10)–(13), the time until failure of the capacitor is given by the lower computed time between ESR lifetime limit and C lifetime limit, as shown in Fig. 11.

We have, for these works, different types of capacitors from four different manufacturers.

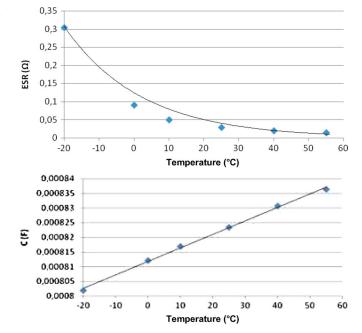

Fig. 12. Electric parameter variations versus temperature of one capacitor (1000  $\mu\mathrm{F}/450$  V).

All capacitors are first characterized versus temperature to determine the parameter-evolution laws versus temperature.

The parameters of (10) are determined by the nonlinear least square method of Levenberg–Marquardt which allows a very close approximation of the model.

For the example shown in Fig. 12, the method gives the following values for ESR:

$\alpha = 0.013055 \,\Omega$   $\beta = 0.75844 \,\Omega \,\gamma = 14.888386 \,^{\circ}\text{C}.$

Fig. 13. ESR evolution at 5 kHz and C evolution at 200 Hz for one capacitor (1000  $\mu$ F/450 V).

The parameters of (11) are determined in the same way as those identified in ESR. For the example shown in Fig. 12, we have the following values for C:

$$\chi = 0.000812 \,\text{F}$$

$\lambda = 4.600790 \,\text{times} \, 10^{-0.007} \,\text{F/}^{\circ}\text{C}.$

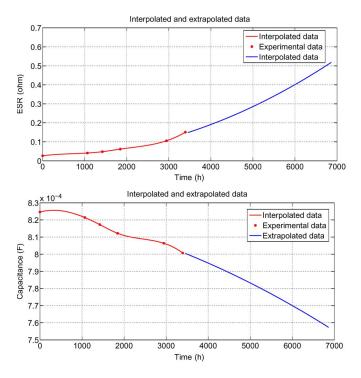

Some experimental results show the parameter evolutions of ESR and C after 3390 h of aging (about 5 mo) at 90 °C. Also, we use a Matlab algorithm to make a linear interpolation and extrapolation with the use of experimental data. This allows us to find the parameter-evolution laws and also the time until failure corresponding to the ESR and the capacitance C limit. The ESR and C variations versus temperature for a capacitor of  $1000~\mu\text{F}/450~\text{V}$  are shown in Fig. 12.

We show in Fig. 13 the interpolated and extrapolated data with the use of experimental measurements for ESR and C parameters of one capacitor (1000  $\mu$ F/450 V).

#### C. Experimental Study

1) Experimental Setup: To verify the validity of the proposed method, an experimental study was performed on a boost converter with a 50-V dc input, 470- $\mu$ F-450-V capacitor, an R load of  $100~\Omega$ , and a switching frequency that is fixed at 5 kHz. Therefore, a fixed-point DSP controller (TMS320F2812) was used for Il,~Uc,~Ic, and capacitor ripple voltage  $\Delta Uc$  acquisition measurements and switching operations required to perform the 200-V dc output voltage. To do that, we choose the two imbricated-loop principles, one fast current loop with a proportional/integrator controller to perform the current reference and another external voltage loop with a deadbeat controller to perform the 200-V dc output voltage. Moreover, a recursive least square algorithm (a particular case of Kalman

Fig. 14. FFT analysis of capacitor ripple voltage and capacitor voltage for a sampling frequency  $f_s=80\,\mathrm{kHz}$ .

filter) has been implemented to identify the two parameters ESR and  ${\cal C}.$

In literature [15], we know that using different cases of Kalman filter provides cutoff of the dc component of the input and output measurements, which are, respectively, capacitor current (recovered using the inductance current) and capacitor voltage. Therefore, the capacitor voltage and the inductance current are passed through a high-pass filter with cutoff frequency of around  $f_c=200~{\rm Hz}$  to suppress the dc component of the voltage measurements and without including phase shift. Consequently, we have only the capacitor ripple voltage which is in phase with the capacitor current.

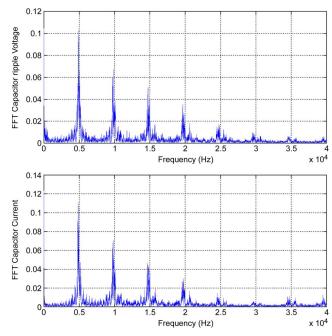

A fast Fourier transform (FFT) analysis respectively on the capacitor ripple voltage and capacitor current is shown in Fig. 14, and we see that the bandwidth of the system is about 40 kHz. Therefore, with respect to the Shannon theorem and to have a good ESR and C estimation, we choose a sampling frequency  $f_s=80~\mathrm{kHz}$ .

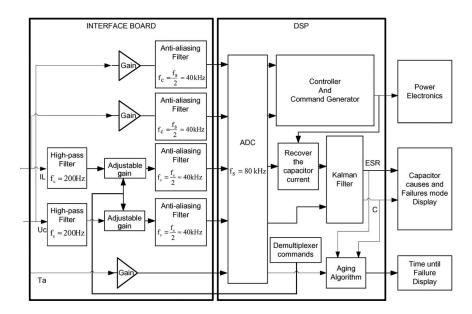

To eliminate signal distortion, an antialiasing filter [15] with a cutoff frequency  $f_c = (f_s/2) \approx 40$  kHz is used, as shown in the global capacitor condition monitoring scheme Fig. 15.

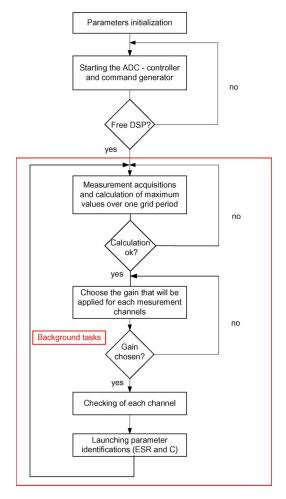

2) Adjusting Channels: The amplitudes of the measurements used to identify ESR and C are variable, depending on several parameters of the system in real time such as temperature, input voltage, and load applied to the power converter. To always have a full scale (3 V) on the DSP entrance for a good accuracy of identified parameters, we choose to apply a system to adjust automatically the amplitude of each measurement channel needed for identification. This system was performed by using a single eight-channel demultiplexer (M74HC4051) for each measure. Each demultiplexer was controlled independently by DSP to implement a variable gain. The gain choice is given by a well-defined algorithm shown in Fig. 16.

Fig. 15. Real-time electrolyte capacitor condition monitoring in UPS.

Fig. 16. Online gain choice algorithm.

This algorithm runs in real time and with less priority compared with the system regulation. The coding used to select the variable gain is optimized with minimizing loops (for, if, while, . . .) to have few DSP clock cycles used.

Fig. 17. Capacitor ripple voltage and capacitor current.

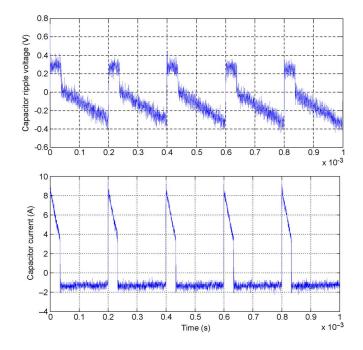

3) Experimental Results: The experimental measurements on the scope of capacitor ripple voltage and capacitor current (given by a current probe) are shown in Fig. 17.

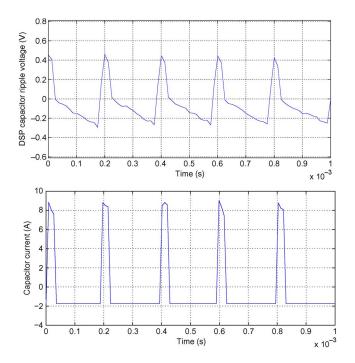

The corresponding numerical DSP measurements (after the analog-to-digital converter) of the capacitor ripple voltage and recovered capacitor current (9) are shown in Fig. 18.

The experimental results for the estimated parameters are summarized in Table II.

The least-squares algorithm implemented on DSP uses about 1 kB of a 16 bits word of DSP memory and takes about 2 s to converge and gives the ESR and C estimated values. This time is too small compared with the lifetime of a capacitor. Also, from experiments, a good and fast parameter identification is given by a decreasing forgetting factor. At every turn, the

Fig. 18. Capacitor ripple voltage and capacitor current recovered on DSP with a sampling frequency  $f_s=80~{\rm kHz}$ .

TABLE II

EXPERIMENTAL RESULTS FOR ESTIMATED PARAMETERS

| $ESR_{actual}$        | $ESR_{identified} = [ESR_{min}; ESR_{max}]$ | % error |

|-----------------------|---------------------------------------------|---------|

| $75.1~\text{m}\Omega$ | [71.3 m $\Omega$ ,78.8 m $\Omega$ ]         | +/-5    |

| $C_{actual}$          | $C_{identified} = [C_{min}; C_{max}]$       | % error |

| 472 μF                | [466 μF, 518 μF]                            | +/-10   |

algorithm starts with the last identified parameters of ESR and  ${\cal C}.$

It can be clearly seen that there is a nonsignificant error between the estimated and actual values of ESR and  ${\cal C}$ .

These results are consistent with the measured value using an impedance meter.

#### IV. CONCLUSION

Due to their large capacity and low cost, electrolytic capacitors, with the abilities of energy storage and voltage regulation, are used for almost all types of power-electronic system. Electrolytic capacitors, which are usually affected by wear-out faults, play a very important role for the quality and reliability of power-electronic system. Therefore, it is important to monitor the condition of an electrolytic capacitor in real time to predict the failure. A new method has been proposed to detect in real time the changes in the ESR and capacitance C values by taking into account the ambient temperature in order to create a real-time failure prediction of an electrolytic capacitor. For the proposed method, capacitor-current and capacitor ripple-voltage measurements using cheap and simple analog circuits are required. Simulation results and hardware experiments show that the proposed electrolytic-capacitor failureprediction technique can be applied to a power-electronic system successfully.

#### ACKNOWLEDGMENT

The authors would like to thank E. Brun, Emerging Technologies Director, for the support of the research.

#### REFERENCES

- Reliability Prediction of Electronic Equipment, Military Handbook 217 F, Feb. 28, 1995.

- [2] P. Venet, H. Darnand, and G. Grellet, "Detection of faults of filter capacitors in a converter. Application to predictive maintenance," in *Proc. Int. Telecommun. Energy Conf.*, 1993, pp. 229–234.

- [3] P. Venet, F. Perisse, M. H. El-Husseini, and G. Rojat, "Realization of a smart electrolytic capacitor circuit," *IEEE Ind. Appl. Mag.*, vol. 8, no. 1, pp. 16–20, Jan./Feb. 2002.

- [4] A. Lahyani, P. Venet, G. Grellet, and P. J. Viverge, "Failure prediction of electrolytic capacitors during operation of a switchmode power supply," *IEEE Trans. Power Electron.*, vol. 13, no. 6, pp. 1197–1207, Nov. 1998.

- [5] K. Harada, A. Katsuki, and M. Fujiwara, "Use of ESR for deterioration diagnosis of electrolytic capacitor," *IEEE Trans. Power Electron.*, vol. 8, no. 4, pp. 355–361, Oct. 1993.

- [6] A. M. Imam, T. G. Habetler, R. G. Harley, and D. M. Divan, "Condition monitoring of electrolytic capacitor in power electronic circuits using adaptive filter modeling," in *Proc. IEEE PESC*, Sep. 2005, pp. 601–607.

- [7] E. Aeloiza, J. H. Kim, P. Enjeti, and P. Ruminot, "A real time method to estimate electrolytic capacitor condition in PWM adjustable speed drives and uninterruptible power supplies," in *Proc. IEEE PESC*, 2005, pp. 2867–2872.

- [8] A. M. Imam, T. G. Habetler, R. G. Harley, and D. M. Divan, "Real-time condition monitoring of the electrolytic capacitors for power electronics applications," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2007, pp. 1057–1061.

- [9] M. L. Gasperi, "Life prediction modeling of bus capacitors in ac variable-frequency drives," *IEEE Trans. Ind. Appl.*, vol. 41, no. 6, pp. 1430–1435, Nov./Dec. 2005.

- [10] V. A. Sankaran, F. L. Rees, and C. S. Avant, "Electrolytic capacitor life testing and prediction," in *Conf. Rec. IEEE IAS Annu. Meeting*, Oct. 1997, pp. 1058–1065.

- [11] O. Ondel, E. Boutleux, and P. Venet, "A decision system for electrolytic capacitors diagnosis," in *Proc. IEEE PESC*, Jun. 2004, pp. 4360–4364.

- [12] D. C. Lee, J. K. Seok, and J. W. Choi, "Online capacitance estimation of DC-link electrolytic capacitors for three-phase AC/DC/AC PWM converters using recursive least squares method," *Proc. Inst. Elect. Eng.—Elect. Power Appl.*, vol. 152, no. 6, pp. 1503–1508, Nov. 2005.

- [13] K. Myungchul, L. Kwangwoon, Y. Jangho, L. S. Bin, and Y. Jiyoon, "Condition monitoring of DC link electrolytic capacitors in adjustable speed drives," in *Conf. Rec. 42nd IEEE IAS Annu. Meeting*, Sep. 23–27, 2007, pp. 237–243.

- [14] F. Perisse, P. Venet, G. Rojat, and J. M. Retif, "Simple model of electrolytic capacitor taking into account the temperature and aging time," *Arch. Elektrotech.*, vol. 88, no. 2, pp. 89–95, Jan. 2006.

- [15] I. D. Landau and G. Zito, Digital Control Systems Design, Identification and Implementation. New York: Springer-Verlag, 2006.

- [16] J. Martinez-Vega, Matériaux diélectriques pour le génie électrique 2— Applications spécifiques. Paris, France: Hermes, 2007.

- [17] F. Perisse, "Etude et analyse des modes de défaillances des condensateurs électrolytiques a l'aluminium et des thyristors, appliquées au système de protection du LHC (Large Hadron Collider)," M.S. thesis, Claude Bernard Univ. Lyon France, 2003.

Karim Abdennadher (S'08) was born in Aix-en-Provence, France, on April 19, 1982. He received the Engineer degree from INSAT, Tunis, Tunisia, the M.S. degree from Claude Bernard University, Lyon, France, in 2006, and the Ph.D. degree in electrical engineering from Lyon 1 University, Villeurbanne, France, in 2010.

Currently, he is a Design Engineer with APC by Schneider Electric, Saint Ismier, France. His current research interests include static-inverter fault diagnostics and control, and modeling and aging of

components such as capacitors and batteries.

Pascal Venet (M'08) was born in Aix-Les-Bains, France, on March 16, 1965. He received the Ph.D. degree in electrical engineering from Lyon 1 University, Villeurbanne, France, in 1993.

Since 1995, he has been an Assistant Professor at Lyon 1 University. He has developed his research activity in the Electrical Engineering Laboratory (Laboratoire Ampère). His current research interests include static-converter fault diagnostics and aging of components such as electrolytic capacitors, supercapacitors, and batteries.

systems.

**Jean-Marie Rétif** received the Ph.D. degree in tuning control from Lyon 1 University, Villeurbanne, France, in 1979.

Since 1979, he has been working in electrical engineering control in the Laboratoire Ampère, Lyon 1 University, Villeurbanne, France, and has been with the Laboratory of Energetic and Control, INSA Lyon, where he deals with different subjects such as process control and optimization of solar heating. Currently, his interests are in the control of hybrid dynamic systems and applications concerning power

**Gérard Rojat** was born in Caraman, France, on May 6, 1946. He received the M.S. and Ph.D. degrees from the Université Paul Sabatier, Toulouse, France, in 1971 and 1974, respectively, and another Ph.D. degree in electrical engineering from Lyon 1 University, Villeurbanne, France.

He was an Assistant Professor at the Ecole Centrale de Lyon, Ecully, France, for 23 years. He is currently a Senior Professor at Lyon 1 University. He is the author or coauthor of more than 100 scientific papers.

**Christophe Rosset** (M'08) was born in Chambery, France, on April 4, 1963. He received the Engineer degree in control systems from the Conservatoire National des Arts et Métiers, Paris, France, in 1995.

Currently, he is a Senior Technical Expert with APC by Schneider Electric, Saint Ismier, France, working in core control for uninterruptible power supplies. Currently, he is involved in research on fault diagnostics of capacitors and batteries and also in electronic architecture of new uninterruptible-power-supply topology.