# Digital Sliding-Mode Controller For High-Frequency DC/DC SMPS

Shuibao Guo, Xuefang Lin-Shi, Bruno Allard, Yanxia Gao, Ruan Yi

# ► To cite this version:

Shuibao Guo, Xuefang Lin-Shi, Bruno Allard, Yanxia Gao, Ruan Yi. Digital Sliding-Mode Controller For High-Frequency DC/DC SMPS. IEEE Transactions on Power Electronics, 2010, 25 (5), pp.1120 - 1123. 10.1109/TPEL.2009.2039356 . hal-00519008

# HAL Id: hal-00519008 https://hal.science/hal-00519008v1

Submitted on 25 Mar 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Letters

# Digital Sliding-Mode Controller For High-Frequency DC/DC SMPS

Shuibao Guo, Xuefang Lin-Shi, Bruno Allard, Yanxia Gao, and Yi Ruan

*Abstract*—Digital control technique is becoming an attractive alternative for high-frequency switching mode power supply (SMPS). This paper introduces a fully synthesizable digital slidingmode (SM) controller for high-frequency dc/dc SMPS. The proposed SM controller is associated with a digital pulsewidth modulation (DPWM) block to operate at constant and high switching frequency compared to already published approaches. The digital SM controller is experimentally validated by means of fieldprogrammable gate array in a 4-MHz step-down converter with 10-bit analog-to-digital conversion (ADC) and 11-bit DPWM. Measured dynamic performances are superior to conventional digital controllers for dc/dc SMPS.

*Index Terms*—Digital controller, field-programmable-gatearray (FPGA) implementation, high-frequency switching-mode power supply (SMPS), sliding-mode (SM) control.

## I. INTRODUCTION

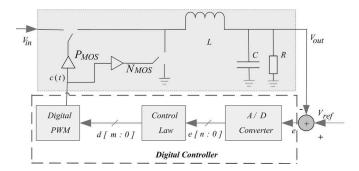

IGITAL control technique has recently become an attractive candidate in the design of high-frequency dc/dc switching-mode-power-supply (SMPS) applications [1]-[3]. A schematic diagram of a digital controller for compact SMPS application is shown in Fig. 1 . The digital controller includes three functionality blocks: analog-to-digital conversion (ADC), control law, and digital pulsewidth modulation (DPWM). Due to emerging windows ADC techniques [1]-[3] and efficient DPWM methods [1]-[5], the issues of high-speed low-power dedicated ADC and DPWM for digital controller have become less important. However, due to the cost/complexity constraints existing in low-power dc-dc converters, few investigations concern the development of high-performance control algorithms. Most existing digital controller for high-frequency (in megahertz range) and low-power (several watts) SMPS converters are designed using linear PID control in field-programmable gate array (FPGA) and application specific integrated circuits (ASIC) implementations [1], [3], [4]. Nevertheless, because of

Manuscript received June 30, 2009; revised October 13, 2009. Current version published May 7, 2010. Recommended for publication by Associate Editor B. Choi.

S. Guo is with Université de Lyon, AMPERE, INSA LYON, CNRS UMR5005, F69621, VILLEURBANNE, France, and also with the College of Mechatronics Engineering and Automation, Shanghai University, Shanghai 200072, China (e-mail: shuibao.guo@insa-lyon.fr).

X. Lin-Shi and B. Allard are with Université de Lyon, AMPERE, INSA LYON, CNRS UMR5005, F69621, VILLEURBANNE, France (e-mail: xuefang.shi@insa-lyon.fr; bruno.allard@insa-lyon.fr).

Y. Gao and Y. Ruan are with the College of Mechatronics Engineering and Automation, Shanghai University, Shanghai 200072, China (e-mail: gaoyanxia@shu.edu.cn; yraun@shu.edu.cn).

Digital Object Identifier 10.1109/TPEL.2009.2039356

Fig. 1. Schematic of a digital controller for a step-down SMPS.

the nonlinearity characteristics of SMPS in nature, it is difficult for a linear PID algorithm to offer high dynamic performances over wide operating conditions and parameter range [6], [7].

As SMPS represents a particular class of variable structure systems (VSSs), nonlinear control methods, especially a slidingmode control (SMC) can enhance the dynamic performances of SMPS. Moreover, it is particularly suitable for high-frequency SMPS application as the control behavior approaches the ideal SMC with the increase in switching frequency [8]. To avoid the issue of variable switching frequency of the conventional hysteresis-modulation (HM) based SMC [9], recently an analog PWM-based SM controller has been proposed [10]. Unfortunately PWM-based analog SM controller shows limitations to control low-power high-frequency SMPS. Analog controllers are sensitive to analog component variations, and it is difficult to realize sophisticated control laws to improve the performances. By contrast, digital implementation overcomes the latter sensitiveness. Moreover, digital control enables to estimate signals in an indirect manner avoiding the use of critical sensors. Finally, advanced control laws may be implemented with a degree of reprogrammability. In [11], an FPGA implementation of a digital PWM-based SM controller is reported for a 23-kHz buck converter, where the DPWM adopts an 8-bit counter-comparator using a 6 MHz clock. With this design, a 1 GHz clock would be required for a converter operating at 4 MHz switching frequency, for example. The practical implementation for IC application with high switching frequency in megahertz range is then questionable. To our knowledge, the relevant experimental results of a SMPS with a digital SM controller operating at high-frequency (>1 MHz) have not yet been reported.

This paper proposes an original implementation of a PWMbased digital SM controller in FPGA for a step-down SMPS. The experimental validation comprises a discrete low-voltage buck converter operating at 4 MHz, a 10-bit discrete ADC and a 11-bit hybrid DPWM. An SM controller similar in complexity as a classical linear PID, but offering higher control performance, is presented in next section. The hybrid DPWM is presented in Section III.

## II. PROPOSED DPWM-BASED SMC

The control objective of a SMPS is to keep the output voltage  $V_o$  tracking the reference voltage  $V_{ref}$  with an acceptable ripple. Therefore, the sliding surface of the SM controller is chosen as [7]

$$S = K_1 (V_{\text{ref}} - V_o) + K_2 \frac{d}{dt} (V_{\text{ref}} - V_o) + K_3 \int (V_{\text{ref}} - V_o) dt \quad (1)$$

where  $K_1$ ,  $K_2$ , and  $K_3$  are control parameters of SMC. Considering the error-space phase plane  $((V_{ref} - V_o), \frac{d}{dt}(V_{ref} - V_o))$ , the system dynamics can be written as

$$\begin{cases} e_1 = V_{\text{ref}} - V_o \\ \dot{e}_1 = e_2 \\ \dot{e}_2 = -\frac{1}{LC}e_1 - \frac{1}{RC}e_2 - \frac{V_{\text{in}}}{LC}u + \frac{V_{\text{ref}}}{LC} \end{cases}$$

(2)

with R the load, L the inductance, C the capacitor, u the control signal of switch, and  $V_{in}$  the input voltage.

With the equivalent control [12], the sliding-mode (SM) input u can be determined using the invariance conditions by setting S = 0 and  $\dot{S} = 0$  [8]

$$u = \frac{1}{V_{\text{in}}} \left[ V_{\text{ref}} + LC \left( \frac{K_1}{K_2} - \frac{1}{RC} \right) e_2 + LC \left( \frac{K_3}{K_2} - \frac{1}{LC} \right) e_1 \right].$$

(3)

From (3), it can be seen that the SM controller involves the time differentiation of output voltage:  $e_2 = -dV_o/dt = -i_C/C$ , which results in the need of measurement for capacitor current  $i_C$ , and thus, increases the cost of the digital controller. Here, a simple numeric derivation is adopted to eliminate the need of hardware measurement

$$e_2 = -\frac{dV_o}{dt} = -\frac{V_o(n) - V_o(n-1)}{T_s}$$

(4)

where  $V_o(n)$  and  $V_o(n-1)$  are the output voltages in the *n*th and the (n-1)th cycle, respectively. Therefore, the proposed DPWM-based SM controller can be obtained as follows:

$$d = \frac{1}{V_{\text{in}}} \left[ V_{\text{ref}} - LC \left( \frac{K_1}{K_2} - \frac{1}{RC} \right) \frac{V_o(n) - V_o(n-1)}{T_s} \right] + \frac{1}{V_{\text{in}}} \left[ LC \left( \frac{K_3}{K_2} - \frac{1}{LC} \right) (V_{\text{ref}} - V_o) \right].$$

(5)

This control algorithm is not more complex than a classical PID one and easy to implement in a FPGA or ASIC as it requires only few memories, multipliers, and adders.

To achieve the design specifications, the SMC must maintain the variable state trajectory on the sliding surface for all subsequent time. It is then necessary to ensure the existence conditions for a sliding surface. This task is performed using the Lyapunov's second method, where the Lyapunov's function is generally defined as  $V = (1/2)S^2$ . The following existence condition must be satisfied:

$$SS < 0. \tag{6}$$

Rewriting (1) in Laplace form as

$$K_1e_1(s) + K_2se_1(s) + K_3e_1(s)\frac{1}{s} = 0$$

<sup>(7)</sup>

the convergence dynamics can be chosen as a standard secondorder system form to ensure the SMC system stability.

### III. 11-BIT HYBRID DPWM DESIGN

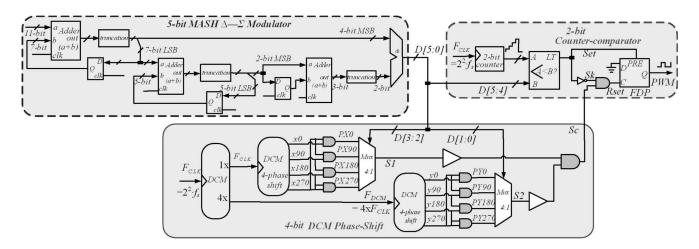

The digital PWM-based SM controller requires a DPWM to do the digital-to-time conversion (DTC) to drive the transistors. This paper proposes an hybrid DPWM comprising a  $\Delta$ - $\Sigma$ block, a digital clock module phase-shift block (DCM) and a counter-comparator block. By comparison, Norris et al. [13] detail a pure  $\Delta -\Sigma$  PWM (soft DPWM) and Batarseh *et al.* [5] describe a pure DCM (hardware) DPWM. The experimental testbench includes an 11-bit FPGA-based DPWM with a 5-bit  $\Delta$ - $\Sigma$  block, a 4-bit segmented DCM phase-shift block, and a 2-bit counter comparator (see Fig. 2). Consequently, for operation at switching frequency  $f_s$ , the counter-comparator block only needs a  $2^2 \cdot f_s$  clock. It dramatically alleviates the high clock-frequency requirement. For instance, when DPWM operates at  $f_s = 4$  MHz, the proposed hybrid DPWM only needs a 16 MHz system clock. In contrast, the pure digital  $\Delta$ - $\Sigma$  DPWM in [13] needs a second-order loop filter, which is potentially less stable than the cascade of two first-order filters proposed here, and the segmented DCM phase shift in [5] would require a system clock of 1 GHz to achieve the 4 MHz switching frequency.

#### **IV. EXPERIMENTAL RESULTS**

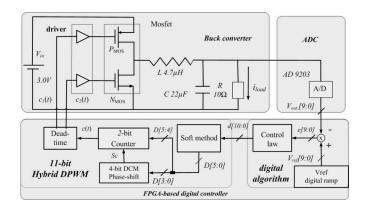

The functionality of the proposed DPWM-based SMC is experimentally verified using a discrete buck converter with 3.0 V input and 1.5 V output voltage. A 10-bit discrete ADC (AD9203) is used in order to avoid limit-cycle oscillation [4]. The implementation of the proposed DPWM-based SM controller is performed on a Xilinx XC2VP30 FPGA with an external 16 MHz system clock. A very-high-speed-integrated-circuit Hardware Description Language (VHDL) design approach is used to synthetize the SM controller with Xilinx ISE development software. The test platform and its block diagram are shown in Figs. 3 and 4, respectively. The parameters of the SMPS are listed in Table I. The tests are currently performed up to 4 MHz due to frequency limits of the discrete SMPS.

The sliding-control parameters are determined by considering the second-order system stability condition and desired behavior. After simulation studies, the damming ratio  $\zeta$  is set to 1 and undumped natural frequency is set to 1/15th of the switching frequency. A classical but optimal PID algorithm is considered for the sake of performance comparison with the proposed SM

Fig. 2. Proposed 11-bit FPGA-based hybrid DPWM: 5-bit  $\Delta - \Sigma$  modulator, 4-bit segmented DCM phase-shift and 2-bit counter comparator.

Fig. 3. Experimental test platform.

Fig. 4. Experimental test platform block diagram.

controller. The PID controller parameters are calculated so that the closed-loop dynamics corresponds to a second-order system with a resonant frequency,  $\omega$ , of 20 times the open-loop pulsation and a damping ratio,  $\zeta = 0.7$ . The PID discrete-time form

| TABLE I<br>Parameters of the Digitally Controlled SMPS |                                |                      |

|--------------------------------------------------------|--------------------------------|----------------------|

| Buck                                                   | Switching power converter      | Step down            |

| R                                                      | Load                           | $10\Omega$           |

| L                                                      | Inductor of power filter       | $4.7 \mu H$          |

| C                                                      | Capacitor of power filter      | $22\mu F$            |

| $V_{in}$                                               | Input voltage                  | 3.0V                 |

| $V_{ref}$                                              | Reference voltage              | 1.5V                 |

| $f_s$                                                  | Switching frequency            | 4MHz                 |

| SMC                                                    | Digital control algorithm      | Sliding mode control |

| ADC                                                    | AD9203                         | 10-bit               |

| DPWM                                                   | Hybrid DWPM                    | 11-bit               |

| $N_{Core}$                                             | Counter comparator resolution  | 2-bit                |

| $N_{DCM}$                                              | DCM phase-shift resolution     | 4-bit                |

| $N_{\Delta-\Sigma}$                                    | $\Delta$ - $\Sigma$ resolution | 5-bit                |

| $F_{CLK}$                                              | DPWM counter frequency         | 16MHz                |

TABLEI

comes as

$$d[n] = a_1 d[n-1] + a_2 d[n-2] + b_0 e[n] + b_1 e[n-1] + b_2 e[n-2]$$

(8)

where  $b_0 = 63.0649$ ,  $b_1 = -125.4422$ ,  $b_2 = 62.4044$ ,  $a_1 = -0.7792$ , and  $a_2 = -1.7792$ .

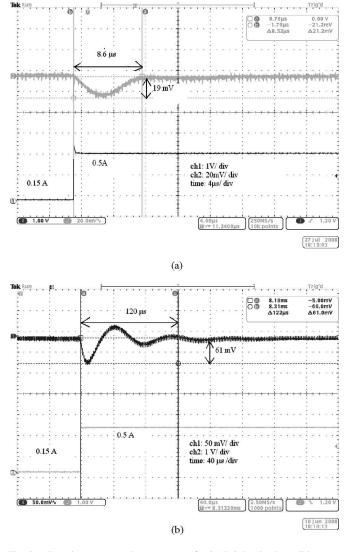

Fig. 5 shows the transient output voltage response of SM controller and PID controller for transient load from 0.15 to 0.5 A (10  $\Omega \rightarrow 3 \Omega$ ). These results show that the dynamic response of SMC is very fast (<8.6  $\mu$ s) and the offset on the output voltage is also very small (<19 mV or 1.3%). Clearly, the proposed DPWM-based SM controller offers better disturbance rejection and faster speed of response than a classical PID.

Fig. 5. Transient output voltage response for 0.15–0.5 A load conditions: (a) SM controller, (b) PID controller.

## V. CONCLUSION

This paper presents a fully synthesizable DPWM-based digital SMC for low-power (some watts) and high-frequency (in megahertz and over) SMPS. The architecture contains a PWMbased SMC algorithm and an efficient hybrid DPWM. The proposed nonlinear SMC achieves a constant high switching frequency. Its hardware implementation is quite simple: only few memories, multipliers, and adders in FPGA/ASIC are needed. The hybrid DPWM combines a 5-bit  $\Delta$ - $\Sigma$  noiseshaping modulator with a 2-bit counter-comparator block. Instead of  $2^{11} f_s$ , the hybrid 11-bit DPWM architecture merely requires  $2^2 f_s$  clock. It dramatically reduces the power consumption. The FPGA implementation is tested on a lab-scale buck converter (step-down SMPS) where the switching frequency is limited to 4 MHz. The experimental results validate the functionality of the proposed PWM-based digital SMC controller.

## REFERENCES

- B. Patella, A. Prodić, A. Zirger, and D. Maksimović, "High-frequency digital PWM controller IC for DC-DC converters," *IEEE Trans. Power Electron.*, vol. 18, no. 1, pp. 438–446, Jan. 2003.

- [2] J. Xiao, A. Peterchev, J. Zhang, and S. Sanders, "An ultra-low-power digitally-controlled buck converter IC for cellular phone applications," in *Proc. 19th Annu. IEEE Appl. Power Electron. Conf. Expo. (APEC 2004)*, vol. 1, pp. 383–391.

- [3] Z. Lukić, N. Rahman, and A. Prodić, "Multibit Δ–Σ PWM digital controller IC for DC–DC converters operating at switching frequencies beyond 10 MHz," *IEEE Trans. Power Electron.*, vol. 22, no. 5, pp. 1693– 1707, Sep. 2007.

- [4] A. Peterchev and S. Sanders, "Quantization resolution and limit cycling in digitally controlled PWM converters," *IEEE Trans. Power Electron.*, vol. 18, no. 1, pp. 301–308, Jan. 2003.

- [5] M. Batarseh, W. Al Hoor, L. Huang, C. Iannello, and I. Batarseh, "Segmented digital clock manager-FPGA based digital pulse width modulator technique," in *Proc. 39th IEEE Annu. Power Electron. Spec. Conf. (PESC* 2008), Jun., pp. 3036–3042.

- [6] C. Coleman and D. Godbole, "A comparison of robustness: Fuzzy logic, PID, and sliding mode control," in *Proc. 3rd IEEE Conf. World Congr. Comput. Intell.*, Jun. 1994, vol. 3, pp. 1654–1659.

- [7] S. Tan, Y. Lai, and C. Tse, "General design issues of sliding-mode controllers in DC–DC converters," *IEEE Trans. Ind. Electron.*, vol. 55, no. 3, pp. 1160–1174, Mar. 2008.

- [8] V. Utkin, Sliding Mode and Their Applications in Variable Structure Systems. Moscow, Russia: Mir, 1978.

- [9] M. Castilla, L. Vicuna, M. Lopez, O. Lopez, and J. Matas, "On the design of sliding mode control schemes for quantum resonant converters," *IEEE Trans. Power Electron.*, vol. 15, no. 6, pp. 960–973, Nov. 2000.

- [10] S. Tan, Y. Lai, and C. Tse, "Indirect sliding mode control of power converters via double integral sliding surface," *IEEE Trans. Power Electron.*, vol. 23, no. 2, pp. 600–611, Mar. 2008.

- [11] R. Ramos, D. Biel, E. Fossas, and F. Guinjoan, "A fixed-frequency quasisliding control algorithm: Application to power inverters design by means of FPGA implementation," *IEEE Trans. Power Electron.*, vol. 18, no. 1, pp. 344–355, Jan. 2003.

- [12] J. Ackermann and V. Utkin, "Sliding mode control design based on Ackermann's formula," *IEEE Trans. Autom. Control*, vol. 43, no. 2, pp. 234–237, Jun. 1998.

- [13] M. Norris, L. Marco, P. E. Alarcon, and D. Maksimovic, "Quantization noise shaping in digital PWM converters," in *Proc. 39th IEEE Annu. Power Electron. Spec. Conf. (PESC 2008)*, Jun., pp. 127–133.