## Fabrication of amorphous silicon nanoribbons by atomic force microscope tip induced local oxidation for thin film device applications

Laurent Pichon, Regis Rogel, Fouad Demami

### ► To cite this version:

Laurent Pichon, Regis Rogel, Fouad Demami. Fabrication of amorphous silicon nanoribbons by atomic force microscope tip induced local oxidation for thin film device applications. Semiconductor Science & Technology, 2010, 25, pp.065001. 10.1088/0268-1242/25/6/065001. hal-00486628

## HAL Id: hal-00486628 https://hal.science/hal-00486628

Submitted on 26 May 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Fabrication of amorphous silicon nanoribbons by atomic force microscope tip induced local oxidation for thin film device applications

L. Pichon, R. Rogel, F. Demami

Groupe Microélectronique, IETR, UMR CNRS 6164, campus de beaulieu, 262 avenue du général Leclerc, 35042 Rennes cedex, France.

#### Abstract

We demonstrate the feasibility of induced local oxidation of amorphous silicon by atomic force microscopy. The resulting local oxide is used as mask for the elaboration of thin film silicon resistor. A thin amorphous silicon layer deposited on a glass substrate is locally oxidized following narrow continuous lines. The corresponding oxide line is then used as mask during plasma etching of the amorphous layer leading to the formation of nanoribbon. Such amorphous silicon nanoribbon is used for the fabrication of resistor.

#### **1. Introduction**

Owing to their physical and electrical properties silicon nano-objects represent promising elements with strong potential for a large variety of applications. They are currently attracting much attention as components for nanoelectronic devices in integrated silicon technology such as nanowire field effect transistors [1], photonic and optoelectronic devices [2], and chemical or biological sensors [3, 4]. For example, silicon nanowires are useful for the development of innovative electronic devices tanks to their specific properties as high surface to volume ratio, giant piezoresistivity, field emission, and synthesis compatible with large area technology. Silicon nano-objects development could significantly impact areas of electronics, genomics, biomedical diagnosis, drug discovery.... These silicon nano-objects can be prepared by the top-down approach, using various advanced methods such as e-beam [5], deep UV [6] lithography, and more particularly Atomic Force Microscopy (AFM) oxidation of silicon [7]. This latter technique could be used as direct write lithography for fabrication of electronic nano-devices.

Local anodic oxidation (LAO) of silicon surfaces by AFM is a promising method to fabricate nanometer scale oxide patterns due to its very precise control of the feature size. In this technique, a negative voltage is applied to the tip of the AFM system with respect to sample to induce local oxidation. This anodic oxidation (or surface anodisation) is described according to the electrochemical reaction of oxidizing ionic species OH<sup>-</sup> from ambient humidity with H-passivated crystalline silicon atoms at the surface of the substrate [8-10].

At first, the native oxide naturally existing on the surface is removed to passivate the silicon surface layer by metastable hydrogenated terminated surface. In this way, the Si-O bonds are substituted by weak Si-H bonds. Then, under a continuous negative bias of the tip, Si-H bonds break and anodisation reaction takes place. The resulting oxide feature depends on experimental conditions (tip bias, write speed, and ambient humidity). For example, previous work reported that electrically conducting AFM tip was used to oxidize regions narrow as 10–30 nm of H-passivated

Si (100) surface at write speeds up to 1  $\mu$ m/s [11]. In addition, reliability and resolution can be improved by using pulsed voltage instead of continuous polarization [12, 13]. However, in all cases the generated oxide is not as good as thermal oxide, but it can be used as an effective mask for pattern transfer, or as an insulating barrier in the case of very thin metallic or semi conductive film on insulator. With this approach, nanoelectronic devices have already been fabricated [7,14,15].

Most of previous works [7-22] reported tip induced local oxidation process on crystalline silicon substrate and some of them on masking process for fabrication of silicon nano-objects (nanowires or nanodots) by selective liquid anisotropic etching. Thus, owing to these observations, an original way consists to study i) the feasibility of AFM tip induced local oxidation of thin amorphous silicon (a-Si) layer, and ii) the ability of this oxide as mask for fabrication of thin film silicon objects by selective dry etching. Such patterning process compatible with the fabrication of thin silicon film based electronic devices has not been yet demonstrated.

#### 2. Technology and device fabrication

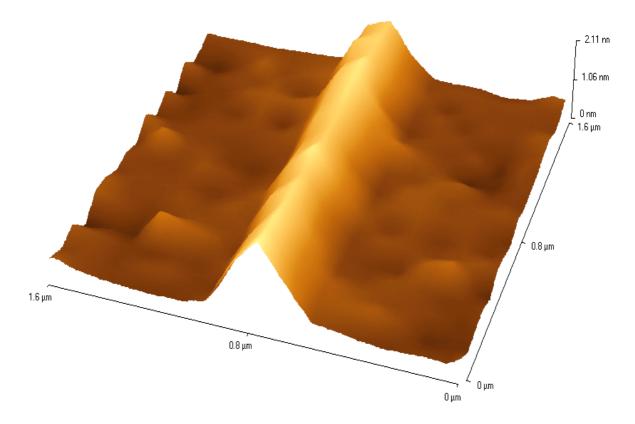

In this study our samples are processed on glass substrate and prepared in clean room under controlled ambient humidity (fixed at 45%). Tip induced local oxidation is performed by using a commercial AFM system (DI-CALIBER) from VEECO instruments company. First, a 250 nm thick  $SiO_2$  buffer layer is deposited by APCVD (Atmospheric Pressure Chemical Vapor Deposition) technique at 390°C on a glass substrate. Then, a 50 nm thick a-Si layer is deposited by LPCVD (Low Pressure CVD) technique at 550°C with a silane (SiH<sub>4</sub>) pressure of 90 Pa. The a-Si layer surface is hydrogen passivated into diluted hydrofluoric acid solution (HF-2%). In our case, such hydrogen passivation allows a local oxidation for at least 24 hours. LAO is carried out following continuous narrow lines. Continuous tip bias,  $V_{tip}$ , is fixed at -10V and the write speed, s, is 1µm/s. According to these conditions, about 2 nm height with 0.4 µm width oxide long line is

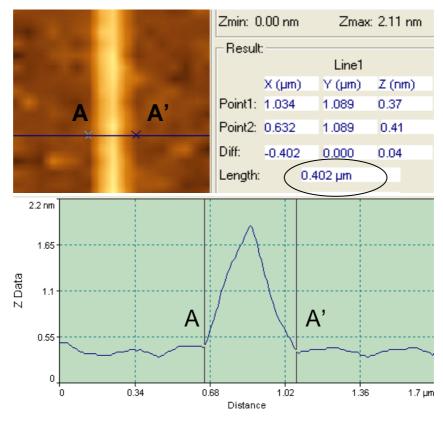

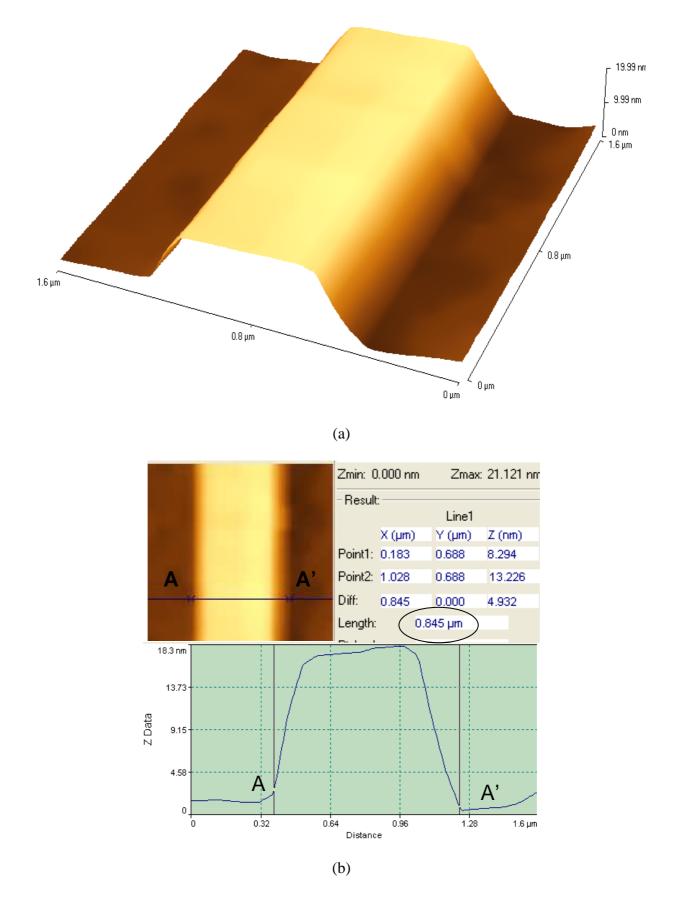

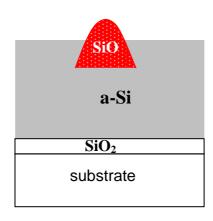

obtained as displayed in the figure 1. The oxide height is typical for local oxide elaborated with similar experimental conditions on crystalline silicon [7,9]. However, as already reported in a previous work [23], local oxidation of a-Si gives wider oxide line than for crystalline silicon. In addition, no significant change of the oxide feature was observed for -10 V < V<sub>tip</sub> < - 6 V, and for  $s < 1\mu m$ . Such oxide line was then used as mask during a Reactive Ion Etching (RIE) process with SF<sub>6</sub> plasma performed on our samples to etch and thus to pattern a-Si lines. The figure 2 shows the AFM picture of the sample displayed in the figure 1 after plasma etching of the 50 nm thick a-Si layer. The close to 20 nm height resulting a-Si nanoribbon indicates that i) the tip induced local oxide is totally etched by RIE using SF<sub>6</sub> plasma, and consequently that ii) the upper part of the underlying amorphous silicon layer is partially etched. For our process conditions, the SiO<sub>2</sub> versus a-Si etching rate selectivity is difficult to estimate because of the low oxide thickness. Nevertheless, this selectivity is high enough to highlights that tip induced local oxidation by AFM of amorphous silicon can be used as masking process for the fabrication of thin film a-Si objects. However, the width of the resulting nanoribbon is larger (0.8  $\mu$ m) than the oxide line width (0.4 µm) depicted in the figure 1. This result can be explained by the lateral effect of the field enhanced diffusion of the ionic oxygen species through the growing oxide [8] occurring in the upper part of the amorphous silicon layer. This phenomenon is more pronounced than for crystalline silicon due to the large defect density in the a-Si film. Since an a-Si film has a very large defect density, dangling bonds in the film easily react with oxygen to produce Si-O bonds resulting to a higher growth oxide rate than for crystalline silicon [24]. In addition, another reason involved in the width of the nanoribbon can be the size and the geometry of the tip. These two reasons can explain the formation of a wider buried oxide line that does not appear on the AFM observation (fig. 3 (a)). Consequently this oxide mask induces a wider a-Si pattern after plasma etching (fig. 3 (b)). Improvements in term of aspect ratio (height/width) of the local oxide feature, and therefore of the a-Si nanoribbon feature, could be possible by application of short pulses that restrict the lateral

diffusion of ionic species while a high-voltage pulse produces a fast growth rate in the vertical direction [13].

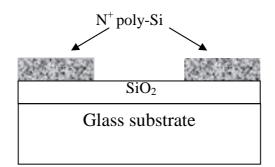

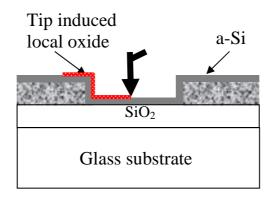

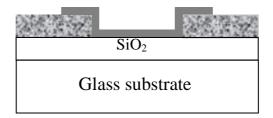

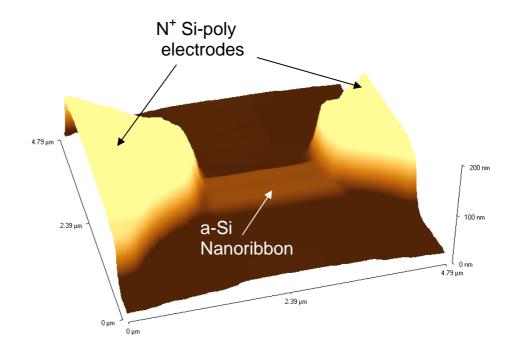

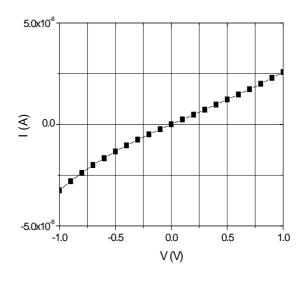

LAO is therefore used as masking process in order to pattern amorphous silicon for fabrication of thin film silicon resistor. First a 250 nm thick SiO<sub>2</sub> buffer layer is deposited by APCVD technique at 390°C on a glass substrate. Then, a 200 nm thick heavily *in-situ* phosphorus doped amorphous silicon layer is deposited by LPCVD technique at 550°C and 90Pa, and crystallized by a thermal annealing at 600°C under vacuum. The phosphorus concentration of this  $N^+$  type polysilicon ( $N^+$ Poly-Si) layer used as electrode material is  $2 \times 10^{20}$  cm<sup>-3</sup>. This layer is patterned by classical UV lithography and etched by RIE using  $SF_6$  plasma to define the device electrodes (fig. 4. (a)). Next, a 50 nm thick a-Si layer is deposited and locally oxidized, using conditions previously mentioned, following a continuous line between the two  $N^+$  Poly-Si pads (fig. 4 (b)). An amorphous silicon nanoribbon is then patterned according to the process previously described to interconnect electrodes to achieve electrical resistor (fig. 4 (c)). The 3D AFM pictures of the device represented in figures 5 (a) and (b) show a uniform and continuous 2  $\mu$ m long  $\times$  0.8  $\mu$ m width  $\times$  20 nm thick a-Si nanoribbon. I(V) characteristics of such resistor is measured at room temperature by a 4156 B semiconductor parameter analyzer. Results plotted in figure 5 (c) highlight an ohmic electrical connection at the a-Si nanoribbon/N<sup>+</sup> Poly-Si electrode interfaces. In addition, it clearly shows that LAO process operates continuously between the two differently levelled  $N^+$  Poly-Si pads. The estimated value of the corresponding resistor is  $40M\Omega$ .

#### **3.** Conclusion

Feasibility of LAO of amorphous silicon film by atomic force microscopy is shown to get a few micrometers long, uniform, and continuous oxide lines. The corresponding tip induced local oxide can be used as etch mask for elaboration of few nanometers thick film silicon patterns by selective dry etching. However, improvements are necessary to reduce the width of line-patterns in

particular for the fabrication of nanowires. This work is the first step towards the fabrication of thin film silicon nanodevices using AFM local oxidation of silicon as direct write lithography system.

#### References

- [1] Josh Goldberger, Allon I. Hochbaum, Rong Fan, and Peidong Yang, Nano Lett. **6(5)**, 973 (2006)

- [2] C. Yang, C. J. Barrelet, F. Capasso and C. M. Lieber, Nanoletters 6(12), 2929 (2006)

- [3] J. I. Hahm and C. M. lieber, Nanoletters 4(1), 51, (2004)

- [4] L.M. Lechuga, J. Tamayo, M. Alvarez, L.G. Carrascosa, A. Yufera, R. Doldan, E. Peralias, A.

- Rueda, J.A. Plaza, K. Zinoviev, C Dominguez, A. Zaballos, M. Moreno, C. Martinez-A, D.Wenn,

- N. Harris, C. Bringer, V. Bardinal, C. Vergnenegre, C. Fontaine, V. Diaz, A. Bernad, Sensors and Actuators **B 118**, 2 (2006)

- [5] Z. Li, Y. Chen, X. li, T.I. Kamins, K. Nauka, R. S. Williams, Nanoletters 4(2), 245 (2004)

- [6] L. Yang, D.H. Lee, H. Y. Chen, C. Y. Chang, S. D. Liu and C. C. Huang, VLSI Symp. Tech. Dig., 196 (2004)

- [7] I. Ionica, L. Montes, S. Ferraton, J. Zimmermann, L. Saminadayar, V. Bouchiat, Solid State Electronics **49**, 1497 (2005)

- [8] A. E. Gordon, R. T. Fayfield, D. D. Litfin, T. K. Higman, J. Vac. Sci. Technol. B 13, 2805 (1995)

- [9] P. Avouris, T. Hertel, R. Martel, Appl. Phys. Lett. 71, 285 (1997)

- [10] R. Garcia, R. V. Martinez, J. Martinez, Chem. Soc. Rev. 35, 29 (2006)

- [11] E. S. Snow, P. M. Campbell, Appl. Phys. Lett. 64, 1932 (1994)

- [12] B. Legrand, D. Stievenard, Appl. Phys. Lett. 74, 4049 (1999)

- [13] M. Calleja, R. Garcia, Appl. Phys. Lett. 76, 3427 (2000)

- [14] S. C. Minne, H. T. Soh, Ph. Flueckiger, C. F. Quate, Appl. Phys. Lett., 66, 703 (1995)

- [15] J. Martinez, R. V. Martinez, R. Garcia, Nano Lett. 8(11), 3636 (2008)

- [16] H. C. Day, D. R. Allee, Appl. Phys Lett. 62, 2691 (1993)

- [17] T. Hattori, Y. Ejiri , K. Saito, J. Vac. Sci. Technol. A 12, 2586 (1994)

- [18] H. Sugimura, T. Yamamoto, N. Nakagiri, M. Miyashita, T. Onuki, Appl. Phys. Lett. 65, 1569(1994)

- [19] T. Teuschler, K. Mahr, S. Miyazaki, M. Hundhausen, L. Ley, Appl. Phys. Lett. 66, 2499 (1995)

- [20] F. Perez-Murano, G. Adabal, N. Barniol, X. Aymerich, J. Servat, P. Gorostiza, F. Sanz, J.Appl. Phys. 78, 6797 (1995)

- [21] J. Servat, P. Gorostiza, F. Sanz, F. Perez-Murano, N. Barniol, G. Abadal, X. Aymerich, Vac.Sci. Technol. A 14, 1 (1996)

- [22] K. Morimoto, K. Araki, K. Yamashita, K. Morita, M. Niwa, Appl. Surf. Sci. 117, 652 (1997)

- [23] I. Umezu, T. Yoshida, K. Matsumoto, M. Inada, A. Sugimura, J of Non Cryst. Sol., 299-302, 1090 (2002)

- [24] G. Sarrabayrouse, P. Taurines, E. Scheid, D. Bielle-Daspet, A. Martinez, Thin Solid Films197, 21 (1991)

#### Figure captions

Figure 1: (a) AFM picture of oxide line obtained by AFM local oxidation of a-Si layer. (b) Maximum height of the oxide is 2 nm with an average width estimated at the surface is about 0.4  $\mu$ m.

Figure 2: (a) AFM picture of a-Si nanoribbon obtained after  $SF_6$  plasma etching of the sample represented in the figure 1. (b) The average nanoribbon height is about 20 nm with an average width estimated about 0.8  $\mu$ m.

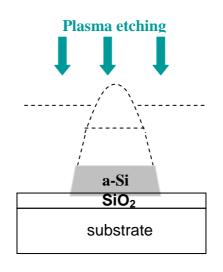

Figure 3: (a) Schematic illustration of a wider buried oxide due to the lateral effect of the field enhanced diffusion of ionic oxygen species through the growing oxide. (b): wider underlying a-Si pattern obtained after plasma etching using such oxide line mask.

Figure 4: Cross section view of the main technological steps of the a-Si nanoribbon resistor fabrication: (a)  $N^+$  poly-Si layer deposited on glass substrate and plasma etched to define electrodes contacts, (b) AFM tip induced local oxidation of a-Si layer, (c) plasma etching of a-Si layer (formation of the a-Si nanoribbon interconnecting the two  $N^+$  poly-Si electrodes).

Figure 5: (a) 3D AFM picture of a 2  $\mu$ m long  $\times$  0,8  $\mu$ m width  $\times$  20 nm thick a-Si nanoribbon resistor obtained by AFM local oxidation, (b) I(V) characteristics of the resistor.

(a)

Figure 1

Figure 2

(a)

(b)

Figure 3

(b)

Figure 4

Figure 5