## 80 GHz field-effect transistors produced using high purity semiconducting single-walled carbon nanotubes

L. Nougaret, H. Happy, Gilles Dambrine, Vincent Derycke, J.P. Bourgoin,

A.A. Green, M.C. Hersam

### ▶ To cite this version:

L. Nougaret, H. Happy, Gilles Dambrine, Vincent Derycke, J.P. Bourgoin, et al.. 80 GHz field-effect transistors produced using high purity semiconducting single-walled carbon nanotubes. Applied Physics Letters, 2009, 94 (24), pp.243505. 10.1063/1.3155212 . hal-00469685

### HAL Id: hal-00469685 https://hal.science/hal-00469685

Submitted on 31 May 2022  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## 80 GHz field-effect transistors produced using high purity semiconducting singlewalled carbon nanotubes

Cite as: Appl. Phys. Lett. **94**, 243505 (2009); https://doi.org/10.1063/1.3155212 Submitted: 31 March 2009 • Accepted: 20 May 2009 • Published Online: 17 June 2009

L. Nougaret, H. Happy, G. Dambrine, et al.

#### ARTICLES YOU MAY BE INTERESTED IN

High-frequency performance of scaled carbon nanotube array field-effect transistors Applied Physics Letters **101**, 053123 (2012); https://doi.org/10.1063/1.4742325

Intrinsic current gain cutoff frequency of 30GHz with carbon nanotube transistors Applied Physics Letters **90**, 233108 (2007); https://doi.org/10.1063/1.2743402

High-performance radio frequency transistors based on diameter-separated semiconducting carbon nanotubes Applied Physics Letters **108**, 233105 (2016); https://doi.org/10.1063/1.4953074

# Lock-in Amplifiers up to 600 MHz

Appl. Phys. Lett. **94**, 243505 (2009); https://doi.org/10.1063/1.3155212 © 2009 American Institute of Physics.

# 80 GHz field-effect transistors produced using high purity semiconducting single-walled carbon nanotubes

L. Nougaret, <sup>1</sup> H. Happy, <sup>1,a)</sup> G. Dambrine, <sup>1</sup> V. Derycke, <sup>2</sup> J. -P. Bourgoin, <sup>2</sup> A. A. Green, <sup>3</sup> and M. C. Hersam<sup>3</sup>

<sup>1</sup>Institut d'Electronique, de Microélectronique et de Nanotechnologie, UMR-CNRS 8520, BP 60069, Avenue Poincaré, 59652 Villeneuve d'Ascq Cedex, France

<sup>2</sup>Laboratoire d'Electronique Moléculaire, Service de Physique de l'Etat Condensé (CNRS URA 2464), CEA, IRAMIS, 91191 Gif sur Yvette, France

<sup>3</sup>Department of Materials Science and Engineering and Department of Chemistry, Northwestern University, Evanston 60208-3108, Illinois, USA

(Received 31 March 2009; accepted 20 May 2009; published online 17 June 2009)

This paper presents the high frequency performance of single-walled carbon nanotube (SWNT) field-effect transistors, with channel consisting of dense networks of high purity semiconducting SWNTs. Using SWNT samples containing 99% pure semiconducting SWNTs, we achieved operating frequencies above 80 GHz. This record frequency does not require aligned SWNTs, thus demonstrating the remarkable potential of random networks of sorted SWNTs for high frequency electronics. © 2009 American Institute of Physics. [DOI: 10.1063/1.3155212]

As a result of their excellent electrical and mechanical properties, semiconducting single-walled carbon nanotubes (SWNTs) are considered prime candidates for the "beyond complementary metal-oxide-semiconductor" era.<sup>1</sup> Using individual SWNTs as a device channel, logic devices and circuits such as field effect transistors<sup>2-4</sup> (FETs), complementary metal-oxide devices,<sup>5,6</sup> and ring oscillators<sup>7</sup> have been demonstrated. In the field of analog circuits, devices based on individual nanotubes face two major problems: the high input impedance of a SWNT and low drive currents in the on state. To circumvent these issues, devices based on an array of SWNTs as the channel are required.<sup>8-13</sup> However, all nanotube synthesis methods invariably produce a mixture of both metallic and semiconducting nanotubes. As a consequence, the performance of network-based devices<sup>8,9,14,15</sup> has been limited by the presence of metallic nanotubes.

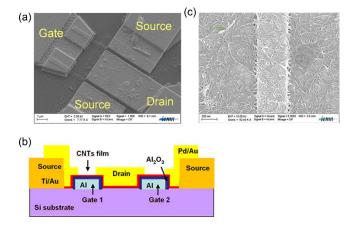

In this work, we demonstrate that high performance SWNT FETs can be produced using SWNT solutions consisting of 99% pure semiconducting nanotubes. These highly enriched nanotube dispersions produced using density gradient ultracentrifugation<sup>16</sup> are used to form a dense network of randomly oriented SWNTs. Briefly, the device structure [Figs. 1(a) and 1(b)] is similar to the one described in our previous work. The device is made on a high-resistivity silicon substrate. The device is a back gated transistor with a 2 nm thick aluminum oxide dielectric layer fabricated from a thin film of aluminum oxidized at low temperature. SWNTs were deposited on the gate area using a combination of surface chemistry<sup>17-19</sup> and dielectrophoresis (DEP). Because of the semiconducting nature of the SWNTs used, DEP does not induce alignment (in the range of the deposition frequencies used), in strong contrast with conventional SWNT solutions.<sup>14</sup> Figure 1(c) shows a randomly oriented SWNT network deposited on the gate electrode before source and drain contact formation. The final SWNT FET structure is a dual gate FET with gate length of 300 nm, and total width of 20  $\mu$ m (10  $\mu$ m per gate).

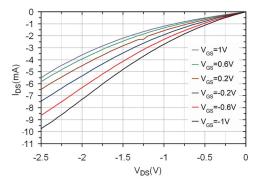

Direct current (dc) characterization (Fig. 2) shows high drain to source current ( $I_{\rm DS}$  up to -10 mA at  $V_{\rm GS}$ =-1 V in the best case) in good correlation with the high density of nanotubes in the device channel. The devices do not show pinch-off, most likely as a result of small numbers of metallic nanotubes in the channel, which may be preferentially deposited by DEP.<sup>20</sup> The maximum dc transconductance is close to 2.66 mS at  $V_{\rm DS}$ =-2.5 V, with the minimum dc conductance  $g_d$  close to 4 mS.

Considering our previous work on SWNT FET devices with unsorted nanotubes as the channel, we can define, at a given  $V_{\text{DS}}$  bias, a factor of merit as a ratio of the effective contribution of semiconducting nanotubes to the total dc current versus the associated gate control bias range,

$$f_{\rm Merit} = \frac{\Delta I_{\rm sc}}{\Delta V_{\rm GS}} = \frac{I_{\rm DS \ max} - I_{\rm DS \ min}}{\Delta V_{\rm GS}}.$$

This factor (which has the same units as transconductance) is related to the number of nanotubes per unit area and to the

FIG. 1. (Color online) SWNT FET schematic representation: (a) plan view, (b) cross-sectional representation, (c) scanning electron microscopy image of carbon nanotubes deposited on the gate electrode, before source and drain contacts deposition.

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: henri.happy@iemn.univ-lille1.fr.

FIG. 2. (Color online) Measured dc  $I_{\rm DS}$  vs  $V_{\rm DS}$  at different  $V_{\rm GS}$ .

ratio of semiconducting and metallic nanotubes. We report in Table I characteristics of three device types, each having the same structure at similar bias points.

In the first case (I),<sup>9</sup> a conventional SWNT solution with  $\sim 2/3$  of semiconducting nanotubes is used in combination with a surface chemistry selective deposition technique. In the second case (II),<sup>14</sup> DEP is employed in addition to selective deposition in order to increase the area density and alignment of nanotubes. Unfortunately, DEP strongly favors the deposition of metallic nanotubes. The contribution of metallic to the dc current is thus very high.

In the third case (III), a solution with 99% pure semiconducting nanotubes is used with the same combination of DEP and surface chemistry as in case (II). The influence of DEP during deposition is negligible.

One can observe that  $f_{\text{Merit}}$  increases as the area density of semiconducting nanotubes increases (case I to case II) and that the best value is obtained in case III where the density of semiconducting nanotubes is maximized. Even though the nanotubes are randomly oriented, a significant improvement of dc performance is obtained. In the following, we show how it impacts rf performance.

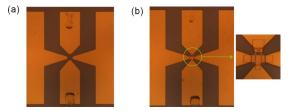

Microwave measurements were performed using an Agilent E8361A PNA series network analyzer from 100 MHz to 55 GHz. The measurement and de-embedding techniques are similar to those described in our previous work.<sup>14</sup> To calculate extrinsic parameters, the influence of coplanar accesses are removed from the *S* parameters measurements using specific structure illustrated in Fig. 3(a). These extrinsic param-

TABLE I. Characteristics of three device types. Case I corresponding to a FET where conventional SWNTs were deposited by selective surface chemistry. Case II corresponding to a FET where conventional SWNTs were deposited by DEP. Case III corresponding to a FET where 99% pure semiconducting SWNTs were deposited by DEP.

|                     | Case I                        | Case II                        | Case III                       |

|---------------------|-------------------------------|--------------------------------|--------------------------------|

|                     | $(V_{\rm DS}=1~{ m V})$       | $(V_{\rm DS} = 1.5 \ {\rm V})$ | $(V_{\rm DS} = 1.5 \ {\rm V})$ |

|                     | 1.53 mA                       | 21 mA                          | 5.0 mA                         |

| I <sub>DS max</sub> | $(V_{\rm GS} = -2 \ {\rm V})$ | $(V_{\rm GS} = -2 \ {\rm V})$  | $(V_{GS}=-1 V)$                |

|                     | 0.8 mA                        | 20 mA                          | 2 mA                           |

| I <sub>DS min</sub> | $(V_{\rm GS}=2~{\rm V})$      | $(V_{\rm GS}=0~{\rm V})$       | $(V_{\rm GS}=1~{\rm V})$       |

| $\Delta V_{GS}$     | 4 V                           | 2 V                            | 2 V                            |

| f <sub>Merit</sub>  | 0.18                          | 0.5                            | 1.5                            |

| $g_m$ (dc)          | 220 µS                        | 500 µS                         | 1.6 mS                         |

| $g_d$ (dc)          | 0.8 mS                        | 15 mS                          | 4 mS                           |

| $g_m/g_d$           | 0.275                         | 0.03                           | 0.4                            |

FIG. 3. (Color online) Structures used for de-embedding. (a) Structure used to extract extrinsic performance. (b) Structure used to extract intrinsic performance.

eters are considered as the actual high frequency characteristics.

To calculate intrinsic parameters, an "open" test structure is used [Fig. 3(b)] for de-embedding. This open structure is strictly identical to the active structure with CNTs except that no nanotube is deposited in the gate area. So every parasitic parameters close to the gate-electrode regions (fringing capacitances, gate-drain and gate-source overlap capacitances, etc.) are removed. With this technique, contact resistance between accesses (source and drain) and array of nanotubes are not removed. It should be noted that test structures, which are passive, are fabricated on the same wafer as active structures (SWNT FETs).

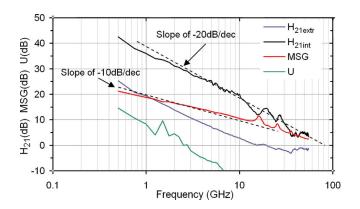

The current gain  $(H_{21})$ , the unilateral gain (U) and the maximum stable gain (MSG) characteristics obtained from this de-embedding procedure are plotted in Fig. 4.  $H_{21}$  and MSG curves present -20 and -10 dB/decade slopes, respectively, in agreement with theory. The extrinsic and intrinsic current gain cutoff frequencies  $(f_{t_{ext}} \text{ and } f_{t_{int}})$  are  $\sim 15$  and  $\sim 80$  GHz, respectively (Fig. 4). The unilateral gain, deduced from S parameters shows the maximum frequency of oscillation  $f_{max}=3$  GHz, which is smaller than  $f_t$ . This limitation is due to some parasitics such as the gate resistance, contact resistance, etc.

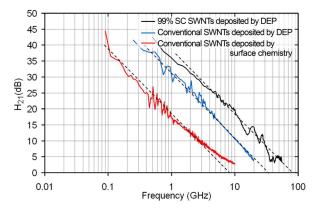

Considering a device without parasitic losses,  $f_t$  is defined by  $f_t = g_m/2\pi C_{gs}$  so that improvement of  $g_m$  is directly reflected in  $f_t$ . Figure 5 shows the comparison of current gain in our three device types. The improvement of cutoff frequency is related to the high density of semiconducting SWNTs in the channel. Indeed, in the case III, current is mainly due to the semiconducting tubes contrary to case II, where the density of metallic tubes is higher. As a consequence, the factor of merit of the new device is three times higher than the previous one (case II), even if the maximum

FIG. 4. (Color online) Current gain 10 log  $10(|H_{21}|^2)$ , MSG, U (in decibels), extracted from the S parameters. The dashed lines correspond to the ideal slopes of -20 dB/decade for  $|H_{21}|$  and -10 dB/decade for MSG.

FIG. 5. (Color online) Current gain 10 log  $10(|H_{21}|^2)$ , extracted from the *S* parameters for the three SWNT FET cases. The dashed lines correspond to the ideal slopes of -20 dB/decade for  $|H_{21}|$ . The respective  $f_t$  are: 8 GHz, 30 GHz and 80 GHz.

current is two times lower. The same improvement is obtained with  $f_t$ . These experimental results are in accordance with trends of simulation results.<sup>21</sup>

In summary, solutions of 99% pure semiconducting nanotubes were used to fabricate SWNT FETs for rf analog applications. The device channel is composed of a high area density network of randomly oriented SWNTs. The dc characterization indicates improvement in terms of current level and ratio between semiconducting nanotube current versus metallic nanotube current. The high frequency characteristics also indicate significant improvement in terms of both extrinsic and intrinsic cutoff frequencies. The extrinsic and intrinsic current gain cutoff frequencies are  $\sim 15$  and  $\sim 80$  GHz, respectively. The maximum available gain is positive up to 3 GHz. Most importantly, this work shows that precise alignment of SWNTs is not required to achieve high frequency performance. This lifts a strong constraint in terms of fabrication processes, thus opening the route for realistic application of nanotubes in randomly oriented networks.

The authors thank N. Chimot for his help with nanotubes deposition. This work was partially supported by the ANR

project HF-CNT under the contract number ANR-05– NANO-055.

- <sup>1</sup>ITRS 2007, Emerging Research Material chapter.

- <sup>2</sup>S. J. Tans, A. R. M. Verschuren, and C. Dekker, Nature (London) **393**, 49 (1998).

- <sup>3</sup>R. Martel, T. Schmidt, H. R. Shea, T. Hertel, and P. Avouris, Appl. Phys. Lett. **73**, 2447 (1998).

- <sup>4</sup>R. Martel, V. Derycke, C. Lavoie, J. Appenzeller, K. Chan, J. Tersoff, and P. Avouris, Phys. Rev. Lett. 87, 256805 (2001).

- <sup>5</sup>A. Javey, Q. Wang, W. Kim, and H. Dai, Tech. Dig. Int. Electron Devices Meet. **2003**, 31.2.1–4.

- <sup>6</sup>C. Chen, D. Xu, E. S.-W. Kong, and Y. Zhang, IEEE Electron Device Lett. **27**, 10 (2006).

- <sup>7</sup>Z. Chen, J. Appenzeller, Y.-M. Lin, J. Sippel-Aokley, A. G. Rinzler, J. Tang, S. J. Wind, P. M. Solomon, and P. Avouris, Science **311**, 1735 (2006).

- <sup>8</sup>S. Kim, T.-Y. Choi, L. Rabieirad, J.-H. Jeon, M. Shim, and S. Mohammadi, *IEEE International Microwave Symposium Digest* (IEEE, New York, 2005), p. 4.

- <sup>9</sup>J.-M. Bethoux, H. Happy, V. Derycke, G. Dambrine, M. Goffman, and J.-P. Bourgoin, IEEE Electron Device Lett. **27**, 681 (2006).

- <sup>10</sup>D. Wang, Z. Yu, S. McKernan, and P. J. Burke, IEEE Trans. Nanotechnol. 6, 400 (2007).

- <sup>11</sup>M. Engel, J. P. Small, M. Steiner, M. Freitag, A. A. Green, M. C. Hersam, and Ph. Avouris, ACS Nano 2, 2445 (2008).

- <sup>12</sup>M. C. LeMieux, M. Roberts, S. Barman, Y. W. Jin, J. M. Kim, and Z. Bao, Science **321**, 101 (2008).

- <sup>13</sup>Q. Cao, H.-S. Kim, N. Pimparkar, J. P. Kulkarni, C. Wang, M. Shim, K. Roy, M. A. Alam, and J. A. Rogers, Nature (London) **454**, 495 (2008).

- <sup>14</sup>A. Le Louarn, F. Kapche, J.-M. Bethoux, H. Happy, G. Dambrine, V. Derycke, P. Chenevier, N. Izard, M. F. Goffman, and J.-P. Bourgoin, Appl. Phys. Lett. **90**, 233108 (2007).

- <sup>15</sup>A. A. Pesetski, J. E. Baumgardner, S. V. Krishnaswamy, H. Zhang, J. D. Adam, C. Kocabas, T. Banks, and J. A. Rogers, Appl. Phys. Lett. **93**, 123506 (2008).

- <sup>16</sup>M. S. Arnold, A. A. Green, J. F. Hulvat, S. I. Stupp, and M. C. Hersam, Nat. Nanotechnol. 1, 60 (2006).

- <sup>17</sup>K. H. Choi, J.-P. Bourgoin, S. Auvray, D. Esteve, G. S. Duesberg, S. Roth, and M. Burghard, Surf. Sci. 462, 195 (2000).

- <sup>18</sup>E. Dujardin, V. Derycke, M. F. Goffman, R. Lefèvre, and J.-P. Bourgoin, Appl. Phys. Lett. **87**, 193107 (2005).

- <sup>19</sup>S. Auvray, V. Derycke, M. Goffman, A. Filoramo, O. Jost, and J.-P. Bourgoin, Nano Lett. 5, 451 (2005).

- <sup>20</sup>R. Krupke, F. Hennrich, H. V. Löhneysen, and M. Kappes, Science **301**, 344 (2003).

- <sup>21</sup>D. L. Pulfrey and L. Chen, Solid-State Electron. 52, 1324 (2008).