# Etude expérimentale de la balisticité du transport dans les transistors nMOS contraints sur silicium massif

Dominique Fleury, Grégory Bidal, Antoine Cros, Frédéric Boeuf, Thomas Skotnicki, Gérard Ghibaudo

## ▶ To cite this version:

Dominique Fleury, Grégory Bidal, Antoine Cros, Frédéric Boeuf, Thomas Skotnicki, et al.. Etude expérimentale de la balisticité du transport dans les transistors nMOS contraints sur silicium massif. Journées Nationales du GdR Nanoélectronique, May 2009, Orsay, France. pp.18-19. hal-00465797

HAL Id: hal-00465797

https://hal.science/hal-00465797

Submitted on 21 Mar 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Etude expérimentale de la balisticité du transport dans les transistors nMOS contraints sur silicium massif

D. Fleury<sup>1,2</sup>, G. Bidal<sup>1,2</sup>, A. Cros<sup>1</sup>, F. Boeuf<sup>1</sup>, T. Skotnicki<sup>1</sup> and G. Ghibaudo<sup>2</sup>

<sup>1</sup> STMicroelectronics, 850 rue Jean Monnet, 38926 Crolles, France

<sup>2</sup> IMEP-LAHC, 3 Parvis Louis Néel, 38016 Grenoble, France

## 1. Introduction

En dépit des défis technologiques à surmonter lors de la réduction d'échelle, la technologie sur silicium massif (bulk) reste attractive grâce son coût modéré. L'augmentation du dopage est un des leviers utilisés pour contrecarrer les effets de canaux courts. Si cette solution reste contraignante en termes de performances (car elle entraine une diminution de la mobilité et une augmentation de la variabilité), l'augmentation du taux de balisticité sur les petites longueurs de grille laisse entrevoir la perspective d'un fort courant  $I_{on}$ , peu dépendant de la mobilité. Cette vision semble attractive, mais la littérature porte peu d'attention à discriminer le phénomène de vitesse de saturation ( $v_{sat}$ ) du phénomène d'injection à la source  $(v_{ini})$ . Pourtant, chacun d'eux peut être LE mécanisme limitant  $I_{on}$ selon le flux de porteurs est limité par la capacité d'injection ou bien par les propriétés de transport du canal. Ce papier ce focalise sur la détermination de la vitesse limitant le transport en considérant les deux approches comme probables.

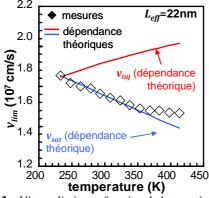

### 2. Concept de vitesse limite

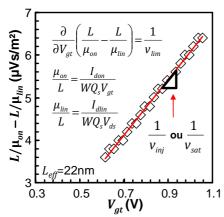

A l'équilibre thermique, les porteurs sont injectés depuis la source avec une vitesse thermique  $v_T$  prenant en compte la dégénérescence (1) [1]. La théorie quasi-balistique prévoit qu'une partie r de porteurs peut être rétrodiffusée vers la source tandis que la part (I - r) atteindra le drain sans interagir dans le canal [1,2]. Pour de forts champs électriques, l'interaction des électrons avec les phonons optiques provoque une non-linéarité de la loi d'Ohm. La vitesse de dérive des porteurs n'est plus linéairement proportionnelle au champ et sature à une vitesse de saturation  $v_{sat}$ . Ces deux mécanismes de limitation ne peuvent pas se produire en même temps et le phénomène le plus limitant régit la valeur maximum du courant de saturation. Dans le cas général, la vitesse limite peut s'écrire  $v_{lim} = \lim(v_{inj}, v_{sat})$  (9). Cette simple relation permet l'unification des mécanismes de transport sous la forme d'un modèl de courant général (8). Comme  $v_{sat}$  et  $v_{inj}$  ont des valeurs proches, l'identification du phénomène limitant peut être difficile. Heureusement, la dépendance en température de ces deux mécanismes est opposée [3,4] et une analyse de  $v_{lim}(T)$  peut révéler le phénomène de transport limitant. La valeur de  $v_{lim}$  est alors extraite comme sur la **Fig.1**.

## 3. Résultats expérimentaux

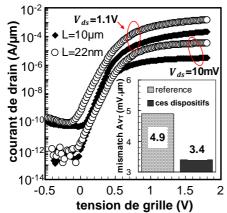

Des dispositifs nMOSFETS basés sur un procédé technologique de type 45nm LSTP, incluant un recuit laser, une couche tensile CESL 1.6Gpa et un substrat d'orientation (100)/<100> ont été utilisés pour effectuer nos mesures. L'extraction des paramètres a été effectuée sur des dispositifs  $W=1\mu m$  et des longueurs effective de canal  $L_{eff}$  (mesurées par méthode capacitive [5]) allant de  $10\mu m$  à 22nm (Fig.2). La tension de seuil ( $V_{th}$ ) et la mobilité ( $\mu$ ) ont été extraites grâce à la fonction  $\xi$  [6]. La résistance série de la technologie a été extraite en utilisant la technique  $R_{tot}(1/\beta)$  [7], et corrigée de manière a retrouver les propriétés de transport intrinsèque du canal. Des mesures statistiques ont été réalisées (66 puces) sur un wafer de 300mm de diamètre, à des températures comprises entre  $-40^{\circ}$ C et  $140^{\circ}$ C et deux tension de drain ( $V_{ds}=10$ mV et 1.1V). La tension  $V_{gt}=V_{gs}-1$

$V_{th}$  est fixée ( $V_{gt} = 1.1$ V) pour tous les dispositifs afin de conserver la même charge d'inversion. La vitesse thermique prenant en compte la dégénérescence pour cette charge est estimée à  $v_T \approx 2 \times 10^7$  cm/s, en accord avec [8].

### 4. Discussion

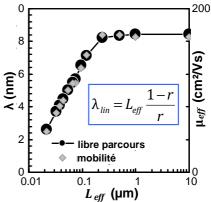

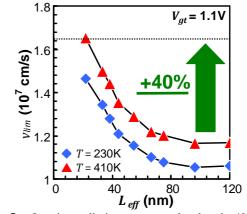

Bien que ne connaissant pas à priori la nature de  $v_{lim}$ , mais connaissant la valeur théorique de  $v_T$  il est possible d'extraire une vitesse d'injection et un taux de balisticité (BR) comme en [9,10]. Evidement, ces valeurs n'ont aucun sens physique si les hypothèses sur le transport ne sont pas confirmées mais elles permettent de comparer les présents résultats à ceux de la littérature. Le régime de saturation renvoie  $BR \sim 40\%$  ce qui aurait tendance à confirmer l'hypothèse d'un transport quasi-balistique, puisque le résultat est en ligne avec ceux de la littérature prônant cette hypothèse [10,11]. Néanmoins, le régime linéaire retourne les valeurs r = 96% et BR =7% ce qui semble inconsistant avec les résultats obtenus en régime de saturation. Nous proposons donc une nouvelle méthode permettant de déterminer la nature de  $v_{lim}$  en utilisant la dépendance en température sans présupposer de la nature du transport. La dérivée de la relation (8) donne directement  $v_{lim}$  (10), cf. Fig.1. En répétant la procédure d'extraction pour différentes températures, il est possible d'extraire l'évolution  $v_{lim}$  en fonction de la température  $v_{lim}(T)$ , et de la comparer avec les dépendances  $v_{sat}(T)$  et  $v_{inj}(T)$  de la littérature [3,4], Fig.3. La conclusion est claire : l'extraction  $v_{lim}(T)$  montre une dépendance en température similaire à celle observée dans [3] pour  $v_{sat}(T)$ . Ceci démontre que l'hypothèse de transport quasi-balistique (comme dans de nombreux papiers sur le sujet) est fausse. Pour aller plus loin dans notre investigation, l'extraction du libre parcours moyen (λ) en fonction de  $L_{\it eff}$  a été effectuée (cf. **Fig.4**).  $\lambda$  chute brutalement pour les petits  $L_{eff}$ , et atteint finalement la valeur de 2.6nm à  $L_{eff} = 22$ nm. Cette valeur est incompatible avec les taux de balisticité mesurés, démontrant que le transport dans les transistors bulk de 22nm reste toujours dominé par des phénomènes d'interaction dans le canal. Notre méthode peut également être utilisée pour extraire la variation de v<sub>sat</sub> en fonction de  $L_{eff}$  (Fig.5). L'augmentation 40% de  $v_{sat}$  reste pour l'instant inexpliquée mais pourrait provenir de la forte contrainte mécanique tensile sur les petits  $L_{eff}$ .

### 5. Conclusion

Nos mesures en température ont montré sans ambigüité que des mécanismes d'interaction dominent toujours le transport dans des transistors sur silicium massif de 22nm. Les taux apparents de balisticité extraits par les méthodes classiques sont largement surestimés et ne sont pas fondés physiquement, puisqu'ils résultent d'une utilisation inappropriée de  $v_{inj}$  au lieu de  $v_{sat}$  dans l'interprétation des résultats. Le point positif reste que même si le transport est limité par les interactions à fort champ, la vitesse limite semble augmenter pour les faibles longueurs de canal, laissant ainsi entrevoir des possibilités de performances accrues pour les prochains nœuds technologiques.

## Remerciements

Les auteurs remercient l'équipe *Process Integration* pour avoir fourni les transistors ici testés, ainsi que le Dr. R. Clerc pour ces précieux commentaires.

**Fig.1** – Extraction de la vitesse limite en utilisant le concept de mobilité apparente.  $v_{lim}$  est donnée par la pente comme défini en (10).

**Fig.2** – Performances des dispositifs en régime linéaire ( $V_{ds} = 10$ mV) et de saturation ( $V_{ds} = 1.1$ V). En insertion : mesure de variabilité.

**Fig.3** – Vitesse limite en fonction de la température. La dépendance met en évidence la présence de mécanismes de diffusion des porteurs dans le canal.

**Fig.4** – La décroissance du libre parcours moyen confirme la présence de mécanismes de diffusion des porteurs dans le canal.

**Fig.5** – La vitesse limite augmente de plus de 40% quand la longueur de canal est réduite à 22nm.

Tab.1 - Equations

| zworz zquarono                                                                                                                    |      |

|-----------------------------------------------------------------------------------------------------------------------------------|------|

| $v_T = \sqrt{\frac{2k_B T}{\pi m_t^*}} \left\{ \frac{F_{1/2}(\eta)}{\ln(1 + e^{\eta})} \right\},  \eta = \frac{E_F - E_C}{k_B T}$ | (1)  |

| $v_{inj} = v_T \times (1-r)/(1+r)$                                                                                                | (2)  |

| $I_{ddon} = W \frac{\mu_{dd} V_{gt}}{L} Q_s  (3)  I_{ddlin} = W \frac{\mu_{dd} V_{ds}}{L} Q_s$                                    | (4)  |

| $I_{balon} = Wv_{inj}Q_s  (5) I_{ballin} = Wv_{inj}Q_s \frac{qV_{ds}}{2k_BT}$                                                     | (6)  |

| $I_{sat} = W v_{sat} Q_s$                                                                                                         | (7)  |

| $1/I_d = 1/I_{dd} + 1/\min(I_{bal}, I_{sat})$                                                                                     | (8)  |

| $v_{lim} = \min(v_{sat}, v_{inj})$                                                                                                | (9)  |

| $\frac{\partial}{\partial V_{gt}} \left( \frac{L}{\mu_{on}} - \frac{L}{\mu_{lin}} \right) = \frac{1}{V_{lim}}$                    | (10) |

## Références

[1] M. Lundstrom, *EDL*, 18, 7, 1997. [2] M. Lundstrom, *TED*, 49, 1, 2002. [3] S.M. Sze « *Physics of semiconductor devices* », Wiley, 1987. [4] M. Zilli et al., *IEDM Tech. Dig.*, 2007. [5] D. Fleury et al., *T-SM*, 21, 4, 2008. [6] D. Fleury et al., *ICMTS*, 2008. [7] D. Fleury et al., *VLSI-TSA*, 2009. [8] V. Barral et al. *Symp. On VLSI Tech.*, 2007. [9] I. Pappas et al., *SSE*, 53, 2009. [10] A. Lochtefield et al., *EDL*, 22, 2, 2001. [11] M.-J. Chen et al., *IEDM* Tech. Dig., 2002.