# A New Technique to Extract the Gate Bias Dependent S/D Series Resistance of Sub-100nm MOSFETs

Dominique Fleury, Antoine Cros, Grégory Bidal, Hugues Brut, Emmanuel Josse, Gérard Ghibaudo

## ▶ To cite this version:

Dominique Fleury, Antoine Cros, Grégory Bidal, Hugues Brut, Emmanuel Josse, et al.. A New Technique to Extract the Gate Bias Dependent S/D Series Resistance of Sub-100nm MOSFETs. International Symposium on VLSI Technology, Systems and Applications, Apr 2009, Hsinchu, Taiwan. pp.109 - 110, 10.1109/VTSA.2009.5159314. hal-00465769

# HAL Id: hal-00465769 https://hal.science/hal-00465769

Submitted on 21 Mar 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## A New Technique to Extract the Gate Bias Dependent S/D Series Resistance of Sub-100nm MOSFETs

Dominique Fleury<sup>1,2</sup>, Antoine Cros<sup>1</sup>, Grégory Bidal<sup>1,2</sup>, Hugues Brut<sup>1</sup>, Emmanuel Josse<sup>1</sup> and Gérard Ghibaudo<sup>2</sup> <sup>1</sup> STMicroelectronics, 850 rue Jean Monnet 38926 Crolles cedex, France

<sup>2</sup> IMEP-LAHC, 3 rue Parvis Louis Néel BP 257 38016 Grenoble cedex 1 France

Tel. : +33-4-3892-3314, Fax : +33-4-3892-2953, email : dominique.fleury@st.com

## ABSTRACT

In this study, a new technique to extract the S/D series resistance (Rsd) from the total resistance versus transconductance gain plot  $R_{tot}(1/\beta)$  is proposed. The technique only requires the measurement of  $I_d(V_{gs})|_{Vgt}$  and  $\beta$ , allowing fast and statistical analysis in an industrial context. Unlike the usual Rtot(L)-based techniques, it has the advantage of being insensitive to the channel length and mobility variations and finally enables to extract very accurate values for Rsd(Vgs) and the effective mobility reduction factor  $\mu_{eff}(V_{gt})/\mu_{eff}(0)$ .

#### INTRODUCTION

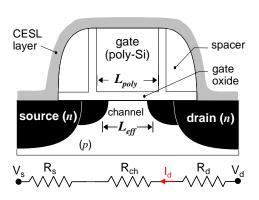

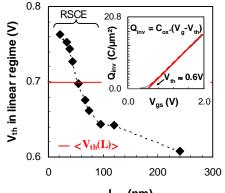

The S/D resistance (R<sub>sd</sub>) is a major concern for the MOSFET scaling as it plays a key role in device performance and power consumption [1]. Since the channel length is scaled down, the  $R_{sd}/R_{tot}$  ratio becomes higher and R<sub>sd</sub> requires improved accuracy in extraction techniques to be assessed within a reasonable error. As described on Fig.1, a transistor can be modeled in linear regime by a channel resistance R<sub>ch</sub> connected to the S/D series resistance  $R_{sd} = R_s + R_d$  through which the drain current  $I_d$  flows ( $R_{tot} = R_{sd} + R_{ch}$ ). Due to pockets implants, strain booster and neutral defects, the effective mobility  $(\mu_{eff})$  changes as a function of channel length (Leff) [2]-[4] (Fig.2). As a consequence, Rch is no more strictly proportional to the geometrical dimensions of the channel and all  $R_{tot}(L)$ -based techniques [5-7] fail when  $\mu_{eff}(L)$  variations are not properly compensated for [8] (cf. Fig.3). To solve this issue, a new extraction technique based on the relationship between R<sub>tot</sub> and the transconductance gain  $\beta$  of the transistor in linear regime is proposed. The technique is insensitive to the  $\mu_{eff}(L)$ ,  $L_{eff}(L)$  variations (which generally make the other techniques inaccurate) and provides a straightforward way to extract R<sub>sd</sub> statistically.

## The $R_{TOT}(1/\beta)$ technique

The  $R_{tot}(1/\beta)$  technique relies on the BSIM3v3 model (1) which reproduces the drain current behavior in linear regime. In (1),  $V_{gt} = (V_{gs})$  $- V_{th}$ ) is the gate overdrive,  $\beta = \mu_{eff}(0).C_{ox}.W_{eff}/L_{eff}$  is the transconductance gain (where  $\mu_{eff}(0)$  is the effective mobility extrapolated to  $V_{gt}$  = 0V) and  $(\Theta_1, \Theta_2)$  are the first and second order mobility attenuation factors, respectively.

$$I_{d} = \mu_{eff} C_{ox} \frac{W}{L} V_{gt} (V_{ds} - R_{sd} I_{d}) = \frac{\beta V_{ds} V_{gt}}{1 + \Theta_{1} V_{gt} + \Theta_{2} V_{gt}^{2}}$$

(1)

The channel resistance is defined as  $R_{ch} = V_{d,0}/I_{d,0}$  (where the "0" subscript refers to the intrinsic value of the parameter, for R<sub>sd</sub>=0  $\Omega.\mu m$ ). From (1),  $R_{tot}$  can be expressed as (2).

$$\mathbf{R}_{\text{tot}} = \frac{1}{\beta} \cdot \left( \frac{1 + \Theta_{1,0} \mathbf{V}_{\text{gt}} + \Theta_{2,0} \mathbf{V}_{\text{gt}}^2}{\mathbf{V}_{\text{gt}}} \right) + \mathbf{R}_{\text{sd}} \left( \mathbf{V}_{\text{gs}} \right)$$

(2)

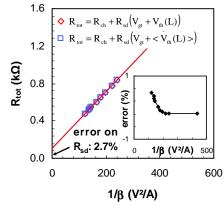

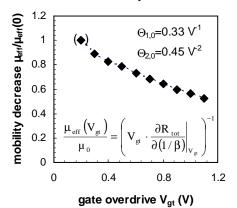

When V<sub>gt</sub> is fixed once for a full set of devices with several channel lengths, the  $R_{tot} = f(1/\beta)$  plot shows a linear behavior which returns the mobility reduction from the slope (3) and the  $R_{sd} \vert V_{gt}$  from the y-axis intercept (2). By repeating the same extraction for several gate overdrives,  $R_{sd}(V_{gs})$  and  $\mu_{eff}(V_{gt})/\mu_{eff}(0)$  can be extracted

$$\mathbf{V}_{gt} \cdot \frac{\partial \mathbf{R}_{tot}}{\partial (1/\beta)} \Big|_{\mathbf{V}_{gt}} = 1 + \Theta_{1,0} \mathbf{V}_{gt} + \Theta_{2,0} \cdot \mathbf{V}_{gt}^{2} = \frac{\mu_{eff}(0)}{\mu_{eff}(\mathbf{V}_{gt})}$$

(3)

## RESULTS

The following results were obtained by measurements on our 45nm node technology platform on the low stand-by power devices, featuring 1.7nm-EOT SiON gate dielectric with polysilicon gate and tensile contact etch stop layer for nMOS mobility optimization [9] (Fig.1). Extraction also been performed on FDSOI devices featuring metal gate (WN) with 2.5nm EOT HfSi<sub>x</sub>O<sub>y</sub>N<sub>z</sub> dielectric, 12nm thinned Si film and elevated S/D [10]. Statistical  $I_d(V_{gs})$  measurements (72 dices) have been performed for lengths ranging from 35nm to 240nm and W=1µm. Strong pockets implants have been used in the process to increase the channel doping and limit the short channel effect in the smallest devices.  $V_{th}$  and  $\beta$  can be extracted from the McLarty's function [11] (4) or from the  $\xi$ -function [12] which have both the advantage of being insensitive to  $(\Theta_1, \Theta_2)$  when  $R_{sd}$  has a linear variation with  $V_{gs}$ .

$$\left(\frac{\partial^2 \mathbf{R}_{tot}}{\partial \mathbf{V}_{gs}^{-2}}\right)^{-1/3} = \left(\frac{\beta}{2}\right)^{1/3} \mathbf{V}_{gt}$$

(4)

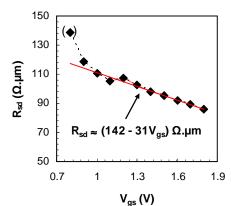

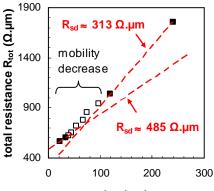

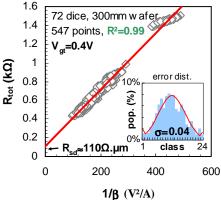

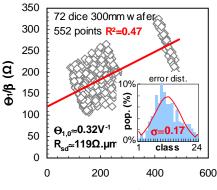

Note that, as displayed in the inset of Fig.4, V<sub>th</sub> deduced from McLarty's functions and  $\xi$ -function corresponds to the charge threshold voltage at strong inversion i.e. where  $Q_{inv} = C_{ox} V_{gt}$ .  $V_{th}(L_{eff})$  and  $\beta(L_{eff})$  behavior are displayed on Fig.4 and Fig.5, where  $L_{eff}$  has been extracted from C-V measurements [13]. Rtot has been measured for each device at several gate overdrive ranging from 0.1 to 1.1V (the nominal voltage for this technology is  $V_{gs} = 1.1$  V, i.e.  $V_{gt} \approx 0.4$ V).  $R_{sd}(V_{gt})$  has been extracted from the  $R_{tot}=f(1/\beta)$  plot, as described previously (2). The linear regression is displayed on Fig.5, where data has been filtered with a recursive normal filter within a  $\pm 3\sigma$ -tolerance (99% confidence). The points show a very good alignment which results in a very small error on the final result: R<sup>2</sup>>0.99,  $R_{sd} = (110 \pm 3) \Omega.\mu m$ . Fig.7 shows  $R_{sd}(V_{gs}),$  where  $V_{gs}$  has been approximated to  $V_{gs} \approx V_{gt} + \langle V_{th}(L) \rangle$ ,  $\langle V_{th}(L) \rangle$  being the average  $V_{th}$  for the set of devices:  $V_{gs} \approx V_{gt} + 0.69 \pm 0.05 \text{ V}$  (cf. Fig.4). The behavior of  $R_{sd}(V_g)$ is consistent with previous studies [14]. Results extracted for small gate overdrive ( $V_{gt} \leq 0.2V$ ) show a slight deviation, which might be due to the limited accuracy in the Vth-extraction technique and/or non validity of strong inversion approximation close to V<sub>th</sub>. Intrinsic mobility reduction factors have been extracted from (3) to be compared with the  $\Theta(\beta)$ technique [15],[16]. As shown on Fig.8 and Fig.9, both techniques provide very close  $\Theta_{1,0}$  values but  $R_{sd}$  extracted from  $\Theta(\beta)$  shows a larger dispersion mainly induced by uncertainties on the  $\Theta_1$  parameter extraction. Finally, error resulting from the  $\langle V_{th}(L) \rangle$  approximation has also been quantified (Fig10) and R<sub>sd</sub> has been estimated for the two extraction techniques. Results for bulk and FDSOI MOSFETs are summarized in Tab.1. As expected, FDSOI devices benefit from a lowered R<sub>sd</sub> thanks to the elevated epitaxial S/D and an improved accuracy is confirmed for the  $R_{tot}(1/\beta)$  technique compared to the  $\Theta(\beta)$  one.

### CONCLUSION AND PERSPECTIVES

This study demonstrates the ability of a new  $R_{tot}(1/\beta)$  technique to provide  $R_{sd}(V_g)$  and  $\mu_{eff}(V_{gt})/\mu_{eff}(0)$  values with an improved accuracy thanks to statistical results. Unlike the  $R_{tot}(L)$ -based technique, the use of  $1/\beta$  for the x-axis allows to correct any  $\mu_{eff}$  or  $L_{eff}$  variations. The technique only requires to measure  $I_d(V_{gs})|_{Vgt}$  and  $\beta$  on several channel lengths. The results match with the  $\Theta(\beta)$  technique which suffers from a larger dispersion and requires full Id(Vgs)-curves measurements to extract R<sub>sd</sub>. this technique is fully compatible with fast measurement techniques, offering new perspectives towards Rsd monitoring and large scale analysis in industrial environment.

### **ACKNOWLEDGMENTS**

The authors would like to thank the Advanced Modules and Process Integration teams for providing the devices used in this work.

Fig.1 – Typical bulk nMOSFET with tensile contact etch stop layer (CESL).

L<sub>eff</sub> (nm)

**Fig.4** –  $V_{th}(L_{eff})$  plot for nMOSFETs in linear regime, in inset: definition of V<sub>th</sub>.

**Fig.7** –  $R_{sd}(V_g)$  behaviour extracted from the  $R_{tot}(1/\beta)$  technique.

Fig.10 – Comparison between exact model (◊) and approximation ( $\Box$ ) using  $\langle V_{th}(L) \rangle$

## effective channel length Leff (nm)

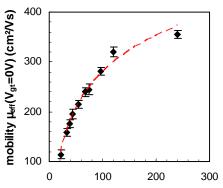

Fig.2 – decrease of the low field mobility for short channel length nMOSFETs

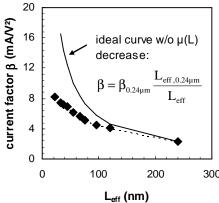

**Fig.5** –  $\beta$ (L<sub>eff</sub>) measurements. Continuous line: **Fig.6** – R<sub>tot</sub>(1/ $\beta$ ) plot for nMOSFETs. R<sub>sd</sub> is ideal behaviour w/o mobility reduction

Fig.8 – Mobility decrease (as a function of  $V_{gs}$ ) from the  $R_{tot}(1/\beta)$  technique.

| R <sub>sd</sub> (Ω.µm) | R <sub>tot</sub> (1/β <b>)</b> | Θ(β)     |

|------------------------|--------------------------------|----------|

| nMOS bulk              | 110 ± 3                        | 119 ± 10 |

| pMOS bulk              | 170 ± 5                        | 155 ± 15 |

| nMOS FDSOI             | 97 ± 5                         | 126 ± 34 |

| pMOS FDSOI             | 156 ± 5                        | 208 ± 50 |

**Tab.1**  $-R_{sd}|V_{gs}=1.1V$  values extracted for bulk and FDSOI MOSFETs and compared to results obtained from the  $\Theta(\beta)$ technique. As expected, the  $R_{tot}(1/\beta)$ method gives more accurate results which remain in line with  $\Theta(\beta)$ .

L<sub>eff</sub> (nm)

**Fig.3** – uncertainty on the  $R_{tot}(L)$  technique due to  $\mu(L)$  degradation on short channels

extracted from the intercept with the y-axis.

$1/\beta$  (A/V<sup>2</sup>)

**Fig.9** –  $R_{sd}$  and  $\Theta_{1,0}$  extracted from the  $\Theta_1(\beta)$ technique. In inset: error distribution

## References

[1] The ITRS, Semiconductor Ind. Assoc., 2006.

- [2] K.M. Cao et al., IEDM.1999 pp. 171-174

- [3] F. Andrieu et al., IEEE EDL, Oct 2005

- [4] A. Cros et al., IEDM.2006 pp. 663-666

- [5] Y. Taur et al., IEEE EDL, May 1992

- [6] G.J. Hu et al., IEEE TED, Dec 1997

- [7] Y.H. Chang et al., EDSSC 2007, pp.87-90

- [8] J. Kim et al., IEEE TED, Oct 2008

- [9] E. Josse et al., IEDM 2006, pp. 693

- [10] D. Aimé et al., ESSDERC 2007, pp.255-258

- [11] P.K. McLarty et al., SSE, Jun 1995

- [12] D. Fleury et al., ICMTS 2008, pp.160-165

- [13] D. Fleury et al., IEEE T-SM, Nov 2008

- [14] S.D. Kim et al, IEEE TED, Mar2002 [15] G. Ghibaudo, Electronics Letters, Apr 1988

- [16] C.Mourrain et al, ICMTS 2000, pp.181-186

300