# Diode-clamped multilevel converters with integrable gate-driver power-supply circuits

S. Busquets-Monge, J. Rocabert, Jean-Christophe Crébier, J. Peracaula

## ▶ To cite this version:

S. Busquets-Monge, J. Rocabert, Jean-Christophe Crébier, J. Peracaula. Diode-clamped multilevel converters with integrable gate-driver power-supply circuits. EPE 09, Sep 2009, Barcelone, Spain. hal-00422539

HAL Id: hal-00422539

https://hal.science/hal-00422539

Submitted on 7 Oct 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Diode-Clamped Multilevel Converters with Integrable Gate-Driver Power-Supply Circuits

S. Busquets-Monge<sup>1</sup>, J. Rocabert<sup>1</sup>, J.-C. Crebier<sup>2</sup>, and J. Peracaula<sup>1</sup>

<sup>1</sup>TECHNICAL UNIVERSITY OF CATALONIA <sup>2</sup>GRENOBLE INSTITUTE OF TECHNOLOGY

Av. Diagonal, 647 UMR 5529 BP 46 08028 Barcelona, Spain 38402 Grenoble, France Tel.: +34 / (93) – 401.71.52. Tel.: +04 / (76) – 82.71.43.

Fax: +34 / (93) – 401.77.85. Fax: +04 / (76) – 82.63.00. E-Mail: sergio.busquets@upc.edu E-Mail: jean-christophe.crebier@g2elab.inpg.fr URL: http://www.leg.ensieg.inpg.fr/G2Elab/

## Acknowledgements

This work was supported by the Ministerio de Educación y Ciencia, Madrid, Spain, under Grant TEC2005-08042-C02.

## **Keywords**

«Multilevel converters», «Pulse Width Modulation (PWM)», «Modulation strategy», «Monolithic power integration», «System integration».

#### Abstract

Recent contributions in pulse width modulations (PWM) for multilevel diode-clamped converters enable the use of these converters with passive front-ends, any number of levels, and small dc-link capacitors. Highly compact converters designs based on these topologies can be envisioned. However, the design of the gate-driver power-supply for the multiple controlled semiconductor devices remains an important issue to be addressed. This paper focuses on the design of such circuits and the analysis of the resulting multilevel converter performance. A simple circuit connected across each power switch and monolithically integrable within it is selected. These circuits lead to simple, compact, and efficient converter designs. The main issues arising from the operation of the multilevel converter with such circuits are analyzed, and both hardware and software solutions are proposed. In particular, a new PWM strategy is presented. Experimental results are provided verifying the good performance of all proposed solutions.

## Introduction

Multilevel converters have opened a door for advances in the electric energy conversion technology [1], [2], not only in high power applications, but also for medium and low power designs [3]–[5], since they present the advantages of a lower device voltage rating, a lower harmonic distortion, and higher efficiency compared to conventional two-level converters. This paper focuses primarily on medium and low power applications.

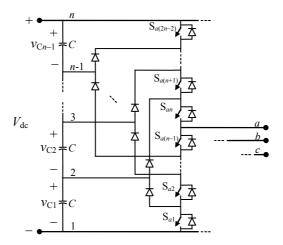

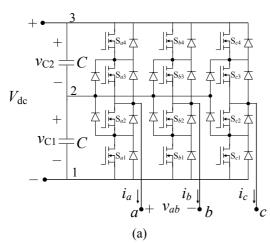

Among multilevel topologies, diode-clamped converters are especially interesting because of their simplicity (see Fig. 1). The multiple voltage levels are obtained through a series connection of identical capacitors. Recent contributions in PWMs for diode-clamped converters [6] have enabled the use of these converters with passive front-ends, any number of levels and small dc-link capacitors. This opens the

Fig. 1: *n*-level diode-clamped topology with multiple legs.

possibility of obtaining compact converter designs based on these topologies. However, in order to achieve a simple and integrable converter design, one of the first and most important issues to address is the design of the multiple isolated gate-driver power supplies required.

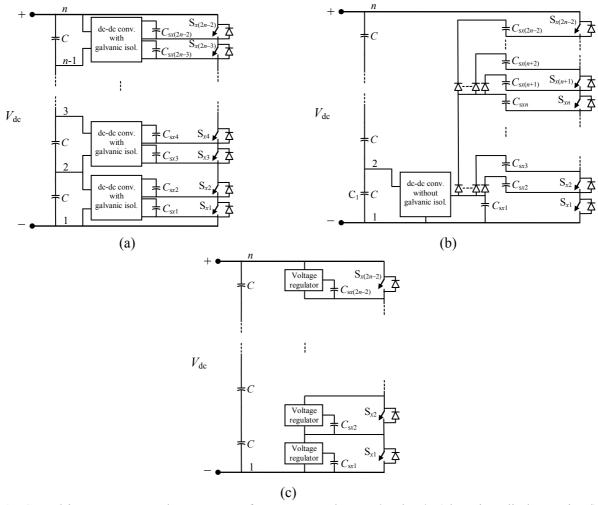

There are several options to generate an isolated low regulated voltage to feed the active-devices gate drivers: low-power dc-dc converters with galvanic isolation, topologies using coreless transformers, charge pump circuits, etc. Fig. 2 shows three possible structures. Fig. 2(a) presents a solution based on dcdc converters with galvanic isolation extracting the energy from the dc-link capacitors. Every dc-link capacitor feeds two gate drivers. The two dc-dc converter outputs are isolated. Capacitor C<sub>sxi</sub> stores the energy necessary to drive device  $S_{xi}$ . This structure has the benefits of an equally distributed energy withdrawal from the dc-link capacitors. The problem is the need for galvanic isolation for all dc-dc converters, which usually calls for the introduction of high-frequency transformers. This solution is therefore discarded because of its complexity, size and cost. An alternative solution without the need of galvanic isolation is shown in Fig. 2(b). This structure is based on the bootstrap charge pump concept, which has been already applied in multilevel converters [3], [5]. The single low-voltage power supply required by the structure can be obtained from the dc-link capacitor C<sub>1</sub>, as shown in Fig. 2(b). However, these topologies are not adequate to be monolithically integrated within the active devices [7], can cause electromagnetic interference problems, and are asymmetric from both the point of view of topology and operation. Recently, other alternative topologies connected across the power device and being fully integrable within it have been proposed [7]-[10]. From these topologies, the structure in Fig. 2(c) is proposed. The gate-driver power-supply capacitors are fed from the energy available across the switch when it turns off. There are several options to implement the voltage regulator modules in Fig. 2(c) [7]-[10]. These circuits have been tested in simple buck and flyback dc-dc converters. This paper explores whether this concept can be applicable to a multilevel diode-clamped converter and evaluates the performance of such converters.

# **Gate-Driver Power-Supply Topology and Operation Principle**

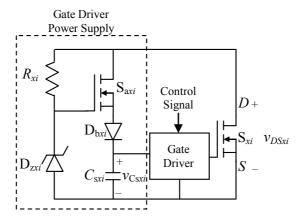

The selected gate-driver power-supply topology is shown in Fig. 3 [8]. The energy to drive the device is obtained from the energy that is otherwise lost during the main power switch S turn-off transition and, eventually, from the corresponding dc-link capacitor connected across the switch during its off state. This energy is stored in capacitor  $C_s$ . The current charging capacitor  $C_s$  flows through the auxiliary metal oxide semiconductor field effect transistor (MOSFET)  $S_a$ . The zener diode  $D_z$ , polarized by resistor R, limits the value of  $v_{Cs}$  and the blocking diode  $D_b$  prevents the discharging of  $C_s$  when the main power switch S is on.

Fig. 2: Gate-driver power-supply structures for converter leg  $x \in \{a, b, c\}$  (clamping diodes omitted). (a) Structure 1 based on dc-dc converters with galvanic isolation. (b) Structure 2 based on the bootstrap technique. (c) Structure 3 using voltage regulators connected across the active devices.

Fig. 3: Gate-driver power-supply circuit ( $x \in \{a, b, c\}$ ,  $i \in \{1, 2, ..., 2n-2\}$ ).

### **Initial Converter Control**

# Adjustment of the Gate-Driver Power-Supply Capacity

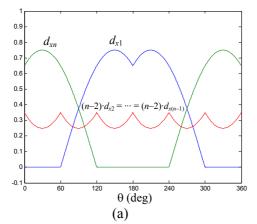

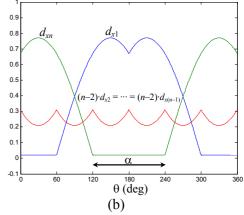

To operate the converter, the PWM strategy presented in [6] and the capacitor-voltage balancing control presented in [11] are initially selected. This control scheme presents the benefit of guaranteeing the dc-link capacitor voltage balance in every switching cycle provided that the addition of the output leg currents equals zero, and thus, enables the operation of an n-level converter with low dc-link capacitance values. Fig. 4(a) presents the corresponding leg duty-ratio pattern ( $d_{xy}$ , corresponding to the leg x duty ratio of connection to dc-link point y) for a three-leg converter at a given modulation index value ( $m \in [0,1]$  for linear modulation) over a line cycle ( $\theta$ : ac-side line-cycle angle). The different power switch duty-ratios,  $d_{Sxi}$ , can be easily computed from these waveforms. It is important to note that the two most inner devices of each converter leg ( $S_{xn}$  and  $S_{x(n-1)}$ ) remain on for 120° intervals every line cycle since the corresponding duty-cycle values

$$d_{Sx(n-1)} = \sum_{j=1}^{n-1} d_{xj}$$

$$d_{Sxn} = \sum_{j=2}^{n} d_{xj}$$

(1)

are equal to the unity during these intervals. This prevents the corresponding capacitor  $C_s$  from being charged during this period. In order to prevent its discharging below the minimum voltage value for correct operation of the gate driver, it is required to select a capacitance value  $C_s$  higher than for other devices, for which the switch duty-ratio is always lower than the unity and, therefore, the corresponding capacitor  $C_s$  is recharged every switching cycle. This required value of  $C_{sxn}$  and  $C_{sx(n-1)}$  will depend upon the ac-side line-cycle frequency ( $f_o$ ). The lower the frequency is, the higher the required value of these two capacitors per leg.

The performance of this control scheme has been tested in the three-level three-leg converter prototype shown in Fig. 5. The components of the gate-driver power-supply are outlined in Table I. The converter is operated in inverter mode with a single dc power supply connected to dc-link points 1 and 3 and a wye-connected three-phase series R-L load connected to the ac side. The computation of the six independent phase duty-ratios is performed by the embedded PowerPC of dSpace DS1103. This information is sent to an Altera EPF10K70 programmable logic device in charge of generating the twelve switch control signals.

Fig. 4: Leg x duty-ratio pattern for an *n*-level three-leg converter (m = 0.75). (a) Original PWM scheme. (b) Modified PWM scheme with  $d_{\text{offset}} = 0.02$ .

Fig. 5: Three-level three-leg dc-ac converter. (a) Topology. (b) Prototype using 150 V MOSFETs as devices  $S_{vi}$ .

**Table I: Gate-driver power-supply components**

| Component Symbol | Selected Component       |

|------------------|--------------------------|

| $S_a$            | IRF5802TR (150 V, 0.9 A) |

| $D_b$            | 10BQ040 (40 V, 1 A)      |

| R                | 10 kΩ                    |

| $D_z$            | BZX85C22 (22 V)          |

| C <sub>s</sub>   | 330 nF, polypropilene    |

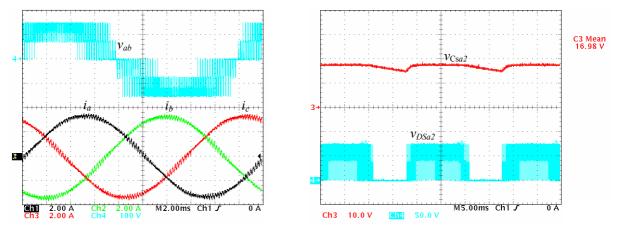

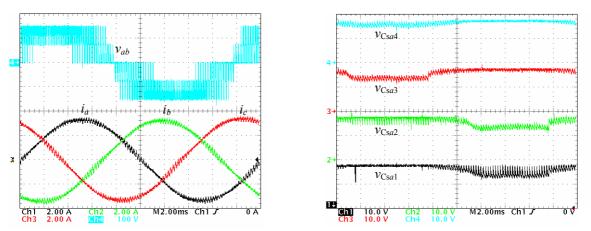

Fig. 6 shows the experimental results obtained with this control scheme and adding  $10 \mu F$  electrolytic capacitors to  $C_{sx2}$  and  $C_{sx3}$ . It can be observed that the converter is operating correctly at a high modulation index value (m = 0.95). Note the footprint of the selected PWM on the line-to-line voltage  $v_{ab}$ . We can also observe that during a  $120^{\circ}$  period over the line cycle, capacitor  $C_{sa2}$  discharges because the corresponding device is on. However, the addition of  $10 \mu F$  capacitors to these inner switch positions prevents the supply voltage from falling beyond the minimum allowed value. Once the device starts switching on and off in every switching cycle, the capacitor is quickly recharged. As mentioned earlier, the value of the required capacitance depends on the output line-cycle frequency. Typically, a relatively high value will be needed, which implies that the recharging process will take place essentially during the off state of the main device without recycling turn-off losses and therefore presenting a lower efficiency.

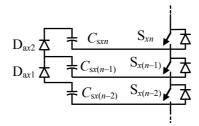

## Addition of an Auxiliary Bootstrap Circuit

An alternative solution to increasing the value of  $C_s$  for the two most inner devices of each leg is the introduction of two diodes per leg to implement the bootstrap circuit of Fig. 7. This bootstrap circuit involves three power devices per leg:  $S_{xn}$ ,  $S_{x(n-1)}$ , and  $S_{x(n-2)}$ . During the 120° in which  $S_{x(n-1)}$  is on, its corresponding gate-driver power-supply capacitor is fed from the energy stored in  $C_{sx(n-2)}$ . During the 120° in which  $S_{xn}$  is on, its corresponding gate-driver power-supply capacitor is fed from the energy stored in  $C_{sx(n-1)}$ .

Fig. 6: Experimental results for  $v_{ab}$ ,  $i_a$ ,  $i_b$ ,  $i_c$ ,  $v_{Csa2}$ , and  $v_{DSa2}$  in the following conditions:  $V_{dc} = 150 \text{ V}$ , m = 0.95,  $C = 155 \mu\text{F}$ ,  $C_{sx1} = C_{sx4} = 330 \text{ nF}$ ,  $C_{sx2} = C_{sx3} = 330 \text{ nF} + 10 \mu\text{F}$  ( $x \in \{a, b, c\}$ ), switching or carrier frequency  $f_s = 5 \text{ kHz}$ , and a linear and balanced load with per-phase impedance  $Z_L = 22.5 \Omega \angle 12^\circ$  (series R-L load).

Fig. 7: Auxiliary bootstrap circuit.

Fig. 8 shows the experimental results of this new configuration with the three-level converter prototype of Fig. 5 and all gate-driver capacitors equal to 330 nF. The converter is operating correctly. However, note the voltage drop in  $v_{Csa2}$  and  $v_{Csa3}$  due to the conduction voltage drop in the auxiliary diodes  $D_{aa1}$  and  $D_{aa2}$ . Additionally, these two extra diodes per leg cannot be monolithically integrated within the power devices.

Fig. 8: Experimental results for  $v_{ab}$ ,  $i_a$ ,  $i_b$ ,  $i_c$ ,  $v_{Csa1}$ ,  $v_{Csa2}$ ,  $v_{Csa3}$ , and  $v_{Csa4}$  in the following conditions:  $V_{dc} = 150 \text{ V}$ , m = 0.95, C = 155 µF,  $C_{sx1} = C_{sx2} = C_{sx3} = C_{sx4} = 330 \text{ nF}$  ( $x \in \{a, b, c\}$ ), auxiliary diodes  $D_{ax1}$  and  $D_{ax2}$  1N4148, switching or carrier frequency  $f_s = 5 \text{ kHz}$ , and a linear and balanced load with per-phase impedance  $Z_L = 22.5 \Omega \angle 12^\circ$  (series R-L load).

#### **Modified Converter Control**

The previous converter control scheme performs satisfactorily, but requires an increased value of  $C_s$  for the two most inner devices of each leg or the addition of two diodes per leg to implement the auxiliary bootstrap circuit of Fig. 7. In order to be able to operate with the configuration of Fig. 2(c), with the same low  $C_s$  value for all devices, and without the need of extra diodes, therefore obtaining a simple modular design, a new PWM strategy is proposed modifying the previous one. The equations describing this new PWM scheme with reference to the original [6] are

$$d'_{x1} = d_{x1} + d_{\text{offset}}$$

$$d'_{xn} = d_{xn} + d_{\text{offset}}$$

$$d'_{xi} = d_{xi} - \frac{2 \cdot d_{\text{offset}}}{n - 2}$$

$$x \in \{a, b, c\}; \quad i \in \{2, 3, ..., n - 1\}$$

(2)

where  $d_{\text{offset}}$  is given, in principle, a small constant value over time. Fig. 4(b) presents the leg duty-ratio pattern for  $d_{\text{offset}} = 0.02$ . It can be seen that the original duty-ratio waveforms  $d_{x1}$  and  $d_{xn}$  are slightly shifted upwards, so that both leg duty-ratios are always greater than zero. This is equivalent to employing switching states 111 and *nnn* in approximating the reference vector when defining the PWM strategy with the aid of a space vector diagram [6]. This modification does not affect the switching-frequency averaged voltage waveforms since a zero average offset is applied to the three converter leg voltages  $v_{x1}$ .

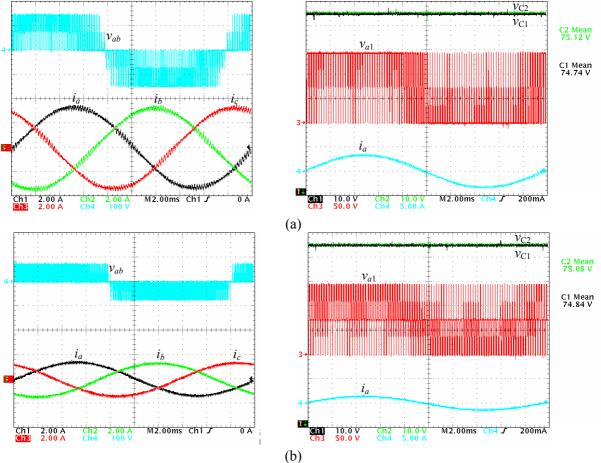

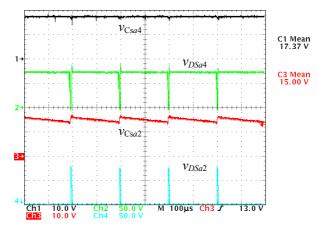

The proposed PWM strategy has been tested in the prototype of Fig. 5 with  $C_s$  = 330 nF for all gate-driver power-supply capacitors. Fig. 9 and Fig. 10 present the experimental results. It can be observed that the converter is performing satisfactorily for both high (Fig. 9(a)) and low (Fig. 9(b)) modulation index values. Note the new footprint of the PWM scheme on the line-to-line voltage  $v_{ab}$  and that the dc-link capacitor voltages  $v_{C1}$  and  $v_{C2}$  are balanced in every switching cycle. Fig. 10 shows the gate-driver power-supply capacitor voltages and drain-to-source voltages of devices  $S_{a2}$  and  $S_{a4}$  (see Fig. 5(a)). A few switching periods are shown corresponding to the 120° region  $\alpha$  in Fig. 4(b). Capacitor  $C_{sa2}$  is correctly recharged every switching cycle despite the short period of time device  $S_{a2}$  is off.

The new PWM scheme allows operating with the gate-driver power-supply structure of Fig. 2(c) and small C<sub>s</sub> capacitors regardless of the output line-cycle frequency. However, this advantage is obtained at the expense of increasing the number of switching transitions per switching cycle (and hence, the switching losses), increasing the ac-side voltage harmonic distortion, and reducing the maximum value of the modulation index in the linear modulation range.

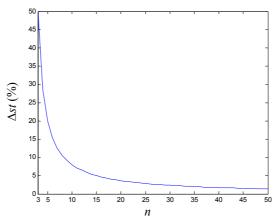

First of all, the percentage increase in per-switching-cycle switching transitions of the modified PWM strategy with reference to the original PWM strategy is

$$\Delta st = \frac{2}{3n-5} \cdot 100 \quad (\%), \tag{3}$$

Fig. 11 deploys this percentage increase as a function of the number of levels. It can be seen that  $\Delta st$  decreases rapidly as the number of levels increases, and so does the associated increase in switching losses. Therefore, for a value of n large enough the increase in switching losses might be deemed not significant.

Fig. 9: Experimental results for  $v_{ab}$ ,  $i_a$ ,  $i_b$ ,  $i_c$ ,  $v_{C1}$ ,  $v_{C2}$ , and  $v_{a1}$  in the following conditions:  $V_{dc} = 150 \text{ V}$ ,  $C = 155 \mu\text{F}$ ,  $C_{\text{sx1}} = C_{\text{sx2}} = C_{\text{sx3}} = C_{\text{sx4}} = 330 \text{ nF}$  ( $x \in \{a, b, c\}$ ),  $d_{\text{offset}} = 0.02$ ,  $f_{\text{s}} = 5 \text{ kHz}$ , and a linear and balanced load with per-phase impedance  $Z_L = 22.5 \Omega \angle 12^{\circ}$  (series R-L load). (a) m = 0.95. (b) m = 0.4.

Fig. 10: Experimental results for  $v_{Csa2}$ ,  $v_{Csa4}$ ,  $v_{DSa2}$ , and  $v_{DSa4}$  in the same conditions as in Fig. 9 and m = 0.95.

Fig. 11: Percentage increase in per-switching-cycle switching transitions of the modified PWM strategy with reference to the original PWM strategy, as a function of the number of levels.

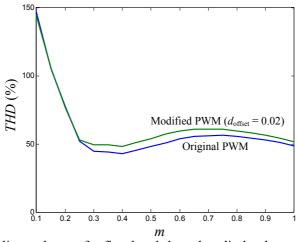

Second, Fig. 12 presents the total harmonic distortion (THD) in the output line-to-line voltage of a five-level three-leg diode-clamped converter as a function of the modulation index for both the original and modified PWM schemes. It can be observed that there is a clear increase of the THD in the new PWM strategy, especially for high values of m. However, this increase may not be significant for many applications.

Finally, since all duty-ratios must have a value between 0 and 1, the maximum value of the modulation index in the linear modulation range with the modified PWM strategy is

$$m_{\text{max}} = 1 - 2 \cdot d_{\text{offset}} \tag{4}$$

In general, this decrease in the maximum value is not significant since a small value of  $d_{\text{offset}}$  can be typically selected. The minimum value of  $d_{\text{offset}}$  is determined from the driver and device technology.

Fig. 12: *THD* in the line-to-line voltage of a five-level three-leg diode-clamped converter as a function of the modulation index m. Conditions:  $f_s / f_o = 100$  and harmonics considered up to  $40 \cdot f_s$ .

## Conclusion

This paper proves the feasibility of integrating the gate-driver power supply in all devices of a multilevel diode-clamped converter. These transformerless circuits avoid the need of incorporating conventional isolated dc-dc power supplies to feed each device driver and, hence, lead to simple and compact multilevel converter designs, more efficient than conventional two-level converters.

The use of existing PWM strategies for operating the multilevel converter requires an increase of two gate-driver power-supply capacitances per leg or the introduction of two bootstrap diodes per leg. Alternatively, the novel PWM strategy presented can be used in order to achieve a simple modular design, independent from the output ac voltage frequency and without the need of additional components. This solution combines the benefits of being modular and integrable, and ensures that the energy required to drive the switches is drawn homogenously from all dc-link capacitors. The drawbacks from this new PWM with regard to switching losses are not significant for a number of levels large enough. The increase in ac-side voltage distortion and the decrease in maximum modulation index may not be significant for many applications.

## References

- [1] J. Rodríguez, J. Lai, and F. Peng: Multilevel inverters: a survey of topologies, controls and applications, IEEE Trans. Ind. Electron., vol. 49, pp. 724-738, Aug. 2002.

- [2] L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo, and M. A. M. Prats: The age of multilevel converters arrives, IEEE Ind. Electron. Magazine, vol. 2, pp. 28-39, 2008.

- [3] B. A. Welchko, M. B. de Rossiter Correa, and T. A. Lipo: A three-level MOSFET inverter for low-power drives, IEEE Trans. Ind. Electron., vol. 51, pp. 669-674, June 2004.

- [4] R. Teichmann and S. Bernet: A comparison of three-level converters versus two-level converters for low-voltage drives, traction, and utility applications, IEEE Trans. Ind. Applicat., vol. 41, pp. 855-865, May-June 2005.

- [5] S. A. Molepo and H. du T. Mouton: A flying capacitor multilevel inverter with bootstrap-powered MOSFET gate drive circuits, in Proc. IEEE Power Electronics Specialists Conf., 2002, pp. 701-705.

- [6] S. Busquets-Monge, S. Alepuz, J. Rocabert, and J. Bordonau: Pulsewidth modulations for the comprehensive capacitor voltage balance of n-level diode-clamped converters, in Proc. IEEE Power Electronics Specialists Conf., 2008, pp. 4479-4486.

- [7] R. Mitova, J.-C. Crebier, L. Aubard, and C. Schaeffer: Fully integrated gate drive supply around power switches, IEEE Trans. Power Electron., vol. 20, pp. 650-659, May 2005.

- [8] J.-C. Crebier and N. Rouger: Loss free gate driver unipolar power supply for high side power transistors, IEEE Trans. Power Electron., vol. 23, pp. 1565-1573, May 2008.

- [9] N. Rouger and J.-C. Crebier: Toward generic fully integrated gate driver power supplies, IEEE Trans. Power Electron., vol. 23, pp. 2106-2114, July 2008.

- [10] N. Rouger, J.-C. Crebier, H. Tran Manh, and C. Schaeffer: Toward integrated gate driver supplies: Practical and analytical studies of high-voltage capabilities, in Proc. IEEE Power Electronics Specialists Conf., 2008, pp. 873-879.

- [11] S. Busquets-Monge, S. Alepuz, J. Bordonau, and J. Peracaula: Voltage balancing control of diode-clamped multilevel converters with passive front-ends, IEEE Trans. Power Electron., vol. 23, pp. 1751-1758, July 2008.