# Etude de l'Elaboration d'Interconnexions Electrodéposées en Electronique de Puissance

Ludovic Ménager, Quoc Hung Luan, Van Hai N'Guyen, Bruno Allard, Vincent Bley, Christian Martin, Thierry Lebey, Philippe Castelan, Zoubir Khatir, Benoît Schlegel, et al.

# ▶ To cite this version:

Ludovic Ménager, Quoc Hung Luan, Van Hai N'Guyen, Bruno Allard, Vincent Bley, et al.. Etude de l'Elaboration d'Interconnexions Electrodéposées en Electronique de Puissance. MGE'2008, May 2008, Toulouse, France. pp.on CD - 78-81/215. hal-00412449

# HAL Id: hal-00412449 https://hal.science/hal-00412449v1

Submitted on 1 Sep 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Etude de l'Elaboration d'Interconnexions Electrodéposées en Electronique de Puissance

L. Ménager <sup>1, 2</sup>, Q.H. Luan <sup>2</sup>, V.H. N'Guyen <sup>2</sup>, B. Allard <sup>1</sup>, V. Bley <sup>2</sup>, C. Martin <sup>3</sup>, T. Lebey <sup>2</sup>, P. Castelan <sup>2</sup>, Z. Khatir <sup>4</sup>, B. Schlegel <sup>2</sup> et T. Vaday <sup>2</sup>

<sup>1</sup> AMPERE, INSA de Lyon, Bâtiment Léonard de Vinci,

21 Avenue Jean Capelle, 69621 Villeurbanne Cedex, France

<sup>2</sup> Université de Toulouse, LAPLACE, CNRS, INPT, UPS,

Bâtiment 3R3, 118 Route de Narbonne, 31062 Toulouse Cedex 9, France

<sup>3</sup> Université de Lyon, AMPERE, CNRS, UMR5005, INSA de Lyon, Ecole Centrale de Lyon, Université Lyon 1, Bâtiment Oméga, 43 Boulevard du 11 Novembre, 69622 Villeurbanne Cedex, France

<sup>4</sup> Laboratoire des Technologies Nouvelles, INRETS,

2 Avenue du Général Malleret – Joinville, 94114 Arcueil Cedex, France

E-mail: ludovic.menager@insa-lyon.fr ou ludovic.menager@laplace.univ-tlse.fr

**Résumé:** Les connexions électriques dans les modules de puissance sont actuellement réalisées par des fils de bondings. Dans certaines applications, recherchant une densité de puissance élevée, la technologie wire bonding montre des limites électriques, thermiques et thermomécaniques. Pour répondre à ce besoin, des technologies d'interconnexion 3D, utilisant la plupart des brasures, ont été développées. Or, l'expérience et des études ont montré des défaillances au niveau des brasures. Dans cet article, des solutions d'interconnexion 3D sans brasure sur des puces de puissance sont présentées.

#### Introduction

Dans les modules de puissance actuels, les connexions électriques sont réalisées par des fils de bondings. Dans certaines applications, nécessitant une densité de puissance élevée, la technologie wire bonding montre des limites électriques [1], thermiques [2] et mécaniques (fiabilité) [3] en limitant de surcroît les possibilités d'intégration 3D. De ce fait, des technologies d'interconnexion 3D ont été développées pour permettre de trouver une solution qui répond à ces exigences [4]. La plupart des interconnexions 3D utilisent des brasures. Cependant, l'expérience et les études ont montré l'apparition de fatigues mécaniques menant à des fissures au niveau de l'interface de métallisation de la puce par rapport à la brasure, activées par le cyclage thermique ou lors de refusion durant l'assemblage [5].

Cet article présente deux technologies d'interconnexion 3D sans brasure sur des puces de puissance par voie électrolytique appelées technologies nano et micro poteaux. L'intérêt et le principe de l'électrodéposition sont présentés. Les procédés de mise en œuvre de ces deux technologies ainsi que les matrices utilisées pour la croissance électrolytique sont décrits.

#### Intérêt et principe de l'électrodéposition

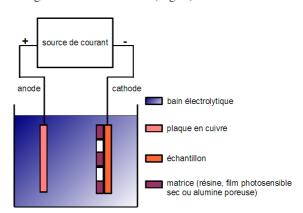

La réalisation des interconnexions sur les métallisations des puces de puissance est faîte par électrodéposition. D'autres méthodes de dépôt de métaux existent à savoir l'évaporation, la pulvérisation et l'*electroless*. Cependant, ces techniques ne permettent pas de réaliser des structures avec des épaisseurs avoisinants 100µm et des nano interconnexions (1µm - 2µm d'épaisseur) à travers une membrane poreuse. Le métal déposé est le cuivre, qui présente à la fois une bonne conductivité électrique et thermique. L'électrodéposition se réalise dans une cuve contenant un bain électrolytique dans lequel sont plongés deux électrodes reliées aux bornes d'un générateur de courant (Fig. 1).

Figure 1 : Cellule d'électrodéposition

Le bain électrolytique est une solution chimique contenant des ions métalliques M<sup>n+</sup> de charge positive. L'échantillon sur lequel doit s'effectuer le dépôt est fixé sur la cathode. La polarisation des électrodes va provoquer une migration des ions métalliques vers la cathode, c'est-à-dire vers l'échantillon. Les ions métalliques sont neutralisés par les électrons e fournis par la cathode et se déposent sur celle-ci sous forme de métal M, suivant la réaction chimique :

$$M^{n+} + n.e^{-} \rightarrow M \tag{1}$$

Dans le cas du cuivre, la réaction chimique est la suivante :

$$Cu^{2+} + 2.e^{-} \rightarrow Cu \tag{2}$$

La croissance électrolytique ne pouvant s'effectuer directement sur les métallisations aluminium des puces, ces dernières sont donc recouvertes d'une couche d'accroche. Celle-ci se compose d'une couche métallique mince à haute adhérence (Ti, Cr, ...) et d'une couche métallique conductrice plus épaisse (Ag, Cu, ...), qui peuvent être déposées par évaporation, pulvérisation ou voie chimique.

# Technologie nano poteaux

Actuellement, l'utilisation des nano fils métalliques en électronique de puissance, micro électronique et stockage d'énergie ne cesse d'augmenter [7, 8, 9, 10, 11, 12]. Le procédé de fabrication d'une interconnexion électrique et mécanique en cuivre déposée par voie électrolytique à travers une membrane d'alumine poreuse *Anodic Aluminum Oxide* (*AAO*) et appelée nano poteaux est tout d'abord présenté. Un assemblage basé sur l'interpénétration et l'enchevêtrement des nano poteaux et appelé « nano scratch » est ensuite décrit.

#### Anodic Aluminum Oxide

Depuis la découverte en 1995 par *Masuda* [13] que sous certaines conditions d'anodisation de l'aluminium, il était possible d'obtenir des membranes d'alumine présentant des réseaux hautement organisés de pores de tailles nanométriques, les membranes n'ont cessé de susciter un intérêt croissant [14]. La structure de l'*AAO*, considérée stable avec la température dans des solvants inorganiques, présente une uniformité des pores parallèles et perpendiculaires à la surface. Elle s'apparente à une matrice idéale [12].

### Procédé de fabrication

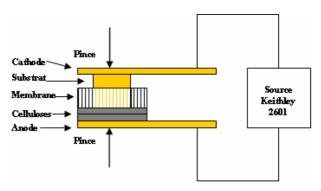

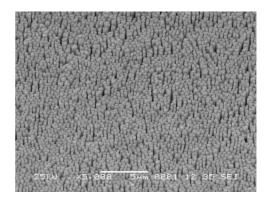

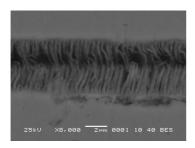

La réalisation des nano poteaux en cuivre s'effectue par électrodéposition dans un bain électrolytique contenant 100g/L de sulfate de cuivre CuSO<sub>4</sub>-5H<sub>2</sub>O, 20g/L de sulfate d'ammonium (NH<sub>4</sub>)<sub>2</sub>SO<sub>4</sub> et 80mL/L de diethyltriamine (Fig. 2). La croissance électrolytique est réalisée à travers une matrice d'alumine poreuse *AAO* d'épaisseur 60μm, de porosité entre 50% - 65%, de diamètre 47mm et de densité de pores 10<sup>10</sup>cm<sup>-2</sup>. Une source *KEITHLEY 2601* est utilisé comme une source de courant et génère un courant cathodique pulsé - 2mA (250ms) et -30mA (50ms). Après l'électrodéposition, la dissolution de la membrane *AAO* est effectuée dans la solution NaOH 1M à 80°C pendant 30s. La Fig. 3 montre des nano poteaux en cuivre électrodéposés d'épaisseur 2μm – 3μm. Le diamètre des nano poteaux

est compris entre 20nm et 200nm et la densité des nano poteaux est d'environ 1milliard/cm<sup>2</sup>.

Figure 2: Manipulation d'électrodéposition

Figure 3 : Photo MEB de nano poteaux en cuivre électrodéposés

# Assemblage « nano scratch »

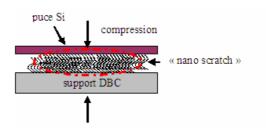

L'assemblage « nano scratch » est un procédé simple, économique et à froid (Fig. 4). Celui est réalisé par l'interpénétration et l'enchevêtrement des nano poteaux en cuivre électrodéposés sur la face arrière d'un composant de puissance et un substrat type DBC. La pression exercée lors de l'assemblage est comprise entre 20MPa et 100MPa. Afin de permettre un assemblage mécanique performant, une campagne d'essais a été menée pour favoriser l'interpénétration des nano poteaux. La solution utilisée consiste à attaquer chimiquement la périphérie des nano poteaux. La Fig. 5 montre un assemblage « nano scratch ».

Figure 4 : Principe d'assemblage "nano scratch"

Figure 5: Photo MEB d'un assemblage "nano scratch"

#### Technologie micro poteaux

La technologie micro poteaux correspond à des micro poteaux en cuivre dont la surface est de 100μm-400μm\*100μm-400μm et l'épaisseur est comprise entre 50μm et 100μm. Ces dimensions sont similaires à celles des interconnexions 3D *bumps* (Fig. 6).

Figure 6 : Technologie bump sur un transistor MOSFET [15]

La Fig. 7 montre le procédé de fabrication des micro poteaux sur les métallisations des puces. L'électrodéposition des micro poteaux est réalisée à travers une matrice en film photosensible sec, qui est une alternative aux solutions classiques types résines positives (AZ9260, ...) et négatives (SU8, ...).

Figure 7 : Procédé de fabrication de la technologie micro poteaux

### Film photosensible sec

Le film photosensible sec est une solution intéresssante en termes de coût et de facilité de mise en œuvre. Son adhérence sur les substrats est bonne. Pour des faibles surfaces similaires à celle d'une puce, les effets de bords sont minimisés. Le film photosensible sec, composé d'une résine photosensible fixée entre un film de protection en polyoléfine et un support en polyester, est déposé par laminage ou thermocompression. Le film photosensible sec utilisé est le *Riston PM275* de la société *Dupont* et son épaisseur est de 75µm [16].

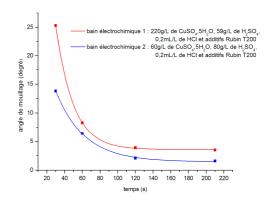

Lors de l'électrodéposition, on constate la formation de bulles d'air dans les motifs où on souhaiter déposer le cuivre. Ceci s'explique en partie par une mauvaise mouillabilité du film photosensible sec. Pour améliorer celle-ci, un traitement par plasma argon sur le film photosensible sec est effectué avant l'électrodéposition. Après un traitement d'une durée de 1min, l'angle de mouillage mesuré avec une solution électrochimique passe de 64° (sans traitement) à 8° (avec traitement). La Fig. 8 montre que l'augmentation de la durée du traitement par plasma argon permet de diminuer l'angle de mouillage. Après traitement plasma argon, l'angle de mouillage peut être légèrement améliorée en modifiant la composition du bain électrochimique à savoir en mettant une basse teneur en sulfate de cuivre (bain électrochimique 2).

Figure 8 : Influence de la durée du traitement par plasma argon sur l'angle de mouillage du film photosensible sec

## Réalisation

La manipulation pour réaliser la technologie micro poteaux sur des puces est présentée en Fig. 9. Les amenées de courant sur la puce, nécessaires pour effectuer l'électrodéposition des connectiques, sont des fils électriques fixés avec de la colle époxy conductrice chargée argent et sans solvant. Les paramètres de la manipulation utilisée sont les suivants :

- Anode: plaque de cuivre sans oxygène OFHC (10cm\*4cm)

- Distance entre l'anode et la puce : 30mm 35mm

- Bain électrolytique : 220g/L de CuSO<sub>4</sub>-5H<sub>2</sub>O, 59g/L de H<sub>2</sub>SO<sub>4</sub>, 0,2mL/L de HCl et additifs Rubin T200

- Température d'utilisation du bain : 25°C – 27°C

- Densité du courant : 40mA/cm<sup>2</sup>

- Vitesse du dépôt : 800nm/min à 40mA/cm<sup>2</sup>

Figure 9 : Manipulation d'électrodéposition

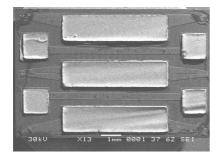

La Fig. 10 montre des micro poteaux en cuivre de 400µm\*400µm électrodéposés.

Figure 10 : Photo MEB de micro poteaux en cuivre électrodéposés

Pour vérifier et valider le bon fonctionnement électrique de l'ensemble puce et connectiques électrodéposées, des puces MOSFETs APT6035BVFR 600V/18A avec des poteaux en cuivre électrodéposés ont été réalisées (Fig. 11).

Figure 11 : Photo MEB d'une puce MOSFET avec des poteaux en cuivre électrodéposés (épaisseurs : 30μm (grille) et 50μm (source))

Différentes solutions technologiques de reprise de contacts sans brasure sur le dessus des micro poteaux telles que le report par des pistes électrodéposés ou l'assemblage par pression et déformation élastique des micro poteaux sont en cours d'études.

#### **Conclusion et perspectives**

Cet article présente deux technologies d'interconnexion sans brasure sur des composants de puissance en vue d'une intégration tridimensionnelle dans les modules de puissance. Des travaux sur l'optimisation des procédés de réalisation des nano/micro poteaux et les techniques d'assemblage ainsi que les caractérisations électriques, thermiques et mécaniques sont envisagés pour la suite.

#### Références

- [1] K. Xing, F. Lee and D. Borojevic, "Extraction of parasitics within wire bond IGBT modules", IEEE Conference Proceeding, Applied Power Electronics Conference and Exposition, vol. 1, pp. 497-503, Feb. 1998.

- [2] S. Wen, "Thermal and thermo mechanical analyses of wire bond vs three dimensionally packaged power electronics modules", Master's thesis, Virginia Polytechnic Institute, Dec. 1999.

- [3] S. Ramminger, P. Turkes, and G. Wachutka, "Crack mechanism in wire bonding joints", Microelectronics Reliability, vol. 38, pp. 1301-1305, 1998.

- [4] L. Ménager, B. Allard, V. Bley and C. Martin, "Industrial and lab-scale power module technologies: a review", IEEE Industrial Electronics, IECON 2006, pp. 2426-2431, Nov. 2006.

- [5] J. Bai, J. Catala and G.-Q. Lu, "Comparative thermal and thermomechanical analyses of solder bump and direct solder bonded power device packages having double sided cooling capability", IEEE Conference Proceeding, Applied Power Electronics Conference, vol. 1, pp. 1240-1246, Feb. 2004.

- [5] Rohm And Haas Company, "Intervia viafill acid copper electroplating", Sep. 2007.

- [6] Prolectro Company, "Rubin T-200".

- [7] P. L. Taberna, S. Mitra, P. Poizot, P. Simon and J. M. Tarascon, "High rate capabilities Fe3O4 based Cu nano-architectured electrodes for lithium-ion battery applications", www.nature.com/naturematerials, Jun. 2006.

- [8] N.H. Basavanhally, R.A. Cirelli and O.D. Lopez, "High density nanostructured interconnection", European Patent Application, Oct. 2005.

- [9] S. Fiedler, M. Zwanzig, R. Schmidt, E. Auerswald, M. Klein, W. Scheel, and H. Reichl, "Evaluation of metallic nano-lawn structures for application in microelectronic packaging", IEEE System Integration Technology Conference, Dresden, Germany, 2006.

- [10] R.-J. Lin, Y.-Y. Hsu, Y.-C. Chen, S.-Y. Cheng and R.-H. Uang, "Fabrication of nanowire anisotropic conductive film for ultra-fine pitch flip chip interconnection", IEEE Electronic Components and Technology Conference, 2005.

- [11] E.C.Walter, M.P. Zach, F. Favier, B.J. Murray, K. Inazu, J.C. Hemminger and R.M. Penner "Metal nanowire arrays by electrodeposition" Chemphyschem, pp. 134-138, 2003.

- [12] S.H. Le, A. Camerlingo, H.T.M. Pham, B. Rejaeil and P.M. Sarro, "Anodic aluminum oxide templates for nanocapacitor array fabrication", pp. 96-100.

- [13] H. Masuda and K. Fukuda, Science, 1995.

- [14] L. Cagnon "Alumine nanoporeuse: fabrication et application à l'élaboration de nanofils par voie électrochimique", Nov. 2006.

- [15] Mouser Electronics Company, www.mouser.com.

- [16] Dupont Electronics Company, www2.dupont.com, "Dupont Riston Platemaster PM200", Apr. 2006.