#### Design and Simulation of a planar anode GTO thyristor on SiC

Pierre Brosselard<sup>a, b</sup>, Dominique Planson<sup>b</sup>, Sigo Scharnholz<sup>a</sup>, Volker Zorngiebel<sup>a</sup>, Mihai Lazar<sup>b</sup>, Christophe Raynaud, Jean-Pierre Chante<sup>b</sup> and Emil Spahn<sup>a</sup>

a) French-German Research Institute of Saint Louis (ISL), B.P. 34, F-68301 Saint Louis cédex, France b) Centre de Génie Electrique de Lyon (CEGELY) INSA-Lyon, UMR 5005 CNRS, Bat. Léonard de Vinci, 20 av. Albert Einstein, F-69621 Villeurbanne, France

Tel.: (+33) 4 72 43 87 24, Fax: (+33) 4 72 43 85 30 corresponding author : brossela@cegely.insalyon.fr

#### Summary :

4H-SiC asymmetrical gate turn-off (GTO) thyristors have been simulated using the finite element code MEDICI<sup>TM</sup>. The goal of these numerical simulations is a performance analysis of GTO SiC-thyristors having a planar anode. One advantage over the conventional etched anode structure is the avoidance of lithography related problems appearing in the recessed gate groove. From a performance point of view the planar anode and gate geometries allow smaller distances and hence lower specific on-resistance as well as a higher dI/dt. After a detailed description of simulation tool, models used and their parameters, this paper focuses on the dV/dt sensitivity, on the blocking voltage attainable with JTE and on the influence of the geometry on the switchingon. Finally the results will be compared to recessed gate GTO thyristors on SiC.

#### Introduction :

Like others [1, 2] we have been developing etched gate turn-off (GTO) thyristors on 4H-SiC [3, 4], featuring a recessed gate structure. The electrical results are very encouraging for future high power semiconducting devices based on silicon carbide (SiC). For the etched thyristor, the anode and the gate are not in the same plane (cf. figure n°1). So, in particular interdigitated structures with small for dimensions, it is a problem to realize contacts in the gate groove. The goal of this paper is to give a performance analysis of GTO SiCthyristors with the anode and the gate on the same plane. The technological solution is to develop the  $p^+$  level of the anode by ion implantation (cf. figure  $n^{\circ}1$ ). In the following, this type of thyristor structure is referred to as "planar" thyristor. In figure 1 and 2, we can

see the device termination is realized by mesa and an additional junction termination extension (JTE). After a detailed description of the models applied and the parameters entered when using the finite element code MEDICI<sup>TM</sup>, we show results obtained by the numerical simulations. Subsequently, a second part describes the effectiveness of the peripheral protection and gives the parameters to be used for the technological realization.

#### About the simulator $MEDICI^{TM}$ :

MEDICI<sup>TM</sup> is a finite element code solving at each mesh node the continuity equations and the Poisson's equation. A model is used for the mobility and is described by equation n°1.

$$\mu_{n,p}(x,y) = MUn, p.MIN + \frac{MUn, p.MAX(\frac{1}{300})^{MUn, p} - MUn, p.MIN}{1 + \left(\frac{T}{300}\right)^{Xln, p} \left(\frac{N_{total}(x,y)}{NREFn, p}\right)^{ALPHAn, p}}$$

(1)

$N_{total}(x,y)$  : level doping [cm<sup>-3</sup>]

In reverse bias, another model is used for the high electrical field with a specified saturation velocity equals to  $2 \times 10^7 \text{ V} \cdot \text{cm}^{-1}$ . The mobility at high electrical field is modelled by the equation n° 2.

$$\mu_{n,p}(\mathbf{x},\mathbf{y}) = \frac{\text{mun,p0}}{\left[1 + \left(\frac{\text{mun,p0.E}_{p}(\mathbf{x},\mathbf{y})}{\mathbf{v}_{\text{satn,p}}}\right)^{\text{Betan,p}}\right]^{\frac{1}{\text{Betan,p}}}}$$

(2)

$E_p(x,y)$  : electrical field module perpendicular to the conduction path

$V_{satn,p}$ : saturation velocity is  $2 \times 10^7 \, V \cdot cm^{-1}$ The carrier lifetime depends on the doping level and its expression is:

$$\tau_{n,p}(x,y) = \frac{TAUn,p0}{\left(1 + \frac{N(x,y)}{NSRHn,p}\right)}$$

(3)

For the impact ionisation, the model is described by the equation  $n^{\circ}4$ .

$$\alpha_{n,p}(\mathbf{x},\mathbf{y}) = n, p.IONIZA.e^{\left(\frac{E_{cnp}}{E_{para}(\mathbf{x},\mathbf{y})}\right)}$$

(4)

$E_{P_{ara}}(x,y)$  : electrical field module parallel to the conduction.

We used the Schokley, Read, Hall statistic to calculate the generation and recombination of the carriers.

The parameters used in the different models and their values applied are listed in table  $n^{\circ}1$ .

TABLE 1 : Parameter values used for different models

| nodels                                                |

|-------------------------------------------------------|

| Value                                                 |

| 947 cm <sup>2</sup> .V <sup>-1</sup> .s <sup>-1</sup> |

| 0                                                     |

| -1,962                                                |

| 0                                                     |

| 0.61                                                  |

| $1.94 \ 10^{17} \ \mathrm{cm}^{-3}$                   |

| $124[cm^2.V^{-1}.s^{-1}]$                             |

| $15.9 \text{ cm}^2.\text{V}^{-1}.\text{s}^{-1}$       |

| -1.434                                                |

| 0                                                     |

| 0.34                                                  |

| $1.76 \ 10^{19} \ \mathrm{cm}^{-3}$                   |

| $500 \text{ cm}^2.\text{V}^{-1}.\text{s}^{-1}$        |

| 167 cm <sup>2</sup> .V <sup>-1</sup> .s <sup>-1</sup> |

| 500 ns                                                |

| 100 ns                                                |

| $10^{30} \mathrm{cm}^{-3}$                            |

| $10^{30} \mathrm{cm}^{-3}$                            |

| $4,08\ 10^5\ \mathrm{cm}^{-1}$                        |

| $1,67 \ 10^7 \ \text{V.cm}^{-1}$                      |

| $1,63 \ 10^7 \ \mathrm{cm}^{-1}$                      |

| $1,67 \ 10^7 \ \text{V.cm}^{-1}$                      |

|                                                       |

# Thyristor structures:

For the first thyristors realized by V. Zorngiebel et al. [3], the gate was obtained by etching a part of the P<sup>+</sup> epilayer (c.f. fig. n°1.). So the gate and the anode are not on the same plane, making the realization of the gate contact in the groove difficult, especially for highly interdigitated structures. To avoid this problem, the anode could be realized by ion implantation (cf. fig. n°2). The planar

thyristor can be realized using an N<sup>+</sup> wafer and only 3 epilayers (PP<sup>-</sup>N).

| $ \begin{array}{c c} Gate & Anode & Gate \\ \hline Epi P^+ J_1 \\ \hline N^+ & Epitaxy N \\ \hline J_2 \end{array} $ | Gate Anode Gate<br>$I_1 \to I_2$<br>$I_2 \to I_2$ |

|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Epitaxy P-                                                                                                           | Epitaxy P-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Epitaxy P                                                                                                            | Epitaxy P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| J <sub>3</sub><br>Wafer N <sup>+</sup>                                                                               | J <sub>3</sub><br>Wafer N <sup>+</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Cathode                                                                                                              | Cathode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Fig. 1 : Schematic of<br>etched thyristor<br>structure                                                               | Fig. 2 : Schematic of<br>planar thyristor<br>structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

# Simulation results:

Before dealing with the forward blocking state we present simulation results revealing the conditions necessary to switch-on the planar thyristor.

Switch on conditions:

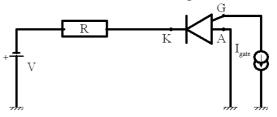

If a positive anode cathode voltage  $V_{AK} = E$  (cf. Fig. 3) is applied, the two outer junctions are forward biased (J<sub>1</sub> and J<sub>3</sub>), and junction J<sub>2</sub> is reverse biased. This state is called the forward blocking state. To switch on the thyristor, a negative gate current must be injected. A resistance R is used to limit the cathode current in the simulation circuit shown in figure n°3.

Fig. 3 : Electrical circuit

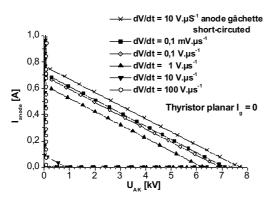

First, simulations were carried out to see the effect of the  $\frac{dV}{dt}$ . Figure n°4 shows to which extend the breakover voltage depends on the  $\frac{dV}{dt}$ . If the  $\frac{dV}{dt}$  increases the breakover voltage decreases. At low voltages, junction J<sub>2</sub> is reverse biased. The junction capacitance was estimated by frequency simulations to be around  $C = 10^{-15} \text{ F} \cdot \text{m}^{-1}$ . For  $\frac{dV}{dt} = 10 \text{ V} \cdot \mu \text{s}^{-1}$  the product  $C \cdot \frac{dV}{dt}$  equals to  $10^{-7} \text{ A} \cdot \text{m}^{-1}$ . So it is sufficient to switch the thyristor to on-state

# Fig. 4 : Electrical characteristics of the planar thyristor for different $\frac{dV}{dt}$

In summary, these simulations show that the dV/dt must be lower than 0.1 V.µs<sup>-1</sup>, to avoid dV/dt related switch-on of the thyristor.

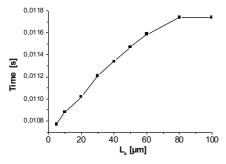

In order to reveal the influence of the anode length on the turn-on time the same simulation circuit is used with a  $4 \text{ k}\Omega$  resistance and a 300 V voltage source. The gate current is a 24 ms pulse. Its maximal value equals to 0.1 mA. The surface of the structure is constant.

The simulation shows that the switching time decreases if the anode length decreases (see Fig. 5).

Fig. 5 : Switching time versus La

Other simulations with varying gate contact width or gate-anode distance  $L_G$  (figure n°2) revealed no change of the switching time for the planar thyristor.

# Forward blocking state :

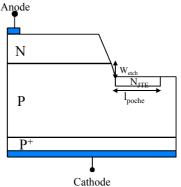

The purpose of the following simulations is to investigate device terminations supporting the blocking junction n°2. For reasons of calculation time needed, the simulation structure used is based on a simple NP<sup>-</sup>P diode structure which is shown in figure n°6.

The doping level and the thickness of the P<sup>-</sup> epilayer were determined by semi infinite junction simulations (onedimensional NP<sup>-</sup>P structure). The breakdown voltage obtained by simulation is 7.9 kV for a 50  $\mu$ m epilayer with a doping level equal to 1×10<sup>15</sup> cm<sup>-3</sup>.

Fig. 6 : NP<sup>-</sup>P structure diode

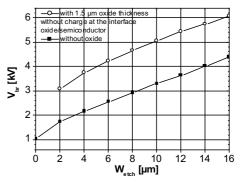

Two types of device terminations have been developed : mesa (cf. figure n°6) and a combination between mesa and JTE (Junction Termination Extension). For the mesa protection, only one parameter, the etching depth ( $W_{etch}$ ) is be optimized. In figure n°7, the breakdown voltage versus  $W_{etch}$  is represented. Note that  $W_{etch}$  is the relative etch depth with respect to J<sub>2</sub>.

Fig. 7 : Breakdown voltage versus mesa etching depth

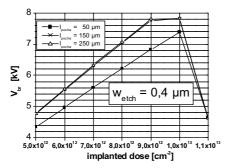

To obtain an efficiency of 50 % or more for the mesa termination (4 kV), the etching depth must be greater than 14 µm. With an RIE process etched with typical speed 100 nm/min, the time would be very long (140 min). Therefore, simulations are performed with an implanted JTE region. The results are shown in figure n°8. The simulations are realized for 0.4 µm etching depth. The breakdown voltage depends on the JTE length but for a length greater than 150 µm, the voltage does not change. As can be seen, the attainable forward blocking voltage is maximal in a small between  $9 \times 10^{12}$ cm<sup>-2</sup> range and  $1 \times 10^{13}$  cm<sup>-2</sup>.

# Fig. 8 : Breakdown voltage versus implanted dose in JTE for different lengths

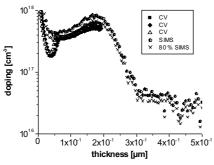

Therefore, it is very important to accurately adjust the implanted dose. Furthermore, because of the sensitivity of the forward blocking voltage on the doping concentration, it is very important to know the exact number of implanted atoms being electrically activated. By comparing CV with SIMS data, Fig 9 indicates 80 % activation of a nitrogen implanted and annealed (1700°C / 30 mn) region on 4H-SiC.

Fig. 9 : N type doping versus the thickness

#### Conclusion:

Based on numerical simulations using MEDICI<sup>TM</sup>, a planar anode SiC-thyristor was simulated with the aim to improve the trade-off between switching behaviour and blocking features. Voltage transient related turn-on is expected for dV/dt rates in  $0.1 \text{ V} \cdot \mu \text{s}^{-1}$ . excess of While the advantageous planar structure gains from the reduction of the anode length in terms of a reduced turn-on time, the anode gate distance and gate width have no influence on the switching speed.

Using a simple mesa termination efforts an etching depth of more than 14  $\mu$ m to guarantee 50 % of the theoretical blocking voltage. JTE, on the other hand, efforts a proper adjustment of the electrically active dopants. The simulations made indicate the optimal dose being in the range of 0.9 to  $1 \times 10^{13}$  cm<sup>-2</sup>. Having only 80 % electrical activation the dose used in the impantation process has to be 1.12 to  $1.25 \times 10^{13}$  cm<sup>-2</sup>. *Reference :*

[1] : S. V. Campen, A. Ezis, J. Zingaro, G. Storaska, R. C. Clarke, K. Elliott, V. Temple, D. Hits, M. Thompson, K. Roe, and T. Hansen, "100 A and 3.1 kV 4H-SiC GTO Thyristors," presented at IEEE Lester Eastman Conf. on High Performance Devices, University of Delaware, Newark, DE, USA, 2002.

[2] : S.-H. Ryu, A. K. Agarwal, R. Singh, and a. J. W. Palmour, "3100 V, Asymmetrical, gate Turn-Off (GTO) Thyristors in 4H-SiC," *IEEE Electron. Device Lett.*, vol. 22, pp. 127-129, 2001.

[3] : V. Zorngiebel, S. Scharnholz, E. Spahn, P. Brosselard, N. Arssi, J.-P. Chante, D. Planson, C. Raynaud, B. Spangenberg, and H. Kurz, "Fabrication and Characterisation of High Voltage SiC-Thyristors", presented at 4th European Conf. on SiC and Related Materials (ECSCRM), Linköping, Sweden, 1-5 Sept. 2002.

[4] : S. Scharnholz, V. Zorngiebel, P. Brosselard, and E. Spahn, "Silicon carbide thyristors for pulsed power applications", in IEE Proc. of the 1st European Pulsed Power Symposium (EPPS), , Saint Louis, France, 22-24 October 2002, pp. 14/1-14/6.