# ULTRA FINE PITCH FLAT PANEL DISPLAY PACKAGING USING $3\mu m$ CONDUCTIVE PARTICLES

G.-J. Wang, Yi-Chin Lin, Gwo-Sen Lin

# ▶ To cite this version:

G.-J. Wang, Yi-Chin Lin, Gwo-Sen Lin. ULTRA FINE PITCH FLAT PANEL DISPLAY PACKAGING USING  $3\mu \rm m$  CONDUCTIVE PARTICLES. DTIP 2006, Apr 2006, Stresa, Lago Maggiore, Italy. 5 p. hal-00189250

HAL Id: hal-00189250

https://hal.science/hal-00189250

Submitted on 20 Nov 2007

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# ULTRA FINE PITCH FLAT PANEL DISPLAY PACKAGING USING 3μm CONDUCTIVE PARTICLES

Gou-Jen Wang<sup>1</sup>, Yi-Chin Lin<sup>2</sup> and Gwo-Sen Lin<sup>3</sup>

<sup>1,2</sup> Department of Mechanical Engineering, National Chung-Hsing University, Taiwan <sup>3</sup> Wintek Inc., Taiwan

#### **ABSTRACT**

In this research, dependency of the hardness of the gold bump and process parameters such as the contact area and the load pressure on the contact resistance of the extra fine pitch chip-on-glass (COG) flat panel display (FPD) packaging is investigated. The FJ2530 anisotropic conductive film (ACF) by Sony Inc. containing the currently smallest 3µm conductive particles implemented to conduct the experiments. Feasibility of the 3µm ACF in ultra-fine pitch COG applications is further examined. Form the experimental results, we found that no special process is required to obtain a satisfied contact resistance for the ultra fine pitch packaging based on the 3µm conductive particles. It can be concluded that the combination of the 3µm conductive particles and the IC gold bumps with hardness 70Hv can lead to a miniaturized device with less cost. For mass production, test sample with pitch space being larger than 10μm is suggested to retain a better reliability.

#### 1. INTRODUCTION

In the past few years, cellular phone becomes one of the key necessities in our daily life. Increasing demands from the customs in higher quality products give an influential impetus to the progress of the components. The resolution of the panel that is the major index of quality is thus required raising unceasingly.

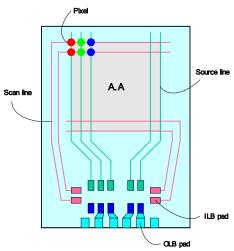

The number of pixels in each square inch of a flat panel display (FDP) determines its resolution. A pixel is defined by the crossing of a horizontal scan line and a vertical source line which are connected to the inner lead bonding (ILB) pads (Figure 1). The ILB pads are the contact pads to bond with the controller IC. To increase a FPD's resolution, denser layouts of the scan lines and source lines are required, and the channels of its controller IC have to be increased. More advanced

packaging techniques using more minute conductive particles are thus desired to precisely connect the controller IC to the interface. The conductive particles, metallic particles or metal-coated polymer balls, combining with the adhesive resin to fix them is named anisotropic conductive film (ACF). The ACFs are the key materials for fine pitch chip-on-glass (COG) FPD packaging [1].

Most of the currently used ACFs consist of conductive particles having diameter larger than 4 $\mu$ m. The conductive particles serve as the conductive paths connecting the gold bumps of the controller IC and the ITO electrode, distributing uniformly between the controller IC and the electrode after packaging. This gives rise to a high possibility of short circuit. For packaging with line width and line pitch being less than  $40\mu$ m,  $4\mu$ m conductive particles cause almost no short circuit. However, the short circuit problems are highly liable to occur when the process is advanced to  $30\mu$ m.

Jeng and Hsieh [2] added the metal-coated polymer material to the gold bumps or the electrode to replace the ACF, trying to deal with the short circuit problems in fine pitch FPD packaging. High contact resistance limits its application in COG based packaging.

Hsu and Liu [3] suggested the thermo-sonic flip-chip method, using ultrasonic energy to eutectic bond connections between chip and substrate. Since the flip-chip bonding operates in a relatively higher temperature, the structure of the ITO crystals is likely to be damaged, making changes in resistance. In addition, successful sputtering of a metal that can melt with the gold bumps on the ITO electrode needs to overcome the adhesion problem in the first place.

Yim et al. [4] used a dual layers structure to investigate the feasibility of the  $4\mu m$  ACF in ultra-fine pitch ( $10\mu m$  clearance) COG applications. The upper layer is a non-conductive film (NCF) with good fluidity. During bonding the correlation of fluidity between the upper NCF and the lower ACF is very small; therefore,

the conduct particles become more immobile and aggregate around the bumps.

Chan et al. [5] investigated the influences of the bonding parameters of the ACF interconnection with reflow treatment on the contact resistance. It was found that the contact resistance increases along with the increase in the peak temperature of the reflow profile. The ACF adhesive assemblies with Au bump has higher contact resistance than that of the Ni/Au bump after reflow due to a higher thermal stress in the *z*-direction. The cause of the higher thermal stress is that the Au bump is higher than the Ni/Au bump.

Figure 1. Dependency of FPD resolution on IC channels

For the above articles, the influence of the hardness of the gold bump and other process parameters such as the contact area and the load pressure on the contact resistance has not been studied yet. Moreover, as aforementioned the currently industrial applied ACFs consist of conductive particles with diameter being larger than  $4\mu m$ . More advanced packaging techniques using more minute conductive particles are continuingly desired from the FPD industry.

The main goal of this research is to investigate the dependency of the hardness of the gold bump and process parameters such as the contact area and the load pressure on the contact resistance of the extra fine pitch COG based FPD packaging. The FJ2530 anisotropic conductive films (ACF) by Sony Inc. containing the currently smallest 3µm conductive particles are used to conduct the experiments. Feasibility of the 3µm ACF in ultra-fine pitch COG applications is further explored.

#### 2. DESIGN OF EXPERIMENT

#### 2.1 Principles of measurement

(1)Four-point probe method to measure resistivity

The four point probe method [6] that is commonly used to measure the resistivity of any semiconductor material was atopted to measurement the resistivity. The key advantage of the four point probe method is that the resistivity of the desired route can be accurately measured, without being influenced by others routes. In our applications, the measurement noise due to the ITO electrode can be effectively excluded.

(2) Insulation resistance test to estimate short-circuit rate

The insulation resistance (IR) test is implemented to

measure the short-circuit rate of each pair of adjacent

wirings.

# 2.2 Process components

#### (1) IC mask

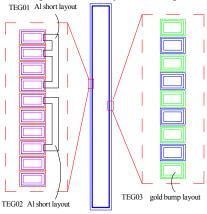

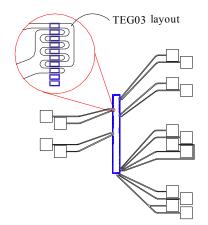

The layout of the IC mask depicted in Figure 2 is composed of 18 test element groups (TEG). Each TEG contains (i)TEG01: formed by 4 gold bumps with 3 of them being shorted circuit to examine the point contact resistance; (ii) TEG02: formed by 4 gold bumps with 2 of them being shorted circuit to investigate the resistance of individual insulating film; (iii)TEG03: formed by 8 separated gold bumps to observe the impressive load induced short circuit problem and the uniformity of pressure, ensuring the reliability of the inspecting points.

Figure 2. Layout of the IC mask

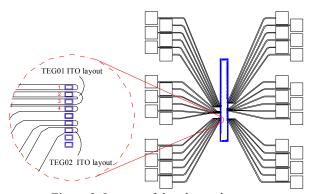

#### (2) ITO mask

The mask for ITO layout is a 300mm x 400mm chromium mask. Layout of the ITO is required to match that of the IC TEG01~03 to enable effective measurement of resistance. Therefore, the TEG layout of the ITO mask includes (1)TEG01: formed by 4 ITO routes, in which routes #3 and #4 were shorted (Figure 3); (2)TEG02: formed by 2 independent ITO routes to successfully examine the resistance of the insulating film; (3)TEG03: formed by 8 ITO routes with the odd numbers routes being shorted and the even number routes being shorted (Figure 4).

Figure 3. Layout of the glass substrate

Figure 4. Layout of the multi insulating routes

## (3) Anisotropic conductive film

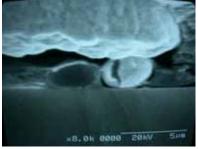

The AFC used in this research is the FJ2530 provided by Sony Inc. with 25 $\mu$ m in thickness and 3.0mm in width. The conductive particles inside the AFC are the currently smallest 3 $\mu$ m particles. Figure 5 is the SEM image of the cross section of the 3 $\mu$ m conductive particle.

Figure 5. SEM image of the  $3\mu m$  conductive particles

#### (4) Glass substrate

The glass/SiO<sub>2</sub>/ITO substrate made by Wintek Inc. was selected to be the glass substrate. Properties of the ITO substrate include: dimension=300mm x 400mm, ITO film thickness =  $4500\text{\AA}$ , and sheet resistance =  $4.5\Omega$ /square.

#### 2.4 Process parameters

In order to explore the effects of different process parameters on the contact resistance of the  $3\mu m$  conductive particles, hardness of gold bump, load pressure, contact area, and pitch space are selected as the process parameters for the experiments. Table 1 tabularizes the settings of these parameters. The load pressure is for examining the degree of deformation of the conductive particles under different bonding pressures; the contact area is selected to testify the inverse proportion dependency of the contact resistance on the contact area; the pitch space is used to detect the minimum pitch space that can prevent the short circuit problems from happening.

### 2.5 Equipments

The Sintex IC main bonder that consists of a 20mm x 15mm bonding head, a glass holding bonding stage, and an aligning system is implemented to conduct the experiments. The experimental procedures include aligning the ITO layout with the gold bumps, heating the bonding head to 300°C, and bonding the device by applying different loading pressures for 12 seconds.

#### 3. RESULTS AND DISCUSSIONS

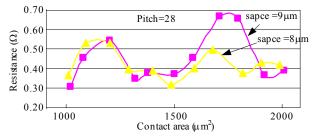

#### 3.1 Contact resistance vs. contact area

Theoretically, the contact resistance is inversely proportional to the contact area. However the experimental results shown in Figure 6 do not coincide with the theoretical tendency. The first reason is presumed that the variations of the contact area for experiments are not large enough to reveal the tendency. Increasing the contact area of the test sample may solve this problem. Nevertheless it is against the demand of miniaturization. Secondly, the conductive particles are expected to distribute uniformly. In reality, the particles stay at the effective conductive area do not spread uniformly owing to the flow and compression of the resin during bonding. It is more crucial in the ultra fine pitch packaging. Variations of the amount of conductive particles on different test pads lead to the uniformity.

Figure 6. Contact resistance as a function contact area

# 3.2 Matrix analysis

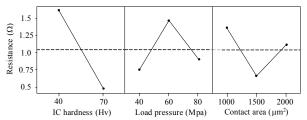

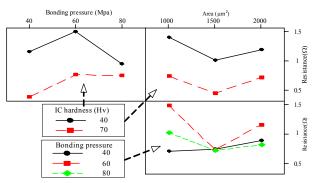

To further investigate the dependencies of contact resistance on different process parameters, experiments which cover all combinations of the hardness of gold bump, load pressure, and contact area are executed. Experimental results are illustrated in Figure 7 and 8. It is found from Figure 7 that the gold bump with 70Hv in hardness leads to a lower contact resistance, compared to the 40Hv gold bump. According to the results of the matrix analysis, the influence ratio of the hardness factor on the resistance is 13.57%. For the load pressure, the 40MPa loading produces a lower contact resistance. The influence ratio of the load pressure is 1.96%. Similarly, a lower resistance is observed when the contact area is 1500 µm<sup>2</sup>. The influence ratio of the contact area is 1.96%. Figure 8 is produced to investigate the mutual influences among the process parameters. As the load pressure and hardness of gold bump are the controlled parameters, experimental results show that both the parameter combinations (70Hv, 60MPa) and (70Hv, 80MPa) can induce a lower contact resistance. The percentage of crossover between these two parameters is 1.47%. When the hardness and contact area are chosen as the controlled variables, the parameter setting of (70Hv, 1500µm<sup>2</sup>) results in a lower resistance. The percentage of crossover between the hardness and the contact area is 0.14%. The parameter setting of (60MPa, 1500µm<sup>2</sup>) leads to a lower resistance, when the load pressure and contact area are the controlled parameters. The percentage of crossover between the load pressure and contact area is 0.84%.

The above analyses imply that no special process is required to obtain a satisfied contact resistance for the ultra fine pitch packaging based on the  $3\mu m$  conductive particles. All the parameter setting combinations of Table 1 are able to produce acceptable contact resistance.

Figure 7. Matrix analysis of process parameters

Figure 8. Matrix analysis of mutual influences

# 3.3 Short circuit rate investigation

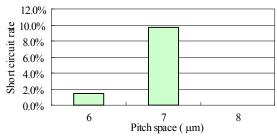

As the  $3\mu m$  conductive particles are employed, the insulation problem becomes more crucial. Test samples with different pitch spaces are applied to examine the minimum pitch space that can ensure electrical insulation. Figure 9 illustrates that a test sample with pitch space of  $7\mu m$  can not prevent the short circuit problem from happening. The main reason is that the  $7\mu m$  pitch space can only accommodate 2 or less conductive particles, leading to a higher possibility of short circuit. For mass production, test sample with pitch space being larger than  $10\mu m$  is suggested to retain a better reliability.

Figure 9. The relationship between the short circuit rate and the pitch space

#### 4. CONCLUSIONS

In this research, experiments of the extra fine pitch chipon-glass (COG) flat panel display (FPD) packaging based on the FJ2530 anisotropic conductive film (ACF) by Sony Inc. containing the currently smallest  $3\mu m$  conductive particles are carried out.

The dependencies of the hardness of the gold bump and process parameters such as the contact area and the load pressure on the contact resistance are experimentally investigated.

Experimental results indicate that the gold bump with 70Hv in hardness leads to a lower contact resistance, compared to the 40Hv gold bump. It is also found that no special process is required to obtain a satisfied contact resistance for the ultra fine pitch packaging based on the

$3\mu m$  conductive particles. The combined resistance of the  $3\mu m$  conductive particles and the IC gold bumps with hardness 70Hv after packaging is far less than that of the indium tin oxide (ITO) electrode. It can be concluded that the combination of the  $3\mu m$  conductive particles and the IC gold bumps with hardness 70Hv can lead to a miniaturized device with less cost. For mass production, test sample with pitch space being larger than  $10\mu m$  is suggested to retain a better reliability.

#### REFERENCES

- [1] P. Savolainen, "<u>Display driver packaging: ACF reaching the limits?</u>,", Proceeding of the IEEE 9<sup>th</sup> Int'l Symposium on Advanced Packaging Materials, pp. 7-10, 2004.

- [2]J. H. Jeng and T. E. Hsieh, "Application of Al/PI Composite Bumps to COG Bonding Process", IEEE Tran. on

- Components and Packaging Technology, Vol. 24, No. 2, pp. 271-278, 2001.

- [3]C. P. Hsu and C. H. Liu, "The Process and Equipment Technology of the Thermosonic Flip-Chip Bonding," Journal of the Mechanical Industry, Vol. 258, pp. 218-228, 2004.

- [4] M. J. Yim\*, J. Hwang, and K. W. Paik, "Anisotropic Conductive Films (ACFs) for Ultra-Fine Pitch Chip-On-Glass (COG) Applications", Proceeding of the IEEE 10<sup>th</sup> Int'l Symposium on Advanced Packaging Materials, Irvine, CA, USA, pp. 181-186, 2005.

- [5] C. Y. Chan, M. O. Alam, C. Bailey and H. Lu, "Effect of Bump Characteristics and Temperature Variation on the Online Contact Resistance of Anisotropic Conductive Joints", Microelectronics Reliability, 43, pp. 625-633, 2003.

- [6] P. J. H, Dobbs and F. S. Kovacs, "Solid State Technology," Vol. 7, No. 8, pp. 28, 1964.

Table 1. Process parameters setting combinations

|   | Parameter | gold | ess of<br>bump<br>(v) | Load pressu<br>(Mpa) |    |    | C     | ontact are (µm²) | ea    | ] | Pitch<br>(µ | space<br>m) | e |

|---|-----------|------|-----------------------|----------------------|----|----|-------|------------------|-------|---|-------------|-------------|---|

| ĺ | Settings  | 40   | 70                    | 40                   | 60 | 80 | 1,000 | 1,500            | 2,000 | 6 | 7           | 8           | 9 |