# Systematic Figure of Merit Computation for the Design of Pipeline ADC

Ludovic Barrandon, Samuel Crand, Dominique Houzet

## ▶ To cite this version:

Ludovic Barrandon, Samuel Crand, Dominique Houzet. Systematic Figure of Merit Computation for the Design of Pipeline ADC. DATE'05, Mar 2005, Munich, Germany. pp.277-278. hal-00181528

HAL Id: hal-00181528

https://hal.science/hal-00181528

Submitted on 24 Oct 2007

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Systematic Figure of Merit Computation for the Design of Pipeline ADC

L. Barrandon, S. Crand, D. Houzet IETR, Université de Rennes 1, Avenue du Général Leclerc, 35042 RENNES Cedex, France ludovic.barrandon@univ-rennes1.fr

#### **Abstract**

The emerging concept of SoC-AMS leads to research new top-down methodologies to aid systems designers in sizing analog and mixed devices. This work applies this idea to the high-level optimization of pipeline ADC. Considering a given technology, it consists in comparing different configurations according to their imperfections and their architectures without FFT computation or time-consuming simulations. The final selection is based on a figure of merit.

### 1. Introduction

The evolution of analog and mixed designs and the increasing complexity of such devices lead to develop methodologies using top-down techniques. To illustrate this concept, we have chosen to focus on the performances evaluation of pipeline ADC devices. The aim is to compute a figure of merit (FOM), which consists in integrating various characteristics into a single parameter, to determine the best compromise while matching specifications. Basic constraints consist in saving computation time by avoiding the use of behavioral or electrical level simulations and FFT analysis.

## 2. Figure of merit adjustment

## 2.1 Definition

This FOM is an example adapted here to software defined radio systems where spectral performances (SNDR and SFDR) are dominant [2]. The number of comparators (*Comp*) represents a relative evaluation of the die area and other parameters like the number of residue amplifiers or the evaluation of the power consumption could be considered:

$$\begin{split} FOM &= \delta \Bigg[ \alpha \Bigg( \frac{SNDR}{SNDR_{\max}} \Bigg) + \beta \Bigg( \frac{SFDR}{SFDR_{\max}} \Bigg) + \gamma \Bigg( \frac{Comp_{\min}}{Comp} \Bigg) \Bigg] \\ \alpha &= SNDR_{\lim} / SNDR_{\max} \\ \beta &= SFDR_{\lim} / SFDR_{\max} \\ \delta &= 1/\big[ 3.(\alpha + \beta + \gamma) \big] \end{split}$$

$\delta$  is computed to obtain 0 < FOM < 1

The indices *max* and *min* indicate the optimal values (ideal case) and the indices *lim* represent the desired extrema which the ADC should meet for a given application.

## 2.2 Evaluation of the performances

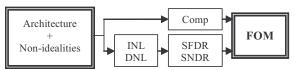

Figure 1. Methodology of evaluation of the performances

Among the different non-idealities of a pipeline ADC stage, only two of them are not corrected by the redundant sign digit (RSD) method: the residue amplification mismatch and the non-linearity of this amplification, whereas offset mismatch on the comparator conversion steps are corrected inside the limit defined as  $1/V_{\rm ref.}2^{\rm Ni+1}$  [2].

**Gain mismatch**: The transfer function  $TF_{\varepsilon}$ , taking into account a relative gain mismatch  $\varepsilon_{gain}$ , is defined from the ideal transfer function TF as follows:

$$TF_{\varepsilon} = (1 + \varepsilon_{gain}) \cdot TF$$

**Non-linearity**: The non-linearity is modeled with a reverse hyperbolic tangent function [3]. The equation used is:

$$\mathit{TF}_{\mathit{NL}} = \frac{1}{\alpha_{\mathit{NL}}} \tanh^{-1} \bigl( \tanh \bigl( \alpha_{\mathit{NL}} \bigr) \mathit{TF} \bigr)$$

where  $\alpha_{NL}$  is a coefficient associated to the amplitude of the non linearity.  $1/\alpha_{NL}$  and  $\tanh(\alpha_{NL})$  are normalization factors.

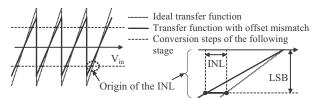

**INL calculation:** The INL is the difference between TF and the actual transfer function (figure 2).

Figure 2. Influence of gain and non-linearity mismatches of a single pipeline stage over the INL

The INL of a non ideal pipeline stage can be written as:

$$INL(i) = \left( \left( 1 - \varepsilon_{gain} \right) \left( \frac{1}{\alpha_{NL}} \tanh^{-1} \left( \tanh \left( \alpha_{NL} \right) x_i \right) \right) - x_i$$

where  $x_i$  is the ideal position of the  $i^{th}$  conversion step and INL(i) is the INL corresponding to  $x_i$ . Then, the global INL of a pipeline ADC is the sum of the contributions of each single stage to this INL.

#### **SNDR** calculation from INL:

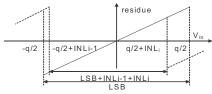

Figure 3. Conversion error for the  $i^{\text{th}}$  code with and without INL

The SNDR is computed from the mean quadratic error of a non-ideally-quantized sine wave, that is to say adding INL to the ideal conversion steps (figure 3):

$$\begin{split} \overline{\varepsilon_{i}^{2}} &= \frac{1}{q} \int_{-q/2+INL_{i-1}}^{q/2+INL_{i}} V_{in}^{2} dV_{in} = \frac{1}{3q} \left[ \left( \frac{q}{2} + INL_{i} \right)^{3} + \left( \frac{q}{2} - INL_{i-1} \right)^{3} \right] \\ &= \frac{q^{2}}{12} + \frac{q}{4} \left( INL_{i} - INL_{i-1} \right) + \frac{1}{2} \left( INL_{i}^{2} + INL_{i-1}^{2} \right) + \frac{1}{3q} \left( INL_{i}^{3} - INL_{i-1}^{3} \right) \end{split}$$

where  $q^2/12$  is equal to the well-known conversion noise for an ideal ADC. Then, the SNDR of an N-bit ADC becomes:

$$SNDR = 20.\log\left(\frac{V_{ref}^2/2}{\overline{\varepsilon^2}/2^N}\right)$$

with  $\overline{\varepsilon^2} = \sum_i \overline{\varepsilon_i^2}$

**SFDR calculation from INL**: In [4], the levels of the harmonics of an ideally-quantized sine-wave are computed from Fourier series expansion:

$$a_k = \frac{2}{\pi k} \sum_{i=1}^{2^n} y_i \left[ \sin(k \cdot \cos^{-1}(x_i)) - \sin(k \cdot \cos^{-1}(x_{i+1})) \right]$$

where  $x_i$  are the thresholds and  $y_i=(x_i+x_{i+1})/2$ . The originality of this work is to add the DNL to the ideal quantization steps. The SFDR is the highest harmonic level given by:

$$HD_k \equiv 20.\log(|a_k/a_1|) dB_c$$

# 3. Results and interpretations

In this study, pipeline ADC use the RSD method to enable digital correction [2]. The use of 1.5-bit stages is allowed, except for the first stage (where digital correction is inefficient as the output varies from -FS/2 to FS/2 with a full-scale input) and for the last stage which is a simple flash ADC. Table 1 presents the extrema obtained with the FOM program for 10-bit ADC (1596 possibilities) with:

$$\varepsilon_{gain} = -1.5\%$$

;  $\alpha_{NL} = 0.2$

$Comp_{lim} = 60 = 12\%$  of  $Comp_{max}$

$SFDR_{lim} = 75 \text{dB} = 88\%$  of  $SFDR_{max}$

$SNDR_{lim} = 56 dB = 90\% \text{ of } SNDR_{max}$

|                             | Comp | SNR(dB) | ENOB(Bits) | SFDR(dB) | FOM  |

|-----------------------------|------|---------|------------|----------|------|

| 2/2/2/7                     | 136  | 49,7    | 7,97       | 81,7     | 0,77 |

| 2/9                         | 514  | 53,0    | 8,51       | 84,5     | 0,79 |

| 2/2/2/2/2/2/2/2             | 27   | 49,4    | 7,91       | 79,7     | 0,85 |

| 9/2                         | 514  | 62,0    | 10,00      | 84,6     | 0,85 |

| 2/1.5/2/2/2/2/2/1.5/2       | 25   | 51,0    | 8,17       | 79,1     | 0,87 |

| 2/1.5/1.5/1.5/1.5/1.5/1.5/2 | 20   | 52,9    | 8,49       | 84,9     | 0,94 |

| 4/1.5/1.5/2/1.5/1.5/2       | 29   | 60,0    | 9,68       | 86,7     | 0,95 |

| 3/1.5/1.5/1.5/1.5/1.5/2     | 22   | 57,5    | 9,26       | 85,9     | 0,96 |

$\alpha$ = 0.909;  $\beta$ = 0.885;  $\gamma$ = 0.333;  $\delta$ = 0.470

Table 1. Extrema obtained with the FOM program for 10-bit pipeline ADC

These results are representative of the following tendencies. 9/2 configuration is the closest to the flash architecture. Its performances are the best in terms of SNDR and SFDR but its number of comparators is also the largest. The architecture only composed of 2-bit stages has the worst performances. Nevertheless, thanks to its reduced number of comparators, this solution does not lead to the lowest FOM. The best architecture, according to the FOM, is an ADC composed of an N-bit front-end stage, with N an integer scaled according to  $\varepsilon_{gain}$  et  $\alpha_{NL}$  (i.e. N=3 for this case), followed by 1.5-bit stages and finished by a 2-bit stage. This analysis is confirmed for other resolutions and other values of  $\varepsilon_{gain}$  and  $\alpha_{NL}$ .

# 4. Conclusion and perspectives

This work presents an efficient way to exhaustively arrange pipeline architectures according to their estimated performances. This method is applicable to other analog or mixed devices with a SoC-AMS top-down design perspective [1]. It will be used to facilitate the exploration of the design space of the mixed front-end for software defined radio applications [5].

The main aspect which remains to develop is the estimation of  $\varepsilon_{gain}$  and  $\alpha_{NL}$  parameters according to actual technologies [3].

### References

- M. Vogels, G. Gielen "Figure of merit based selection of A/D converters", DATE 2003, CAD for Analogue Design, Design Methodologies and Physical Design p.1190

- [2] L. Sumanen, "Pipeline analog-to-digital converters for wideband wireless communications", Helsinki University of Technology Electronic Circuit Design, Report 35, 2002

- [3] P. Nuzzo, "Architectural Space Characterization of a Transconductance Amplifier", Università di Pisa, 2003

- [4] Hui Pan, "A 3.3-V, 12-bit, 50-MS/s A/D Converter in 0.6μm CMOS", University of California, Los Angeles, PhD thesis, 1999

- [5] L. Barrandon, S. Crand, D. Houzet, "Behavioral Modeling and Simulation of Mixed Signal Front-End for Software Defined Radio Terminals", ISIE 2004, Ajaccio – France