# A 4H-SiC high-power-density VJFET as controlled current limiter

Dominique Tournier, Philippe Godignon, Josep Montserrat, Dominique Planson, Christophe Raynaud, Jean-Pierre Chante, Jean-François de Palma, Franck Sarrus

### ▶ To cite this version:

Dominique Tournier, Philippe Godignon, Josep Montserrat, Dominique Planson, Christophe Raynaud, et al.. A 4H-SiC high-power-density VJFET as controlled current limiter. IEEE Transactions on Industry Applications, 2003, 39 (5), pp.1508-1513. hal-00140109

HAL Id: hal-00140109

https://hal.science/hal-00140109

Submitted on 6 Apr 2007

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## A 4H-SiC High-Power-Density VJFET as Controlled Current Limiter

Dominique Tournier, Philippe Godignon, Joseph Montserrat, Dominique Planson, Christophe Raynaud, Jean Pierre Chante, Jean-François de Palma, and Franck Sarrus

Abstract-Considering fault current limiters for serial protection, many structures exist, from regulation to other complex systems such as circuit breakers, mechanical switches, or more conventional fuses. Up to now, only a few semiconductor current limiter structures have been described in the literature. Although current-regulative diode components already exist, their voltage and current capabilities ( $V_{BR} = 100 \text{ V}$ ,  $I_{max} = 10 \text{ mA}$ ), do not allow their use in power systems. This paper presents both simulation study and experimental results of a bidirectional current limiter structure based on a vertical SiC VJFET. The device was designed for serial protection in order to limit  $I^2t$ value. Finite-element simulations were performed with ISE-TCAD software to design the device and evaluate its static electrical characteristics. Then, dynamic simulations were performed to underline current reduction ability and power losses adjustment by gate resistance value optimization. Finally, electrical characterization for a unidirectional and a bidirectional device were done up to 400 V. The measured specific on resistance  $R_{\mathrm{ON}}$  is in the range of 176 m $\Omega \cdot \text{cm}^2$ . Limiting capabilities have also been measured for a bidirectional device made of two unidirectional devices connected head to tail. The highest breakdown voltage value in "current limiting state" was measured to be  $\sim$ 810 V, corresponding to a high power density of 140 kW/cm<sup>2</sup>.

Index Terms—Command integration, current limiter, high voltage, JFET, serial protection device.

#### I. INTRODUCTION

THE SiC-semiconductor-based devices are suitable for high-current and high-voltage applications [1], [2]. A promising application of SiC-based devices is current limitation for power system protection [3], [4], which benefits from its high thermal conductivity and wide bandgap. Most silicon components realized in SiCs, Schottky diodes, MOSFETs, and MESFETs, show good electrical and thermal characteristics

Paper ICPSD-IAS 57–4, presented at the 2002 Industry Applications Society Annual Meeting, Pittsburgh, PA, October 13–18, and approved for publication in the IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS by the Power Systems Protection Committee of the IEEE Industry Applications Society. Manuscript submitted for review October 15, 2002 and released for publication May 27, 2003. This work was supported by Ferraz Shawmut and by the European Community under the Access to Research Infrastructure action of the Improving Human Potential Program.

- D. Tournier, P. Godignon, and J. Montserrat are with the Centro Nacional de Microelectronica, 08193 Bellatera, Spain (e-mail: Dominique.Tournier@cnm.es; Philippe.Godignon@cnm.es; Josep.Montserrat@cnm.es).

- D. Planson, C. Raynaud, and J. P. Chante are with the Centre de Génie Electrique de Lyon-INSA, 69621 Villeurbanne, France (e-mail: Planson@cegely.insa-lyon.fr; Raynaud@cegely.insa-lyon.fr; Chante@cegely.insa-lyon.fr).

- J.-F. de Palma is with Ferraz Shawmut, Inc., Newburyport, MA 01950-1930 USA (e-mail: jeanfrancois.depalma@ferrazshawmut.com).

- F. Sarrus is with Ferraz Shawmut, 69720 St Bonnet de Mure, France (e-mail: Franck.Sarrus@fr.ferrazshawmut.com).

Digital Object Identifier 10.1109/TIA.2003.816465

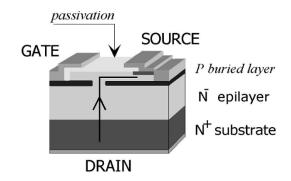

Fig. 1. Cross section of the VJFET.

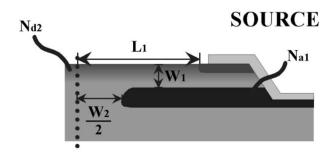

Fig. 2. VJFET parameters to be optimized.

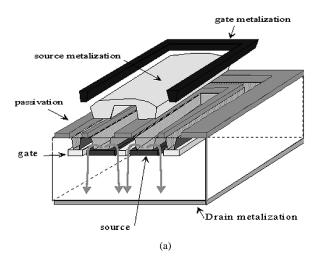

[2]. A few SiC current limiters were presented in [5] and [6]. This paper targets the design, manufacture, and characterization of a new VJFET (Fig. 1), which implements both gate and source in buried layers. In the steady state, the voltage drop across the component must be as low as possible. In the active state (limiting phase), the current limiter must sustain a high current, under high-voltage bias. The resulting high power density must not cause the component failure. We describe the structure, the behavior of the component, and the adjustable parameters. Then, dynamic simulations are discussed. Finally, experimental electrical characteristics of both unidirectional and bidirectional current limiters are presented.

#### II. SiC VJFET CONTROLLED CURRENT LIMITER

#### A. Structure Description

The novelty of this device consists in the design of the gate, which is formed by a buried layer. Fig. 1 shows the cross section of the VJFET and Fig. 2 the main parameters to adjust. This device has a channel divided in two parts: a vertical one and a lateral one. The source is grounded and current flows from drain to source. P-buried layers are designed so that the

|                 | Doping concentration (cm <sup>-3</sup> )    | Thickness<br>(µm) |

|-----------------|---------------------------------------------|-------------------|

| Epitaxial layer | 8×10 <sup>15</sup> cm <sup>-3</sup>         | 18                |

| P-buried layer  | $N_{a1} = 2 \times 10^{18} \text{ cm}^{-3}$ | 2                 |

| Surface channel | $N_{\rm m} = 3 \times 10^{16}  \rm cm^{-3}$ | 0.5               |

TABLE I MAIN PARAMATERS OF THE VJET

VJFET is normally on and presents a low specific resistance. When the drain voltage rises, the current saturates at a voltage corresponding to the pinch-off of both vertical and horizontal channels. In the saturation mode, the device presents an important on resistance ( $R_{\rm ON}$ ), resulting from the serial resistance of both parts of the channel and the drift resistance of the epitaxial layer. Due to self-heating, current decreases as the voltage increases (since electron mobility decreases and induces a current reduction). This effect is amplified while increasing the limiting current density. When a negative bias is applied between gate and source, the p-n junction formed by the p-well and the epitaxial layer is reverse biased leading to current modulation. A tradeoff between specific resistance and blocking capabilities was investigated by simulations. The main parameters are summarized in Table I.

#### B. Static Simulations

In order to optimize the structure layout, a global optimum parameter was defines. It derives from the classical equations of a VJFET [7], which define the relations between pinch-off voltage  $V_p$  (pinch-off current  $I_p$ , transconductance...) and both geometrical and doping parameters as summarized hereafter.

$$\begin{split} V_p &= \frac{q \cdot N_{d2} \cdot w_1^2}{2 \cdot \varepsilon} \\ I_p &= \frac{Z \cdot \mu \cdot q^2 \cdot N_{d2}^2 \cdot w_1^3}{6 \cdot \varepsilon \cdot L_1} \\ g_{ms} &= \frac{Z \cdot \mu}{L_1} \cdot (2 \cdot \varepsilon \cdot q \cdot N_{d2})^{1/2} \cdot \left[ V_p^{1/2} - (V_{di} - V_g)^{1/2} \right] \\ g_o &= \frac{Z \cdot \mu \cdot q \cdot N_{d2} \cdot w_1}{L_1} \\ \text{classical equations of a JFET.} \end{split}$$

These equations were applied to the current-limiter structure with the geometrical parameters presented in Fig. 2. The global optimum parameter defined in (2) allows investigation of a tradeoff in terms of on resistance  $(g_0)$ , current modulation  $(g_{ms})$ , and power losses in the limiting state  $(V_P \times I_P)$

$$Opt(W, Nd, L) = \max \left(\frac{g_0 \cdot g_{ms}}{V_p \cdot I_p}\right)_{(W, Nd, L)}.$$

(2)

It allows us to get a range of parameters to be investigated by fine simulations.

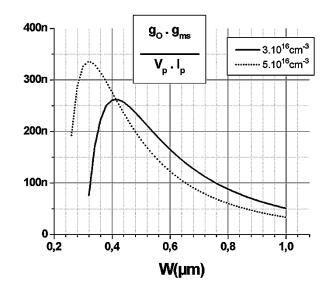

As an example, considering a channel doping concentration of  $3\times 10^{16}$  Atoms  $\times$  cm<sup>-3</sup>, the optimal channel thickness is assumed to be  $\sim 0.4~\mu m$  (Fig. 3). To estimate the peripheral effect on the electrical characteristics, finite-element simu-

Fig. 3. Optimal channel thickness estimation.

TABLE II

MOBILITY MODEL AND PARAMETERS USED FOR SIMULATION

(CAUGHEY-THOMAS MODEL)

$$\mu_{N,p} = \mu_{\min 1} + \frac{\mu_{\max} \left(\frac{T}{300}\right)^{\frac{p}{\xi}} - \mu_{\min 2}}{1 + \left(\frac{N_i}{C_x}\right)^{\kappa}}, \quad N_i = N_A$$

| Param ètres                                                                  | 4 H -S iC |                    |

|------------------------------------------------------------------------------|-----------|--------------------|

|                                                                              | μn        | μр                 |

| μ <sub>m ax</sub> (c m <sup>2</sup> .V <sup>-1</sup> .c m <sup>-1</sup> )    | 870       | 120                |

| μ <sub>m in 1</sub> (c m <sup>2</sup> . V <sup>-1</sup> .c m <sup>-1</sup> ) | 0         | 0                  |

| μ <sub>m in 2</sub> (c m <sup>2</sup> . V <sup>-1</sup> .c m <sup>-1</sup> ) | 0         | 0                  |

| Cr (cm <sup>-3</sup> )                                                       | 2.1017    | 5.10 <sup>19</sup> |

| α                                                                            | 0,55      | 0,3                |

| ξ                                                                            | 2         | 2                  |

lations (using ISE-TCAD [8]) are useful. In that case, different models are used, taking into account physical properties of silicon carbide. As the dissipated power can reach high values, the mobility temperature dependence is taken into account [using the Caughey–Thomas model (see Table II)]. Most of parameters were given by Ruff [9] or are extracted from experimental results [10].

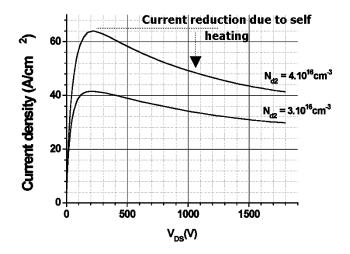

The effect on electrical characteristics of each parameter presented in Fig. 2 was estimated by finite-elements simulation. As an example, channel doping level  $N_{d2}$  has been investigated. Current density dependence and self-heating effect are presented in Fig. 4 (both increasing while rising doping concentration). The simulated specific resistance  $R_d$  in the linear mode is in the range of 150 m $\Omega \cdot {\rm cm}^2$  at  $V_{DS}=1$  V.

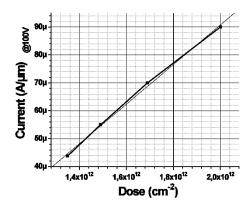

The saturation current dependence on channel implanted dose D ( $D = N_{d2} \times w_1$ ) was checked by means of finite-element simulations. This lets us choose a set of fabrication parameters considering, for example, the desired current saturation value (Fig. 5). Additional parameters such as the breakdown voltage have been taken into account for the design of the final demonstrator.

Fig. 4. Influence of the surface channel doping on the current density and self-heating effect.

Fig. 5. Saturation current dependence versus channel dopant dose.

Fig. 6. Electrical circuit for switching.

#### C. Dynamic Simulations

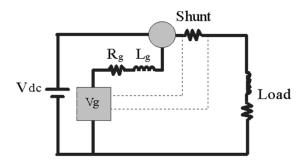

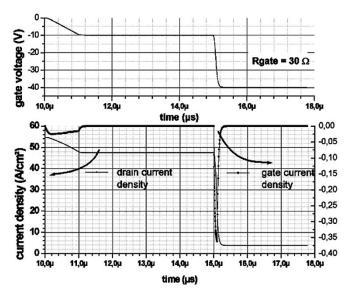

Mixed-mode simulations using a Spice circuit and finite elements for the VJFET were done to evaluate switching performance of the circuit described in Fig. 6. Parasitic wiring inductance has been taken into account. Using a shunt for current sensing and an appropriate electronic command block allows us to modulate the VJFET gate voltage in this way to reduce the current in the circuit. The simulated electrical circuit is presented in Fig. 7. Switching simulations were performed with a two-step gate bias.

Fig. 7. Current reduction and switch-off waveform.

Fig. 8. Switch-off characteristics details for two  $R_{\rm gate}$  values.

TABLE III COMMUTATION LOSSES AS A FUNCTION OF  $R_{\cal G}$

| $\mathbf{R}_{\mathtt{G}}$ | I <sub>Gmax (A/cm²)</sub> | $P_{\rm off(W/cm^2)}$ |

|---------------------------|---------------------------|-----------------------|

| 20                        | - 0.41                    | 0.146                 |

| 30                        | -0.36                     | 0.133                 |

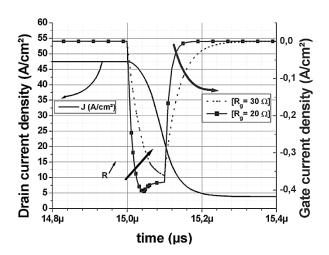

The first gate bias step underlines the current reduction ability ( $V_{GS}=-10~{\rm V}$  at  $t=10~{\mu}{\rm s}$ ). Then, applying a gate bias  $V_{GS}=-40~{\rm V}$  at  $t=15~{\mu}{\rm s}$  allows us to shut down the current in the circuit as presented in Fig. 7. The switch-off gate current is dependent on the gate resistance value and voltage rise time. Adjusting the resistance value allows us to control the gate switch-off power losses, without an effect on drain current value and switch-off time, as shown in Fig. 8. Consequently, gate power losses and peak current are reduced by around 10% as shown in Table III.

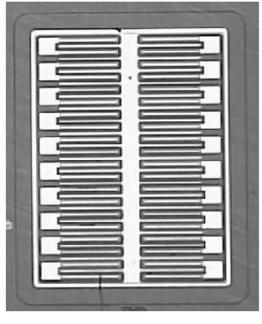

Fig. 9. (a) Interdigitated structure cross section. (b) Fabricated interdigitated VJFET ( $1.4 \times 1.8$  mm).

(b)

#### III. DEVICE FABRICATION AND CHARACTERIZATION

#### A. Device Fabrication

Various device layouts have been implemented (such as an interdigitated device presented in Fig. 9), to validate the process technology, parameters adjustments, and the device performance. Key points of the device fabrication are high energy implantation, annealing activation, and ohmic contact formation. State-of-the-art values [2] of ohmic contact were measured on the first batch of VJFETs fabricated ( $\approx 10~\mu\Omega \cdot \text{cm}^2$ ).

#### B. Static's Measurements

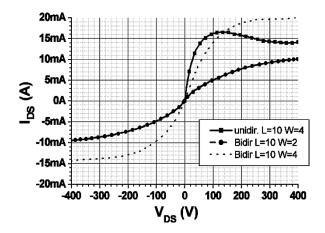

Fig. 10 presents the measured electrical characteristics for a unidirectional VJFET. Unidirectional measurements were done by applying 0.5-s pulse ( $f=2~{\rm Hz}$ ), with drain biased up to 400 V. The specific on-resistance varies from 176 up to 237 m $\Omega$ ·cm<sup>2</sup> for the matrix structures. The maximum pulsed power density dissipated in the limiting mode is 160 kW/cm<sup>2</sup>. Limiting

Fig. 10. Electrical measured characteristics for unidirectional and bidirectional limiters.

Fig. 11. High breakdown voltage measurement of a unidirectional current limiter (sinusoidal waveform, 50 Hz).

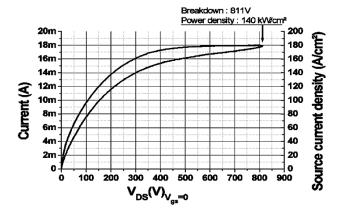

capabilities have also been measured for a bidirectional device made of two unidirectional devices connected head to tail (i.e., drain connected). This one exhibits a specific on-resistance of 700 m $\Omega \cdot \text{cm}^2$ . The highest breakdown in the "current-limiting state" was measured to be  ${\sim}810$  V (Fig. 11), corresponding to a high pulsed power density of 140 kW/cm $^2$ .

#### C. Dynamic's Measurements

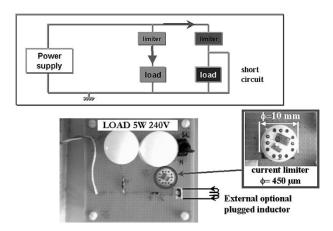

The response time of the current limiter was checked by means of short-circuit measurements, using the following electrical circuit setup (Fig. 12). The power supply used was a 240-V 50-Hz sinusoidal source. Load was 5-W/240-V bulbs. Using the mechanical switch, a short circuit was performed on one of the lights serially plugged with a current limiter. Both VJFET current and voltage evolution were measured in the case of short circuit.

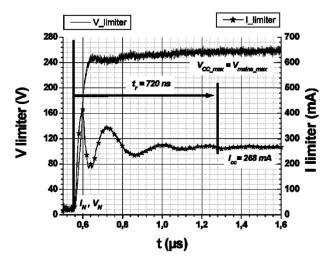

The gate of the VJFET was not connected in order to show the self-protection capability of the device. Without any external electronic system, the VJFET is able to protect against short circuit as shown in Fig. 13. A response time of  $t_r=0.7~\mu \mathrm{s}$  was measured, with a limited current  $I_{cc}=270~\mathrm{mA}$  after stabilization.

Considering the impedance of the electrical circuit, without serial protection the fault current rise up would have been 43 A/ $\mu$ s. This measurement clearly demonstrates the efficiency

Fig. 12. Electrical circuit used to performed short-circuit measurements.

Fig. 13. VJFET response to a short circuit (measurements).

of serial protection using a VJFET as a current limiter. The short circuit was maintained during more that 5 min, without any failure of the device, which was able to sustain short-circuit power of 70 W (an equivalent power density of 75 kW/cm<sup>2</sup>). Temperature increase in that case is lower than 70 °C.

#### IV. CONCLUSION

This paper has demonstrated the feasibility of an SiC current limiter with high power density. The design was made using the ISE software with respect to the technological limitations. The first demonstrator exhibits optimistic characteristics. Bidirectional components were measured by associating two devices head to tail. Moreover, the SiC VJFET manufacturing process is compatible with the SiC MESFET manufacturing process [11]. This allows us to foresee the integration of a self-controlled current limiter by an appropriate association of FET transistors.

A short-circuit demonstration was done using 5-W/240-V bulbs as a load. A very low response time to short circuit has been measured (as low as 1  $\mu$ s). This device could be used in applications such as current limitation in the case of a short

circuit of an electrical system. Using such a component could allow an increase of the current ratings of classical mechanical devices. The next challenge consists of both current sensing and current modulation in the limiting state using the gate electrode so as to reduce short-circuit power losses.

#### ACKNOWLEDGMENT

The realization of this device was achieved at the Centro Nacional de Microelectronica, Barcelona, Spain.

#### REFERENCES

- [1] Y. Sugawara, "12 19 kV 4H-SiC pin diodes with low power loss," in *Proc. ISPSD'01*, Osaka, Japan, 2001, pp. 27–30.

- [2] H. Matsunami, "Progress in wind bandgap seminconductor SiC for power devices," in *Proc. 12th Int. Symp. Power Semiconductor Devices* and ICs, 2000, pp. 3–9.

- [3] S. M. Sze, Physics of Semiconductor Devices, 2nd ed. New York: Wiley, 1981, p. 868.

- [4] SEMITEC I.E. Corp.. (2003, Mar.) CRD: Current regulative diode. [Online] Available: http://www.semitec.co.jp/english/indexe.htm

- [5] Siemens Corp., "Current limiter circuit," World Patent W09727657, July 30, 1997.

- [6] F. Nallet and A. Senes *et al.*, "Electrical and electrothermal 2D simulation of a 4H-SiC high voltage current limiting device for serial protection application," in *Proc. ISPSD'00*, Toulouse, France, May 22–25, 2000, pp. 287–290.

- [7] H. Mathieu, *Physique des Semiconducteurs et des Composants Électronique*, 4th ed. Paris, France: Editions Masson, 1998, p. 709.

- [8] Integrated System Engineering, ISE TCAD, AG, Zurich, Switzerland,

- [9] M. Ruff and H. Mitlehner et al., "SiC devices: physics and numerical simulation," *IEEE Trans. Electron Devices*, vol. 41, pp. 1040–1054, June 1994

- [10] M. Lades, "Modeling and simulation of wide bandgap semiconductor devices: 4H/6H-SiC," Thesis, Technischen Univ. München, Munich, Germany, May 15, 2000.

- [11] D. Tournier et al., "Compatibility of VJFET technology to MESFET fabrication and its interest to system integration: fabrication of 6H and 4H-SiC 110V lateral MESFET," Mater. Sci. Forum, vol. 389, pp. 1403–1407, 2002.

**Dominique Tournier** (S'02) was born in Bourgoin-Jallieu, France, in 1973. He received the Ph.D. degree from the Institut National des Sciences Appliquées (INSA), Lyon, France, in 2003.

In 2003, he joined the Centro Nacional de Microelectronica, Bellaterra, Spain. His interests are silicon carbide device design and fabrication for high-power electronics applications.

**Philippe Godigon** received the Ph.D. degree in electrical engineering from the Institut National des Sciences Appliquées (INSA), Lyon, France, in 1993.

Since 1990, he has been with the Power Device and System Group, Centro Nacional de Microelectronica, Bellaterra, Spain, working on Si IGBT/VDMOS and SiC devices design and technologies. His expertise covers device technological process development and mask design as well as electrical characterization. He has authored more than 70 publications and conference papers on SiCs.

**Joseph Montserrat** received the B.S. and Ph.D. degrees in physics from the University of Barcelona, Barcelona, Spain, in 1985 and 1991, respectively.

In 1987, he joined the Centro Nacional de Microelectronica, Bellaterra, Spain, where he works as a Process Engineer in the Clean Room Group. He is responsible for the ion implantation and metallization areas. His main research interest is silicon technology for the manufacture of CMOS integrated circuits, power devices, and microelectronic sensors.

power electronics.

**Dominique Planson** was born in Paris, France, in 1965. He received the electrical engineering and Ph.D. degrees from the Institut National des Sciences Appliquées (INSA), Lyon, France, in 1991 and 1994, respectively.

In 1993, he joined INSA as an Associate Professor, where, since 1994, he has been an Assistant Professor. He is with the Centre de Génie Electrique de Lyon (CEGELY)-INSA, Villeurbanne, France, where his research is focused on silicon carbide power device design and applications of SiCs to

Christophe Raynaud was born in Vienne, France, in 1969. He received the engineering and Ph.D. degrees from the Institut National des Sciences Appliquées (INSA), Lyon, France, in 1992 and 1995, respectively. His Ph.D. studies were devoted to characterizations of SiC bipolar and Schottky diodes and MOS devices in the Materials Physics Laboratory.

He also worked for three years on submicrometer silicon-based MOSFETs and EEPROMs, in particular, in charge pumping measurements, in modeling

quantum effects in ultrathin oxide MOS, and studying EEPROM aging, in collaboration with ST Microelectronics. Since 1999, he has been Assistant Professor at INSA, where his research activities at the Centre de Génie Electrique de Lyon (CEGELY)-INSA, Villeurbanne, France, are focused on high-voltage silicon-carbide-based devices in the area of failure analysis.

**Jean Pierre Chante** was born in Lyon, France, in 1942. He received the "Doctorat d'Etat" degree from the University of Lyon, Lyon, France, in 1981.

From 1980 to 1986, he managed a research team in the field of power semiconductor devices at the Ecole Centrale de Lyon. Since 1986, he has been a Professor of Electronic Components and Applied Electronics at the Institut National des Sciences Appliquées (INSA), where he is the Head of the Power Devices and Applications Team which is part of the Centre de Génie Electrique de Lyon

(CEGELY)-INSA, Villeurbanne, France. He is also in charge of the Centre Inter-Universitaire de Microélectronique de la Région de Lyon, which is a regional research center in the microelectronics field. His interests are in high-temperature electronics, SiC-based components, advanced power devices, and CAD tools for power electronics.

**Jean-François de Palma** was born in Torino, Italy, in 1963. He received the Ph.D. degree from the Institut National des Sciences Appliquées (INSA), Villeurbanne, France, in 1992.

In 1992, he joined Ferraz, St Bonnet de Mure, France, where, as a member of the R&D group, he worked on semiconductor market trend and performance analyses, TVSS components, pyrotechnic devices, and fuse development. In 1995, he moved to Ferraz Corporation, NJ, as Engineering Manager. From 1995 to 1998, he helped U.S.

customers select fuses for their applications. In 1998, he returned to Ferraz as Manager of the Fuse Development Group, working mainly on fuses for IGBT case rupturing applications, high-voltage high-current fuses, and new technology for square-body fuses. In 1999 Ferraz, France, and Gould Shawmut merged, becoming Ferraz Shawmut. In 2000, he joined Ferraz Shawmut, Inc., Newburyport, MA, as the North American R&D Director.

Franck Sarrus was born in Guéret, France, in 1965. He received the Dipl.Eng. degree in electrical engineering from the University of Clermont Ferrand, Clermont Ferrand, France, in 1992, and the Ph.D. degree from the University of Lyon, Lyon, France, in 1995.

In 1995, he jointed Ferraz Shawmut, St Bonnet de Mure, France, as an Electrical Engineer on the research team. Since 2000, he has been an R&D Manager.